一,相控阵原理

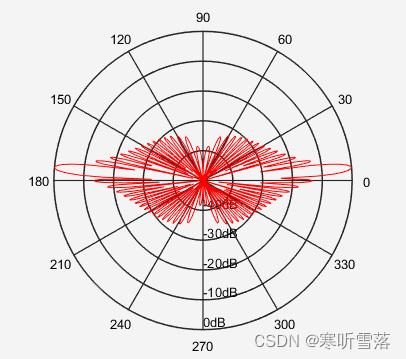

相控阵即相位补偿(或延时补偿)基阵,它既可用以接收,也可用以发射。其工作原理是对按一定规律排列的基阵阵元的信号均加以适当的移相(或延时)以获得阵波束的偏转,在不同方位上同时进行相位(或延时)补偿,即可获得多波束。其优点是,不必用机械转动基阵就可在所要观察的空间范围内实现波束的电扫描,非常方便灵活。同时,基阵的尺寸便可做得大一些以提高空间增益。

二,相控阵的优势和劣势

雷达扫描目标的方式分为两种。 第一种:雷达在搜索目标时,需要不断改变波束的方向。改变波束方向的传统方法是转动雷达天线,使波束扫过一定的空域、地面或海面,这种方式称为机械扫描。 第二种:雷达天线阵面上排列着成百上千个阵元,每个阵元都能发射和接收雷达脉冲。 通过计算机控制每个单元脉冲的相位和振幅,可以确定雷达整体波束的形状和方向,以这样方式进行的扫描,称为电扫描。接收单元将收到的雷达回波信号送入主机进行计算,完成雷达的搜索、跟踪和测量任务,这就是相控阵技术。

本文介绍了相控阵的基本原理,包括波束切换速度快、无伺服机构等优势,以及Phasor Solution公司的平板天线在低轨和高轨通信中的应用。同时,讨论了超材料波束形成技术和光学波束形成技术,展示了降低天线成本和功耗的可能性。最后,概述了相控阵的发展历程和未来趋势。

本文介绍了相控阵的基本原理,包括波束切换速度快、无伺服机构等优势,以及Phasor Solution公司的平板天线在低轨和高轨通信中的应用。同时,讨论了超材料波束形成技术和光学波束形成技术,展示了降低天线成本和功耗的可能性。最后,概述了相控阵的发展历程和未来趋势。

订阅专栏 解锁全文

订阅专栏 解锁全文

1922

1922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?