相关文章:

(1)千兆以太网网络层 ARP 协议的原理与 FPGA 实现

(2)千兆以太网硬件设计及链路层 MAC 协议格式

(3)CRC校验原理及实现

(4)RGMII 与 GMII 转换电路设计)

(5)千兆以太网网络层 IP 协议介绍与 IP 校 验和算法实现

(6)千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP发送)

(7)千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP接收)

(8)千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP回环)

(9)以太网初始化设计(MDIO 控制器)

(10)添加基于 OV2640 的以太网 RGMII 图像传输系统设计

文章目录

前言

经过前面章节的理论讲解和模块设计,相信大家已经对以太网传输以及如何实现以太网通信有了一定的了解。为了验证前面章节的内容,我们将进行以太网回环案例。通过判断回环数据是否一致,对前面章节内容和设计的模块进行验证。

提示:任何文章不要过度深思!万事万物都经不起审视,因为世上没有同样的成长环境,也没有同样的认知水平,更「没有适用于所有人的解决方案」 ;不要急着评判文章列出的观点,只需代入其中,适度审视一番自己即可,能「跳脱出来从外人的角度看看现在的自己处在什么样的阶段」才不为俗人 。怎么想、怎么做,全在乎自己「不断实践中寻找适合自己的大道」

心得体会

(1)UDP发送数据,无论是MAC地址,还是IP地址,或者UDP端口,其源端口都为开发板;

(2)在发送数据时不关心源端口(开发板)的MAC地址,还是IP地址,或者UDP端口,只关心目的地址,验证时一定要弄清目的地址的MAC和P地址及UDP端口;

(3)UDP接收数据,无论是MAC地址,还是IP地址,或者UDP端口,其源端口都为计算机;

(4)在接收数据时不关心源端口(计算机)的MAC地址,还是IP地址,或者UDP端口,只关心目的地址,验证时一定要弄清目的地址(开发板)的MAC和IP地址,这里与UDP发送中目的MAC、IP(计算机)是相反的,此处需要注意;

(5)本实验针对千兆网,注意查看电脑是否支持。

————————————————

一、UDP GMII 回环测试工程介绍

为了完成基本的以太网回环测试,我们提供了一个基于 FPGA 的以太网回环测试程序。该程序使用 UDP 协议,接收 PC 发送的 UDP 数据包,提取出其中的数据部分并使用 UDP 协议发回给PC。

例程调用了前面小节中我们设计的 UDP 发送模块以及 UDP 接收模块,UDP 接收模块接收到上位机发来的 UDP 数据包,通过解析目标 MAC_address 来确定是否是发给 FPGA 的数据包。如果是的话,FPGA 会把数据包中的数据以及MAC地址, IP 地址,UDP端口,数据长度等信息输出,再通过发送程序将数据包发送回指定上位机。

千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP接收)

千兆以太网传输层 UDP 协议原理与 FPGA 实现(UDP发送)

二、UDP GMII 回环测试工程顶层设计

`timescale 1ns / 1ps

//

// Create Date: 2023/09/20 15:54:40

// Module Name: UDP_RX_TX_ip

// Name: 小王在努力...

// Revision: Vivado 2018.3

// Revision 0.01 - File Created

//

module UDP_RX_TX_ip(

input CLK125M,

input reset_n,

input GMII_ER,

input GMII_DV,

input [7:0]GMII_TXD,

output GMII_TX_ER,

output GMII_TX_EN,

output GMII_TX_CLK,

output [7:0]GMII_TX_TXD,

output eth_reset_n,

output reg [1:0]led

);

wire tx_done;

wire [15:0]udp_data_length;

wire [15:0]udp_src;

wire [15:0]udp_dest;

wire [31:0]src_ip;

wire [31:0]dst_ip;

wire [47:0]dst_mac;

wire [47:0]src_mac;

wire GMII_RX_EN;

wire [7:0]GMII_RXD;

wire GMII_RX_DONE;

wire clk125m_o;

//fifo

wire [11:0]wrusedw;

wire wr_rst_busy;

reg [7:0]wrdata;

reg wrreq;

assign eth_reset_n = reset_n;

//------------------------------------------------------------------------------

//此处设计两个led灯,当数据接收完成后led1闪烁,当数据发送完成是led0闪烁,以此判断数据是否接收与发送

reg [27:0]cnt_time_rx,cnt_time_tx;

parameter time_500_ms = 28'd62499999; //62499999

//计数0.5s时钟

always @ (posedge clk125m_o or negedge reset_n)

if(!reset_n)

cnt_time_rx <= 0;

else if(GMII_RX_DONE)

cnt_time_rx <= 0;

else if(cnt_time_rx >= time_500_ms)

cnt_time_rx <= cnt_time_rx ;

else

cnt_time_rx <= cnt_time_rx + 1;

//利用cnt_time产生led信号当接收完时led闪烁0.5s

always @ (posedge clk125m_o or negedge reset_n)

if(!reset_n)

led[1] <= 0;

else if(GMII_RX_DONE )

led[1] <= 1;

else if(cnt_time_rx >= time_500_ms)

led[1] <= 0;

else

led[1] <= led[1];

always @ (posedge clk125m_o or negedge reset_n)

if(!reset_n)

cnt_time_tx <= 0;

else if(tx_done)

cnt_time_tx <= 0;

else if(cnt_time_tx >= time_500_ms)

cnt_time_tx <= cnt_time_tx;

else

cnt_time_tx <= cnt_time_tx + 1;

//利用cnt_time产生led信号当发生完时led闪烁0.5s

always @ (posedge clk125m_o or negedge reset_n)

if(!reset_n)

led[0] <= 0;

else if(tx_done )

led[0] <= 1;

else if(cnt_time_tx >= time_500_ms)

led[0] <= 0;

else

led[0] <= led[0];

//------------------------------------------------------------------------------

UDP_RX_ip UDP_RX_ip(

. clk125m (CLK125M) ,

. reset_n (reset_n) ,

. GMII_ER (GMII_ER) ,

. GMII_DV (GMII_DV) ,

. GMII_TXD (GMII_TXD) ,

//udp层

.udp_data_length(udp_data_length),

.udp_src (udp_src ),

.udp_dest (udp_dest ),

//ip层

.src_ip (src_ip ),

.dst_ip (dst_ip ),

//mac层

.dst_mac (dst_mac ),

.src_mac (src_mac ),

//RGMII_RX输出

.GMII_RX_EN (GMII_RX_EN ),

.GMII_RXD (GMII_RXD ),

.GMII_RX_DONE (GMII_RX_DONE ),

.clk125m_o (clk125m_o)

);

//当接收模块接收到数据时就开始往发送模块的fifo中寄存

always @ (posedge clk125m_o or negedge reset_n)

if(!reset_n)

begin

wrreq <= 0;

wrdata <= 0;

end

else if(GMII_RX_EN)

begin

wrreq <= 1;

wrdata<=GMII_RXD;

end

else

begin

wrreq <= 0;

wrdata <= 0;

end

UDP_TX_ip #(

//ip层参数

. ip_ver (4'd4), //ipv4

. ip_hdr_len (4'd5), //ip首部长度

. ip_ttl (8'd64), //生存周期

. ip_protocol (8'd17), //UDP协议

//mac层

. eth_type (16'h0800) //ip协议

)UDP_TX_ip

(

. clk_125m(clk125m_o),

. reset_n (reset_n),

//udp层

. udp_data_length(udp_data_length), //23

. udp_src (udp_dest),

. udp_dest(udp_src),

//ip层

. ip_src(dst_ip),

. ip_dst(src_ip),

//mac层

. dst_mac(src_mac),

. src_mac(dst_mac),

//fifo

. wrclk(clk125m_o),

. rst(~reset_n),

. wrdata(wrdata),

. wrreq(wrreq),

. wrusedw(wrusedw),

. wr_rst_busy(wr_rst_busy),

. tx_done(tx_done),

//GMII协议

. GMII_TX_ER (GMII_TX_ER),

. GMII_TX_EN (GMII_TX_EN),

. GMII_TX_CLK(GMII_TX_CLK),

. GMII_TX_TXD(GMII_TX_TXD)

);

endmodule

三、UDP GMII 回环测试工程仿真设计

这里使用UDP发送模块(UDP_SEND_DATD)进行模拟上位机数据发送(此处的目的地址均为开发板),然后将数据传输到UDP接收模块解析出数据,送往UDP发送模块输出(此处的目的地址为PC机)。

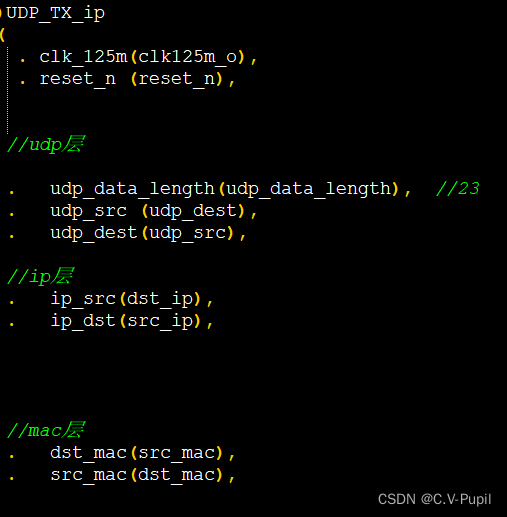

【注意:】UDP接收端解析出的目的地址为开发板,而UDP发送端目的地址为PC,二者需要在发送端对调。

`timescale 1ns / 1ps

//

// Create Date: 2023/09/20 15:54:40

// Module Name: UDP_RX_TX_ip

// Name: 小王在努力...

// Revision: Vivado 2018.3

// Revision 0.01 - File Created

//

module UDP_RX_TX_ip_tb( );

reg clk50m;

wire locked;

reg reset_n;

wire [1:0]led;

wire TX_ER;

wire TX_EN;

wire TX_CLK;

wire [7:0]TXD;

wire eth_reset_n ;

wire GMII_TX_ER;

wire GMII_TX_EN;

wire GMII_TX_CLK;

wire [7:0]GMII_TX_TXD;

initial clk50m = 1;

always #10 clk50m = ~clk50m;

initial begin

reset_n = 0;

#201;

reset_n = 1;

#10000000;

end

UDP_SEND_DATD UDP_SEND_DATD(

. clk50m (clk50m),

. reset_n (reset_n),

. locked (locked),

. GMII_TX_ER (TX_ER),

. GMII_TX_EN (TX_EN),

. GMII_TX_CLK(TX_CLK),

. GMII_TX_TXD(TXD),

. eth_reset_n( )

);

UDP_RX_TX_ip UDP_RX_TX_ip(

.CLK125M(TX_CLK),

.reset_n(reset_n),

.GMII_ER(TX_ER),

.GMII_DV(TX_EN),

.GMII_TXD(TXD),

.led(led),

.GMII_TX_ER(GMII_TX_ER),

.GMII_TX_EN(GMII_TX_EN),

.GMII_TX_CLK(GMII_TX_CLK),

.GMII_TX_TXD(GMII_TX_TXD),

.eth_reset_n(eth_reset_n)

);

endmodule

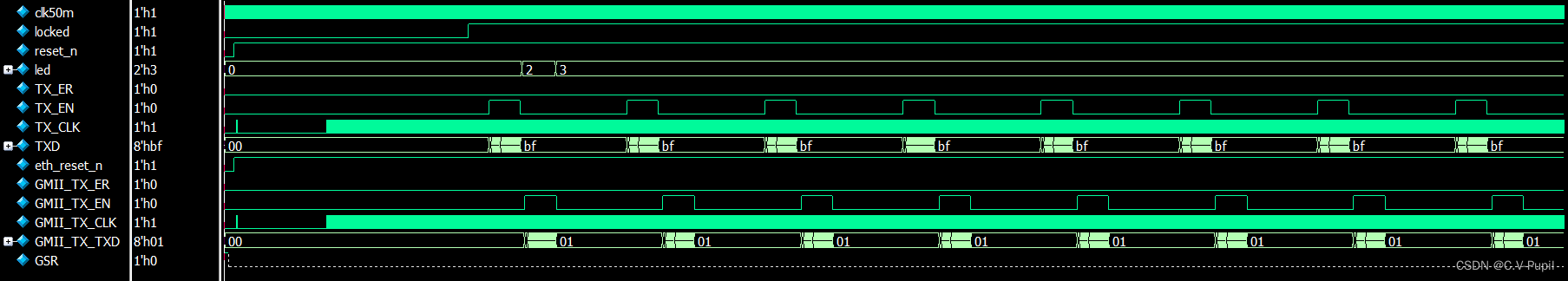

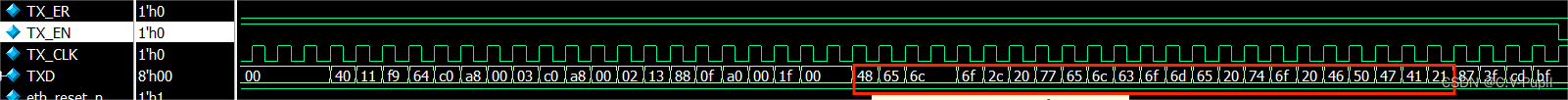

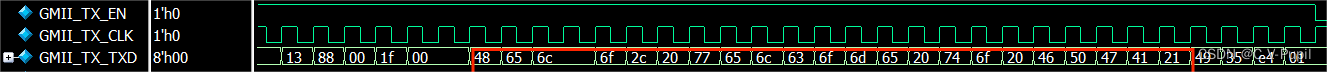

四、UDP GMII 回环测试工程仿真波形

局部展示:

此图为UDP_SEND_DATD模块模拟PC发送的数据,理论上除目的地址和源地址相反,校验值不同外(因目的地址和源地址不同),经过UDP接收传输到UDP发送端,数据应完全相同。

可以看出两图传输的有效数据完全相同。至此仿真验证完成。

五、UDP GMII 回环测试工程上板演示

【说明:】如果使用的是RTL8211EG-VB芯片,在添加管脚约束时,添加一句

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullnone [current_design]

防止自动协商时协商为百兆或十兆。具体原因参考RTL8211EG-VB芯片自动协商时协商为百兆或十兆的原因

RTL8211EG-VB芯片自动协商时协商为百兆或十兆的原因

————————————————

用户实验时,IPV4地址与mac地址一定与自己电脑相对应

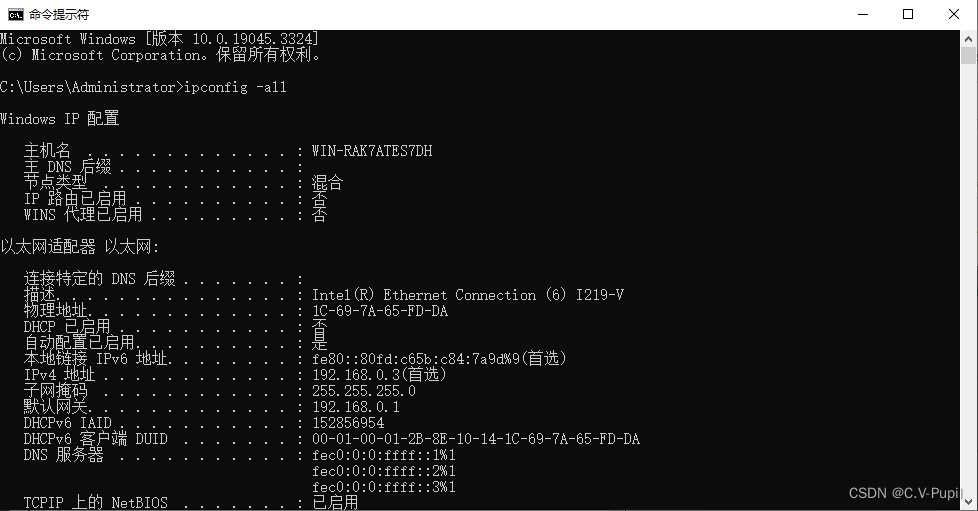

(1)在 DOS 命令窗口,用 ipconfig –all 命令看一下,可以看到PC的MAC地址与IP地址,需与 FPGA 网口相连接的电脑网口的配置保持一致。

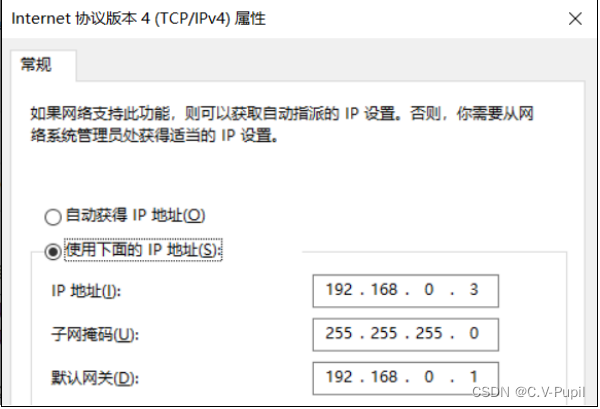

建议将自己的电脑 IP 地址设置为程序中询问的 192.168.0.3。

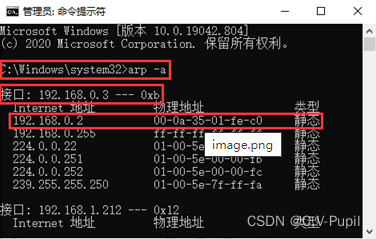

由于本测试工程不支持ARP协议,因此只能通过静态绑定的方式来强制将开发板的IP地址和MAC地址关联在一起。这样,当 PC发送给192.168.0.2的数据包的时候,目标MAC地址自动为开发板的MAC地址。操作时先以管理员身份运行cmd.exe程序(该文件在C:\Windows\System32路径下),也就是我们常说的命令行窗口。由于有用户反应在使用时无法成功绑定arp,经过分析就是操作权限不够,所以这里强调要以管理员身份运行cmd.exe。然后在窗口中输入下述命令:

arp -s 192.168.0.2 00-0a-35-01-fe-c0

绑定后我们可以用arp -a命令来查看PC上绑定的结果,如下图所示:

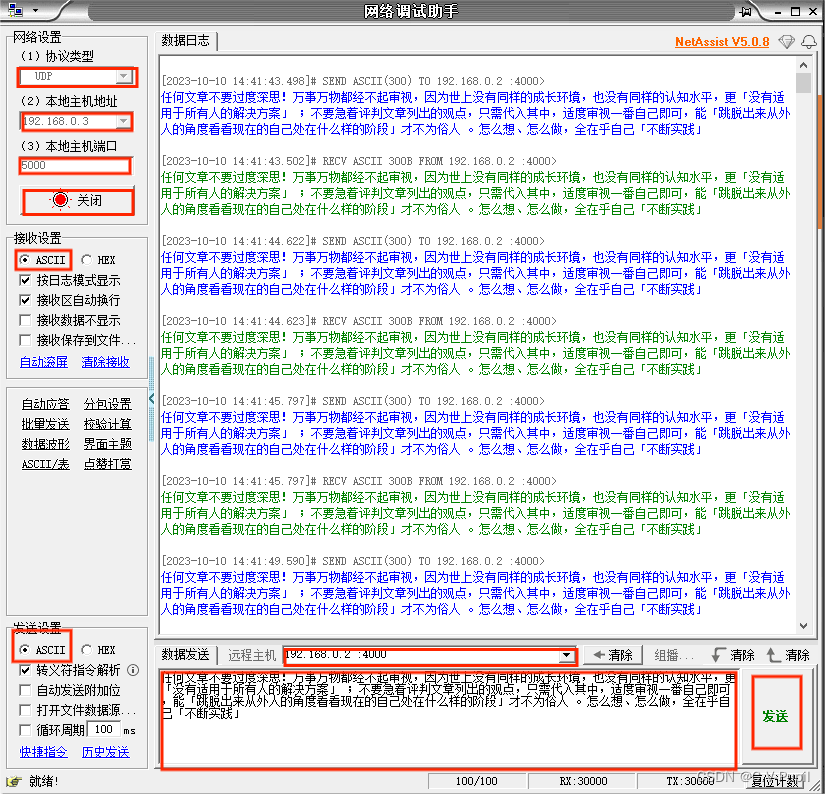

进行管脚约束,下载bit文件,确认无误后,打开网络调试助手,对应设置:

可以看到网络调试助手收发100次,数据无误。

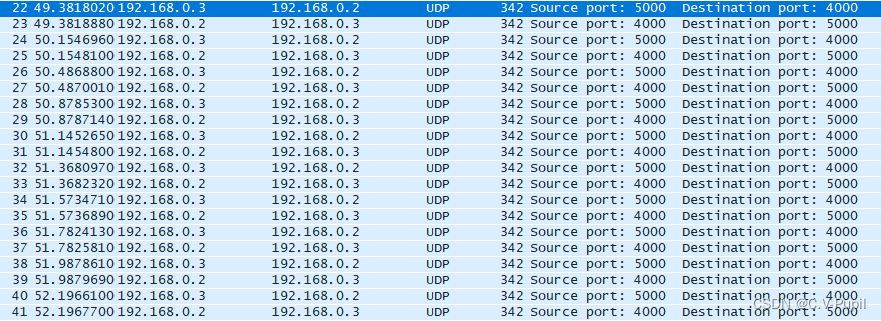

打开wireshark抓取数据:

选择以太网,点击开始,并点击网络调试助手发送按钮:

可以抓到收发数据,至此验证完成。

【附件:】链接:https://pan.baidu.com/s/1QpRBT29i80VPxecbEqaQcA?pwd=jpy6

提取码:jpy6

9053

9053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?