开发板环境:vivado2017.4

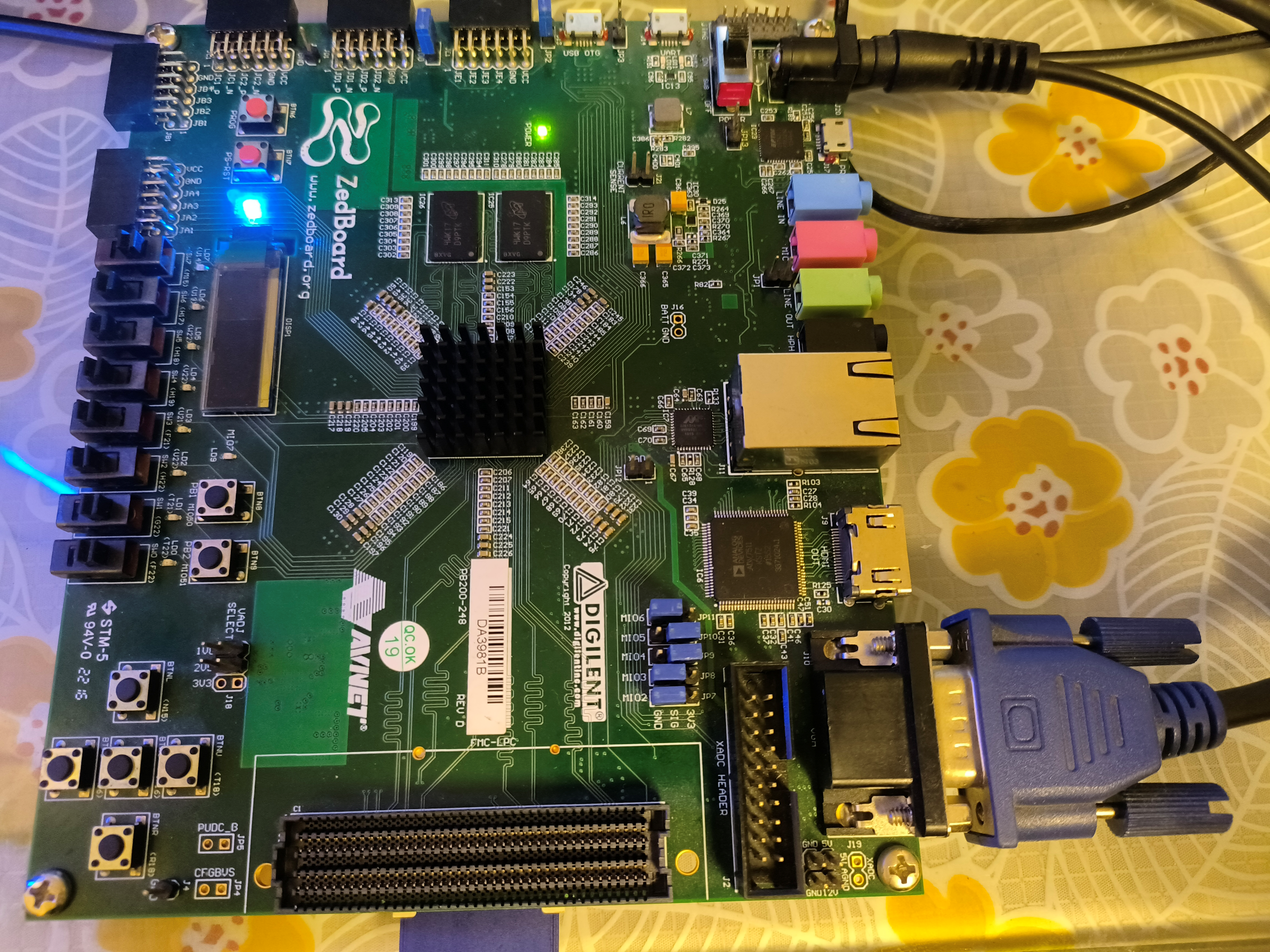

开发板:Zedboard 芯片型号:xc7z020clg484-1

VGA显示硬件

新建工程vivado工程(如果不会可以参考前面的hello_world这章)

新建Block工作区

调用zynq核

双击ZYNQ核,选择Presets-->Apply Configuration导入tcl配置文件

选择vdma_vga.tcl并点击OK,导入配置文件

配置完成后如下图所示

需调用的所有IP核

需调用的所有IP核

VDMA设置

设置VGA时钟和VTC,分辨率设置为1920*1080,频率为148.5M

设置时钟

设置V_TC分辨率

设置Video out

顶层文件

//Copyright 1986-2017 Xilinx, Inc. All Rights Reserved.

//--------------------------------------------------------------------------------

//Tool Version: Vivado v.2017.4 (win64) Build 2086221 Fri Dec 15 20:55:39 MST 2017

//Date : Sun Sep 18 22:55:19 2022

//Host : PS2022UUIQUORW running 64-bit major release (build 9200)

//Command : generate_target design_1_wrapper.bd

//Design : design_1_wrapper

//Purpose : IP block netlist

//--------------------------------------------------------------------------------

`timescale 1 ps / 1 ps

module design_1_wrapper

(DDR_addr,

DDR_ba,

DDR_cas_n,

DDR_ck_n,

DDR_ck_p,

DDR_cke,

DDR_cs_n,

DDR_dm,

DDR_dq,

DDR_dqs_n,

DDR_dqs_p,

DDR_odt,

DDR_ras_n,

DDR_reset_n,

DDR_we_n,

FIXED_IO_ddr_vrn,

FIXED_IO_ddr_vrp,

FIXED_IO_mio,

FIXED_IO_ps_clk,

FIXED_IO_ps_porb,

FIXED_IO_ps_srstb,

vga_r,

vga_g,

vga_b,

vga_hs,

vga_vs);

inout [14:0]DDR_addr;

inout [2:0]DDR_ba;

inout DDR_cas_n;

inout DDR_ck_n;

inout DDR_ck_p;

inout DDR_cke;

inout DDR_cs_n;

inout [3:0]DDR_dm;

inout [31:0]DDR_dq;

inout [3:0]DDR_dqs_n;

inout [3:0]DDR_dqs_p;

inout DDR_odt;

inout DDR_ras_n;

inout DDR_reset_n;

inout DDR_we_n;

inout FIXED_IO_ddr_vrn;

inout FIXED_IO_ddr_vrp;

inout [53:0]FIXED_IO_mio;

inout FIXED_IO_ps_clk;

inout FIXED_IO_ps_porb;

inout FIXED_IO_ps_srstb;

output vga_hs;

output vga_vs;

output [3:0] vga_r;

output [3:0] vga_g;

output [3:0] vga_b;

wire [14:0]DDR_addr;

wire [2:0]DDR_ba;

wire DDR_cas_n;

wire DDR_ck_n;

wire DDR_ck_p;

wire DDR_cke;

wire DDR_cs_n;

wire [3:0]DDR_dm;

wire [31:0]DDR_dq;

wire [3:0]DDR_dqs_n;

wire [3:0]DDR_dqs_p;

wire DDR_odt;

wire DDR_ras_n;

wire DDR_reset_n;

wire DDR_we_n;

wire FIXED_IO_ddr_vrn;

wire FIXED_IO_ddr_vrp;

wire [53:0]FIXED_IO_mio;

wire FIXED_IO_ps_clk;

wire FIXED_IO_ps_porb;

wire FIXED_IO_ps_srstb;

wire vid_active_video;

wire vid_clk;

wire [23:0]vid_data;

wire vid_hsync;

wire vid_vsync;

assign vga_hs = ~vid_hsync;

assign vga_vs = ~vid_vsync;

assign vga_r = (vid_active_video)? vid_data[23:20]: 4'd0;

assign vga_g = (vid_active_video)? vid_data[15:12]: 4'd0;

assign vga_b = (vid_active_video)? vid_data[7:4] : 4'd0;

design_1 design_1_i

(.DDR_addr(DDR_addr),

.DDR_ba(DDR_ba),

.DDR_cas_n(DDR_cas_n),

.DDR_ck_n(DDR_ck_n),

.DDR_ck_p(DDR_ck_p),

.DDR_cke(DDR_cke),

.DDR_cs_n(DDR_cs_n),

.DDR_dm(DDR_dm),

.DDR_dq(DDR_dq),

.DDR_dqs_n(DDR_dqs_n),

.DDR_dqs_p(DDR_dqs_p),

.DDR_odt(DDR_odt),

.DDR_ras_n(DDR_ras_n),

.DDR_reset_n(DDR_reset_n),

.DDR_we_n(DDR_we_n),

.FIXED_IO_ddr_vrn(FIXED_IO_ddr_vrn),

.FIXED_IO_ddr_vrp(FIXED_IO_ddr_vrp),

.FIXED_IO_mio(FIXED_IO_mio),

.FIXED_IO_ps_clk(FIXED_IO_ps_clk),

.FIXED_IO_ps_porb(FIXED_IO_ps_porb),

.FIXED_IO_ps_srstb(FIXED_IO_ps_srstb),

.vid_active_video(vid_active_video),

.vid_clk(vid_clk),

.vid_data(vid_data),

.vid_hsync(vid_hsync),

.vid_vsync(vid_vsync));

endmodule

设置管脚约束

set_property PACKAGE_PIN V20 [get_ports {vga_r[0]}]

set_property PACKAGE_PIN U20 [get_ports {vga_r[1]}]

set_property PACKAGE_PIN V19 [get_ports {vga_r[2]}]

set_property PACKAGE_PIN V18 [get_ports {vga_r[3]}]

set_property PACKAGE_PIN AB22 [get_ports {vga_g[0]}]

set_property PACKAGE_PIN AA22 [get_ports {vga_g[1]}]

set_property PACKAGE_PIN AB21 [get_ports {vga_g[2]}]

set_property PACKAGE_PIN AA21 [get_ports {vga_g[3]}]

set_property PACKAGE_PIN Y21 [get_ports {vga_b[0]}]

set_property PACKAGE_PIN Y20 [get_ports {vga_b[1]}]

set_property PACKAGE_PIN AB20 [get_ports {vga_b[2]}]

set_property PACKAGE_PIN AB19 [get_ports {vga_b[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_r[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_r[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_r[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_r[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_g[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_g[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_g[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_g[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_b[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_b[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_b[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {vga_b[0]}]

set_property PACKAGE_PIN AA19 [get_ports vga_hs]

set_property PACKAGE_PIN Y19 [get_ports vga_vs]

set_property IOSTANDARD LVCMOS33 [get_ports vga_hs]

set_property IOSTANDARD LVCMOS33 [get_ports vga_vs]

因v_tc产生的时序和vga时序有所不同,所以在顶层需要对hs和vs进行处理,并且输出数据需要使用vid_active_video信号进行使能

生成bit文件

导出硬件配置

打开SDK

新建fsbl

新建完成的fsbl

新建vdma_vga工程,选择刚刚新建的fsbl_bsp

现在hello_world 模板,点击Finish

新建的vdma_vga工程

在src下重新加入1080p.c图片数据文件和新的hello_world.c文件,hello_world文件为vdma的配置

hello_world文件代码,这里代码参考虚无缥缈vs威武的博客

/*

* Copyright (c) 2009-2012 Xilinx, Inc. All rights reserved.

*

* Xilinx, Inc.

* XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION "AS IS" AS A

* COURTESY TO YOU. BY PROVIDING THIS DESIGN, CODE, OR INFORMATION AS

* ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, APPLICATION OR

* STANDARD, XILINX IS MAKING NO REPRESENTATION THAT THIS IMPLEMENTATION

* IS FREE FROM ANY CLAIMS OF INFRINGEMENT, AND YOU ARE RESPONSIBLE

* FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE FOR YOUR IMPLEMENTATION.

* XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO

* THE ADEQUACY OF THE IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO

* ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE

* FROM CLAIMS OF INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY

* AND FITNESS FOR A PARTICULAR PURPOSE.

*

*/

/*

* helloworld.c: simple test application

*

* This application configures UART 16550 to baud rate 9600.

* PS7 UART (Zynq) is not initialized by this application, since

* bootrom/bsp configures it to baud rate 115200

*

* ------------------------------------------------

* | UART TYPE BAUD RATE |

* ------------------------------------------------

* uartns550 9600

* uartlite Configurable only in HW design

* ps7_uart 115200 (configured by bootrom/bsp)

*/

#include <stdio.h>

#include "xparameters.h"

#include "xil_io.h"

#include "sleep.h"

#define DDR_BASEADDR 0x00000000

#define VDMA_BASEADDR XPAR_AXI_VDMA_0_BASEADDR

#define H_STRIDE 1920

#define H_ACTIVE 1920

#define V_ACTIVE 1080

#define VIDEO_LENGTH (H_STRIDE*V_ACTIVE)

#define VIDEO_BASEADDR0 DDR_BASEADDR + 0x2000000

#define VIDEO_BASEADDR1 DDR_BASEADDR + 0x3000000

#define VIDEO_BASEADDR2 DDR_BASEADDR + 0x4000000

//函数声明

void Xil_DCacheFlush(void);

extern const unsigned char gImage_beijing[8294400];

void show_img(u32 x, u32 y, u32 disp_base_addr, const unsigned char * addr, u32 size_x, u32 size_y)

{

//计算图片 左上角坐标

u32 i=0;

u32 j=0;

u32 r,g,b;

u32 start_addr=disp_base_addr;

start_addr = disp_base_addr + 4*x + y*4*H_STRIDE;

for(j=0;j<size_y;j++)

{

for(i=0;i<size_x;i++)

{

b = *(addr+(i+j*size_x)*4+1);

g = *(addr+(i+j*size_x)*4+2);

r = *(addr+(i+j*size_x)*4+3);

Xil_Out32((start_addr+(i+j*H_STRIDE)*4),((r<<24)|(g<<16)|(b<<8)|0x0));

}

}

Xil_DCacheFlush();

}

int main()

{

//各种显示 相关的参数

Xil_Out32((VDMA_BASEADDR + 0x000), 0x00000003); // enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x05c), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x060), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x064), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x058), (H_STRIDE*4)); // h offset (1920 * 4) bytes

Xil_Out32((VDMA_BASEADDR + 0x054), (H_ACTIVE*4)); // h size (1920 * 4) bytes

Xil_Out32((VDMA_BASEADDR + 0x050), V_ACTIVE); // v size (1080)

while(1)

{

show_img(0,0,VIDEO_BASEADDR0,&gImage_beijing[0],1920,1080);

}

}

生成BOOT.bin文件

生成的BOOT.bin文件,将生成的BOOT.bin文件拷贝到SD卡里运行

开发板插上SD卡,上电后连接VGA接口

感觉颜色有点异常,但大致是显示了图片数据,需要对vga的数据打拍才能使颜色正常,先写到这里有时间再改下顶层时序

本文介绍了一个基于Zedboard开发板的VGA显示项目,详细记录了从创建Vivado工程到SDK软件开发的全过程,包括硬件配置、IP核设置、顶层文件编写、约束设置及软件编程等关键步骤。

本文介绍了一个基于Zedboard开发板的VGA显示项目,详细记录了从创建Vivado工程到SDK软件开发的全过程,包括硬件配置、IP核设置、顶层文件编写、约束设置及软件编程等关键步骤。

1037

1037

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?