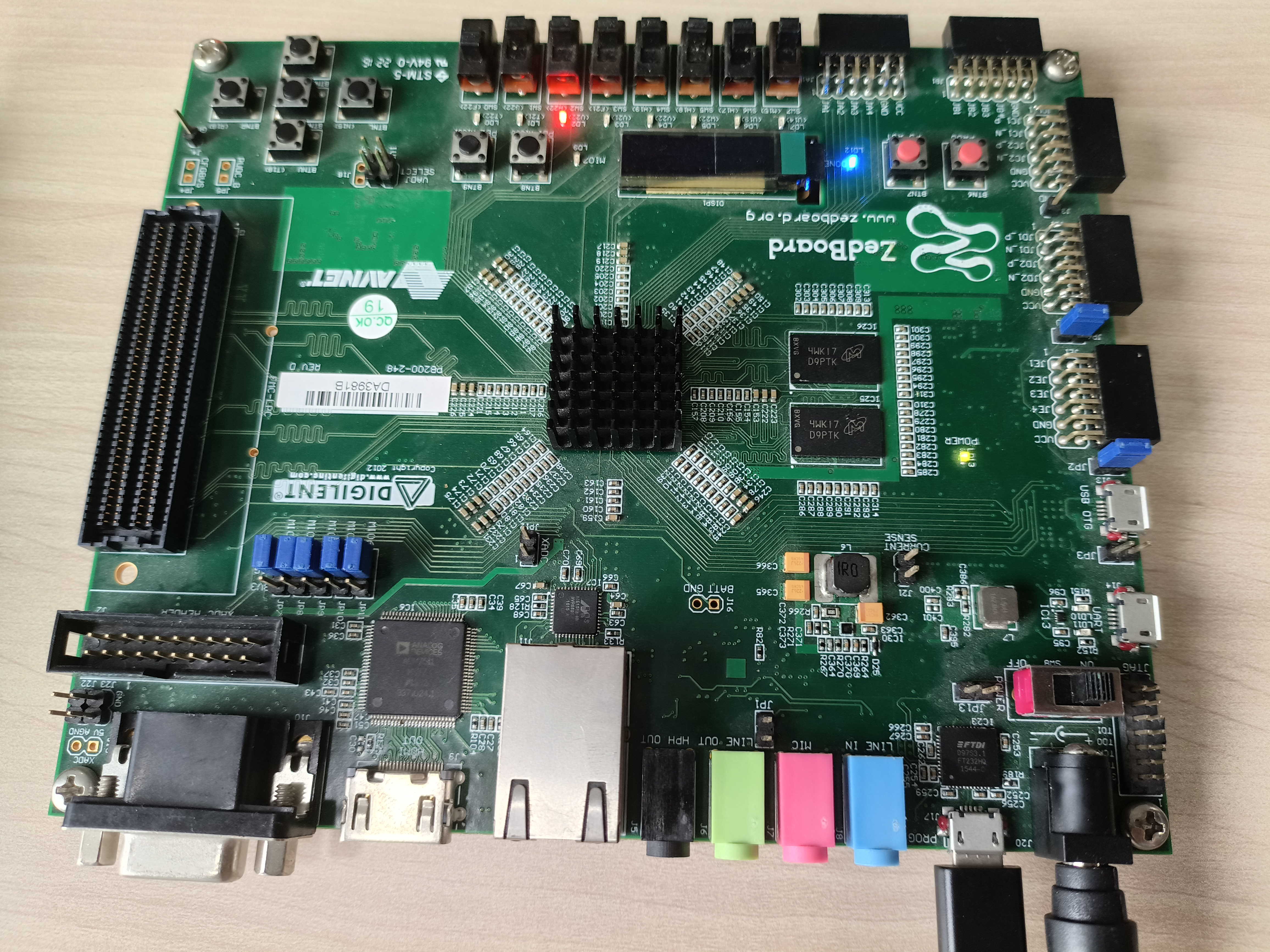

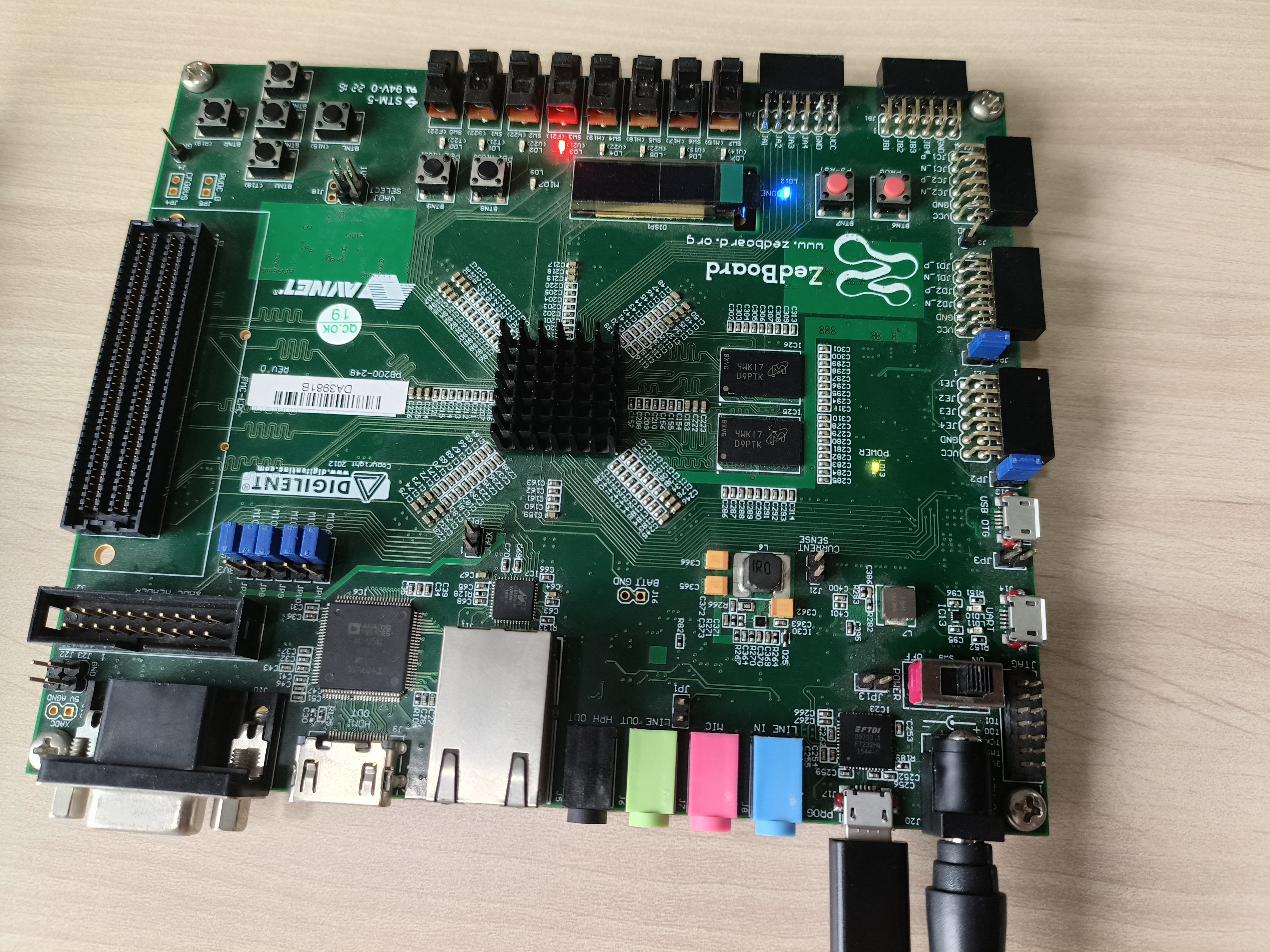

开发板环境:vivado2017.4

开发板:Zedboard 芯片型号:xc7z020clg484-1

本章主要使用用verilog编写一个流行灯代码控制PL端的八个LED

1.打开vivado2017.4

2.点击Create Project 新建工程,点击Next

3.填写工程名和选择工程存储路径,点击Next

点击Next

点击Next

点击Next

4.选择官方提供的板级包,并选择ZedBoard Zynq这个型号后面会显示芯片型号,点击Next

点击Finish,创建一个zynq工程

zynq工程界面,可以看到右边显示官方的开发板图片

5.编写流水灯代码

新建led_test.v文件

点击Next

点击Create File新建工程,填写工程名为led_test

点击Finish

新建的led_test.v

流水灯代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date:

// Design Name:

// Module Name: led_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module led_test(

input clock,//100M

input reset,//SW0

output [7:0] led//LED0~LED7

);

reg [32:0] count;

reg [2:0] led_cnt;

reg [7:0] led_reg;

//0.5s计数

always@(posedge clock or negedge reset)begin

if(!reset)

count <= 32'd0;

else if(count == 32'd50000000 - 1'b1)

count <= 32'd0;

else

count <= count + 1'b1;

end

//led计数0~7

always@(posedge clock or negedge reset)begin

if(!reset)

led_cnt <= 3'd0;

else if(count == 32'd50000000 - 1'b1)

led_cnt <= led_cnt + 1'b1;

else

led_cnt <= led_cnt;

end

//根据计数值点亮led

always@(posedge clock or negedge reset)begin

if(!reset)

led_reg <= 8'b00000000;

else case(led_cnt)

0: led_reg <= 8'b00000001;

1: led_reg <= 8'b00000010;

2: led_reg <= 8'b00000100;

3: led_reg <= 8'b00001000;

4: led_reg <= 8'b00010000;

5: led_reg <= 8'b00100000;

6: led_reg <= 8'b01000000;

7: led_reg <= 8'b10000000;

default:led_reg <= 8'b00000000;

endcase

end

assign led = led_reg;

endmodule

6.分配硬件管脚

led管脚

复位管脚直接使用SW0,这里不进行按键检测处理

时钟管脚

点击RTL ANALYSIS下面的Open Elaborated Design来分配管脚

分配时钟管脚

按Ctrl+S保存管脚约束文件

生成的管脚约束文件

约束文件

set_property PACKAGE_PIN T22 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN T21 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN U22 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property PACKAGE_PIN U21 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property PACKAGE_PIN V22 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property PACKAGE_PIN W22 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property PACKAGE_PIN U19 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property PACKAGE_PIN U14 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property PACKAGE_PIN Y9 [get_ports clock]

set_property IOSTANDARD LVCMOS33 [get_ports clock]

set_property PACKAGE_PIN F22 [get_ports reset]

set_property IOSTANDARD LVCMOS33 [get_ports reset]

7.编译工程生成bit下载文件

点击Generate Bitstream,生成bit文件

生成bit下载文件成功,点击Cancel关闭对话框

8.连接JTAG,下载bit文件运行

点击Open Target自动识别jtag

识别到了fpga芯片

右击选择Program Device

找到bit文件路径,然后点击Program进行下载

注意将SW0打到上面,不然会一直对工程进行复位,LED也不会亮

下面是流水灯部分效果图

1329

1329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?