欢迎FPGA工程师加入官方微信技术群

点击蓝字关注我们FPGA之家-中国最好最大的FPGA纯工程师社群

“ 课堂上给大家介绍代码规范的时候,反复强调不能出现组合逻辑环,具体就是组合逻辑所有的else语句要写全,case语句也要写全,但组合逻辑环到底有什么危害?下面就详细举例说明。”

01

—

什么是组合逻辑环?

组合逻辑反馈环路是数字同步逻辑设计的大忌,它最容易因振荡、毛刺、时序违规等问题引起整个系统的不稳定和不可靠。 组合逻辑反馈环路是二种高风险的设计方式,主要原因如下:

1.组合反馈环的逻辑功能完全依赖于其反馈环路上组合逻辑的门延时和布线延时等,如果这些传播延时有任何改变,则该组合反馈环单元的整体逻辑功能将彻底改变,而且改变后的逻辑功能很难确定。

2.组合反馈环的时序分析是无穷循环的时序计算,综合、实现等EDA 工具迫不得已一般必须主动割断其时序路径,以完成相关的时序计算。而不同的EDA工具对组合反馈环的处理方法各不相同,所以组合反馈环的最终实现结果有很多不确定因素。

3.通常的综合工具在处理组合逻辑反馈问题时,将产生Latch,这将对时序造成许多问题。

在用Verilog HDL进行可综合电路设计时,有很多情况都有可能产生组合逻辑环。

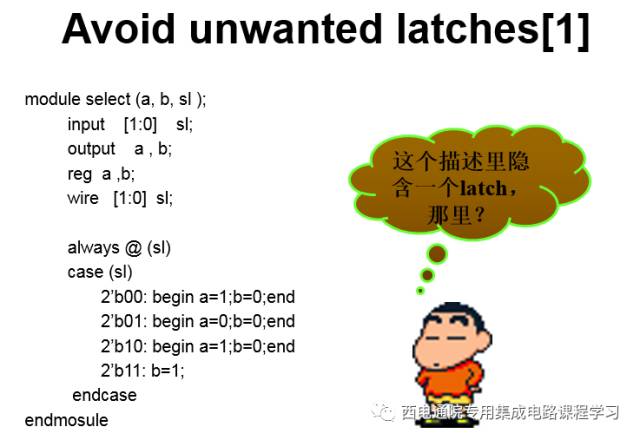

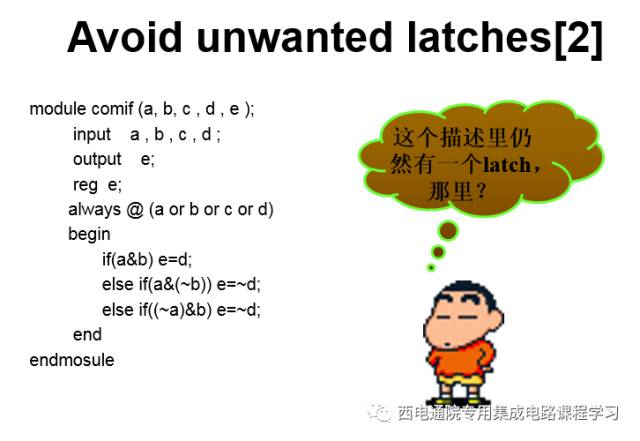

•在组合逻辑的组合进程中, 条件语句描述时应该指定所有条件下所有输出的状态,以避免锁存。比如if/case语句的所有分支必须定义全部的输出才可能避免出现锁存。

•在设计中,应该尽量避免使用锁存!因为锁存要占去大量的触发器资源,而且会对电路带来某种不稳定的隐患。

•所谓的latch,其实质是组合电路中有反馈!反馈的形成是利用到了前一个状态。

具体举例如下:

总结如下:

•组合电路描述中,条件判断语句必须指明所有条件分支情况下,被赋值信号的值。

•分支不完整,意味着电路需要在某种电平状态下,让被赋值的信号“保持原值”,这只能使用锁存电路实现。

02

—

一个实例

设计代码如下:

// **************************************************************

// COPYRIGHT(c)2015, Xidian University

// All rights reserved.

//

// IP LIB INDEX :

// IP Name :

// File name :

// Module name :

// Full name :

//

//

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

122

122

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?