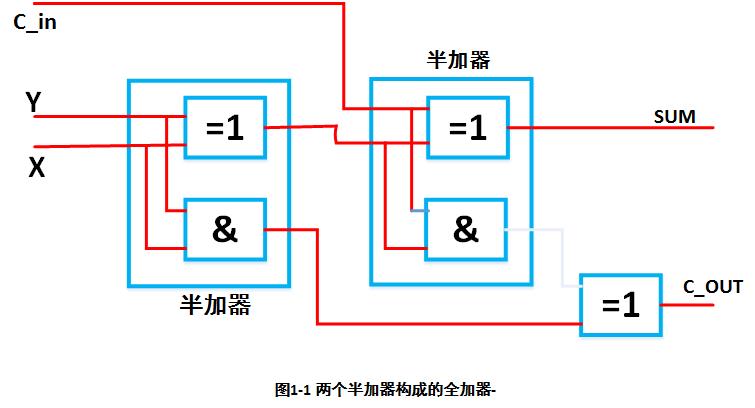

一个verilog程序可以包含多个模块,以满足一个复杂的程序设计。调用多个模块是通过端口关联来进行实现的,这种调用实际上是 一种硬件电路的嵌入,调用的方式是模块实例化,其中端口关联有两种方式:一种是位置关联,一种是名称关联,形式为“.端口名(变量名)“,实现端口与变量的关联。下面通过两个半加器来实现一个全加器来加以说明调用的方式:

moudle HalfAdd(X,Y,SUM,C_out);

input X,Y;

output SUM,C_out;

xor u_xor(SUM,X,Y);

and u_and(C_out,X,Y);

endmoudle

moudle FullAdd(X,Y,C_in,SUM,C_out);

input X,Y;

output C_in,Sum,C_out;

wire HalfAdd_A_SUM;

wire HalfAdd_A_COUT;

wire HalfAdd_B_COUT;

or u_or(C_out,HalfAdd_A_COUT,HalfAdd_B_COUT);

HalfAdd u_HalfAdd_A(.X(X),.Y(Y),.SUM(HalfAdd_A_SUM),.C_out(HalfAdd_A_COUT));

HalfAdd u_HalfAdd_B(.X(X),.Y(Half_A_SUM),.SUM(SUM),C_out(HalfAdd_B_COUT)));

endmoudle

1427

1427

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?