数字后端面试问题No.7-9(每日三问)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

今天继续分享三道面试题,其中第一道题可以作为巩固 timing borrowing 知识点,起到帮助各位复习的功效(中午没能加上鸡腿,没力气了,呵呵)。第二三道题是 CTS 相关。另外,想进吾爱 IC 社区技术交流群的,可以先加小编微信,然后邀请各位入群。

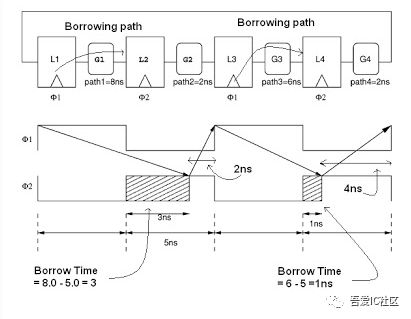

1.Please explain details of the timing borrowing based on the following latch based design?And what is the advantage compared to FF(Flip Flop) design?

这道题其实跟吾爱 IC 社区昨天推送的分享是同一个 topic。大家可以练练手,答案都在波形图中了(大家自己画画)。

听说 Latch 可以高效修 hold 违例(Timing borrowing 及其应用)

Base FF 的设计,需要 4*8=32ns 时间来完全电路所要求的功能。而基于 Latch 的设计只需要 20ns 即可。

2.Please write a sdc for the following circuit, and explain how ICC to handle cascaded generated clocks when the generated clock in two overlapped clocks

create_clock -name clk1 [get_ports clk1]

create_clock -name clk1 [get_ports clk2]

create_generated_clock -name genclk2 -source [get_ports clk2] -divide_by 2 [get_pins FF1/Q]

set_case_analysis 1 [get_pins mux/S]

set_clock_group -logically_exclusive -group clk1 -group clk2 (logically_exclusive 和 physically_exclusive 的区别,面试经常问到哦)

CTS will synthesis genclk2 when doing clock tree synthesis on clk2.

3.Why we use inverters not buffers when building clock tree?

-

Less insertion delay(latency)

-

Less switching power than buffers for an equivalent number of stages,and also less leakage power

-

no duty cycle distortion and inverters can self-correct(the distortion of inverter can be automatically corrected by next stage because of symetric)

相关文章推荐(不看保证后悔)

听说 Latch 可以高效修 hold 违例(Timing borrowing 及其应用)

秒杀数字后端实现中 clock gating 使能端 setup violation 问题

教你轻松调 DCT 和 ICC 之间 Timing 与 Congestion 的一致性

Scan chain reordering 怎么用你知道吗?

数字后端实现时 congestion 比较严重,你 hold 得住吗?

Final netlist release 前,你应该做好哪些工作?

深入浅出讲透 set_multicycle_path,从此彻底掌握它

数字后端实现时 congestion 比较严重,你 hold 得住吗?

时钟树综合(clock tree synthesis)基础篇

好了,今天的内容分享就到这里。另外,因为公众号更改推送规则,小编分享的每篇干货不一定能及时推送给各位。为了避免错过精彩内容,请关注星标公众号,点击 “在看”,点赞并分享到朋友圈,让推送算法知道你是社区的老铁,这样就不会错过任何精彩内容了。

如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

-

基于 90nm 项目案例实现教程(ICC 和 Innovus 配套教程)

-

数字 IC 行业百科全书

吾爱 IC 社区知识星球星主为公众号” 吾爱 IC 社区” 号主,从事数字 ic 后端设计实现工作近八年,拥有55nm,40nm,28nm,22nm,14nm等先进工艺节点成功流片经验,成功tapeout 过三十多颗芯片。

这里是一个数字 IC 设计实现高度垂直细分领域的知识社群,是数字 IC 设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字 ic 前端设计,后端实现,模拟 layout 工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字 ic 后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有 880 星球成员,感谢这880童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。

欢迎关注 “吾爱 IC 社区”

微信号:ic-backend2018

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?