uvm寄存器模型RAL

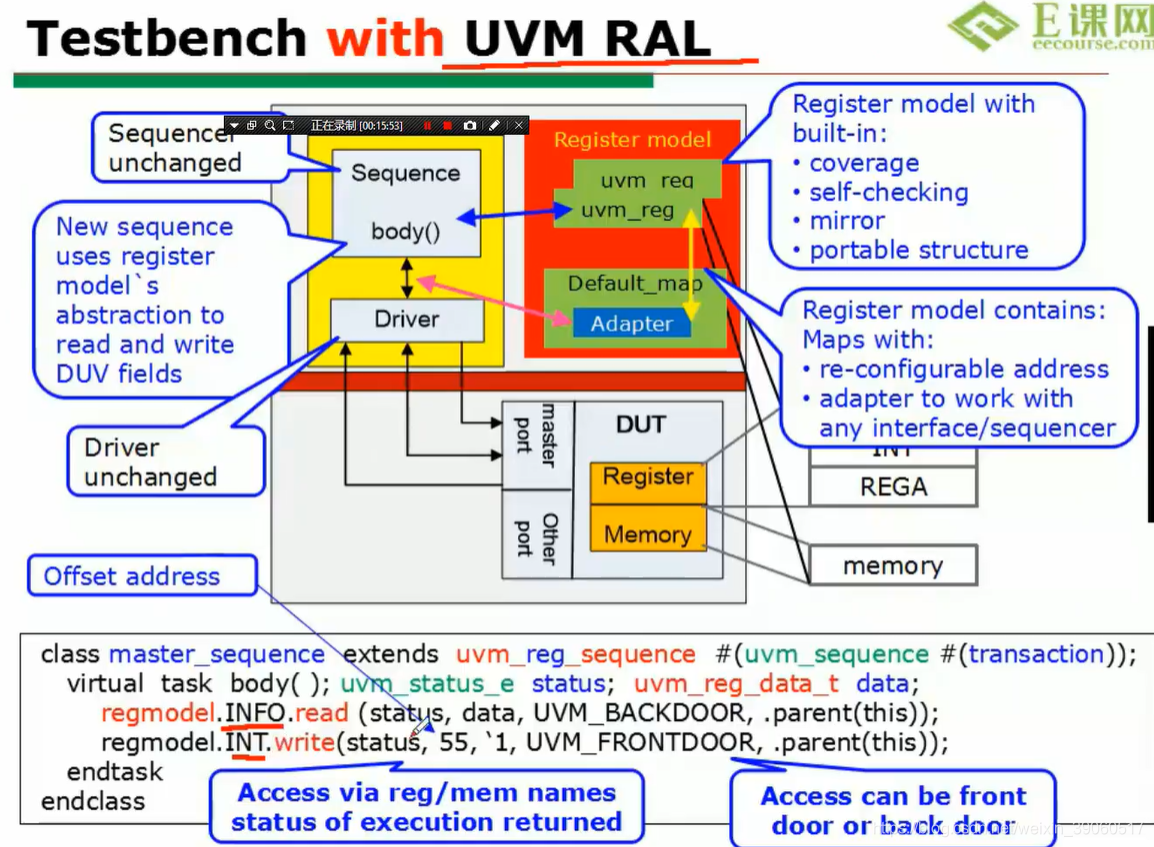

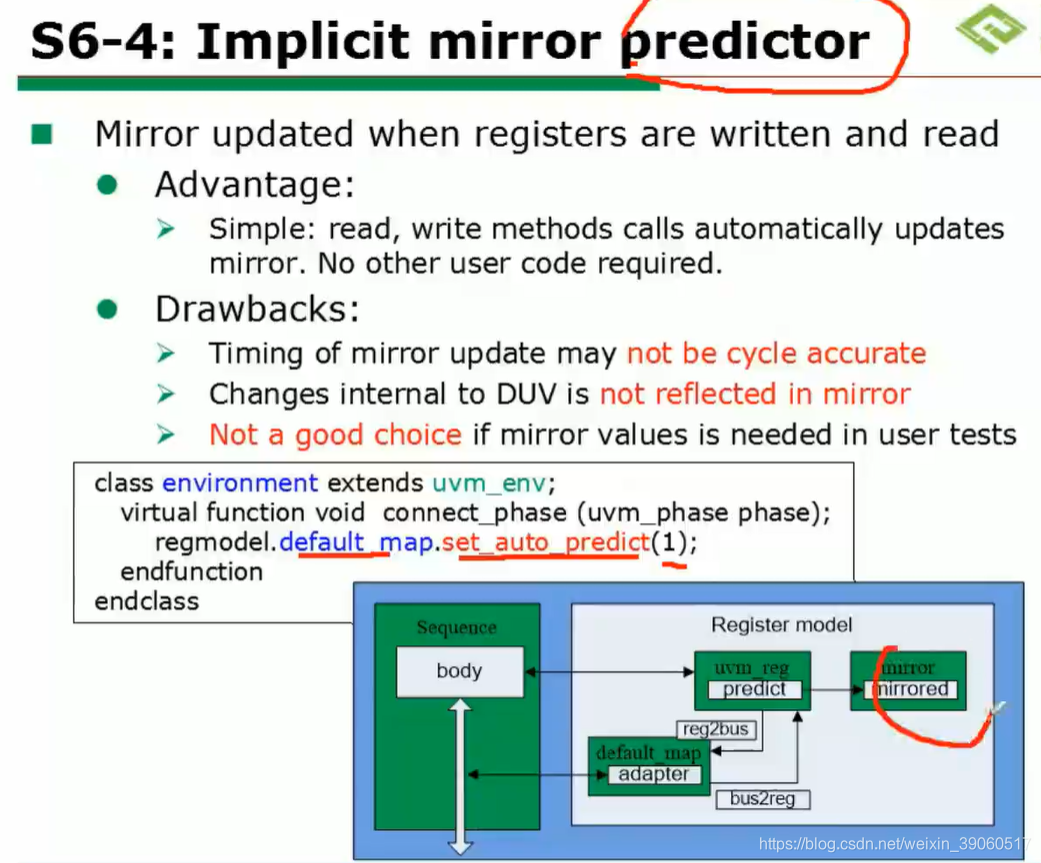

implicit predictor 自动预测

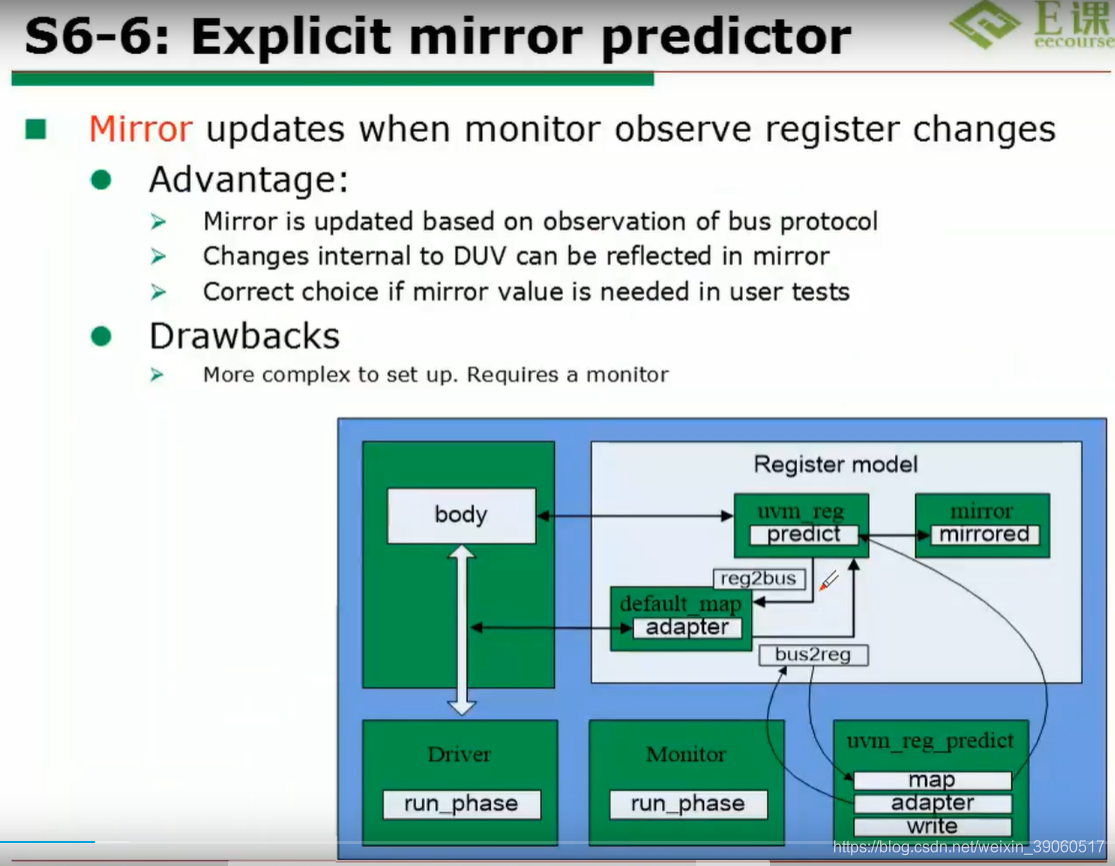

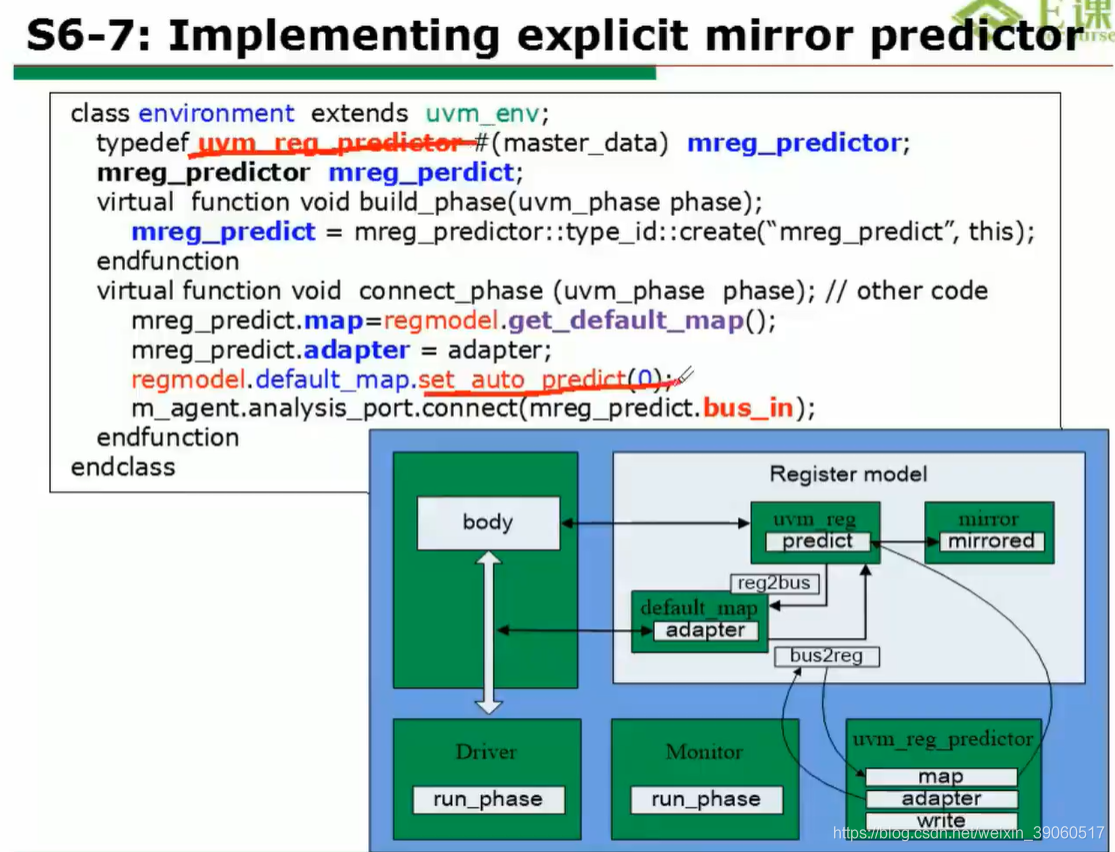

explicit predictor

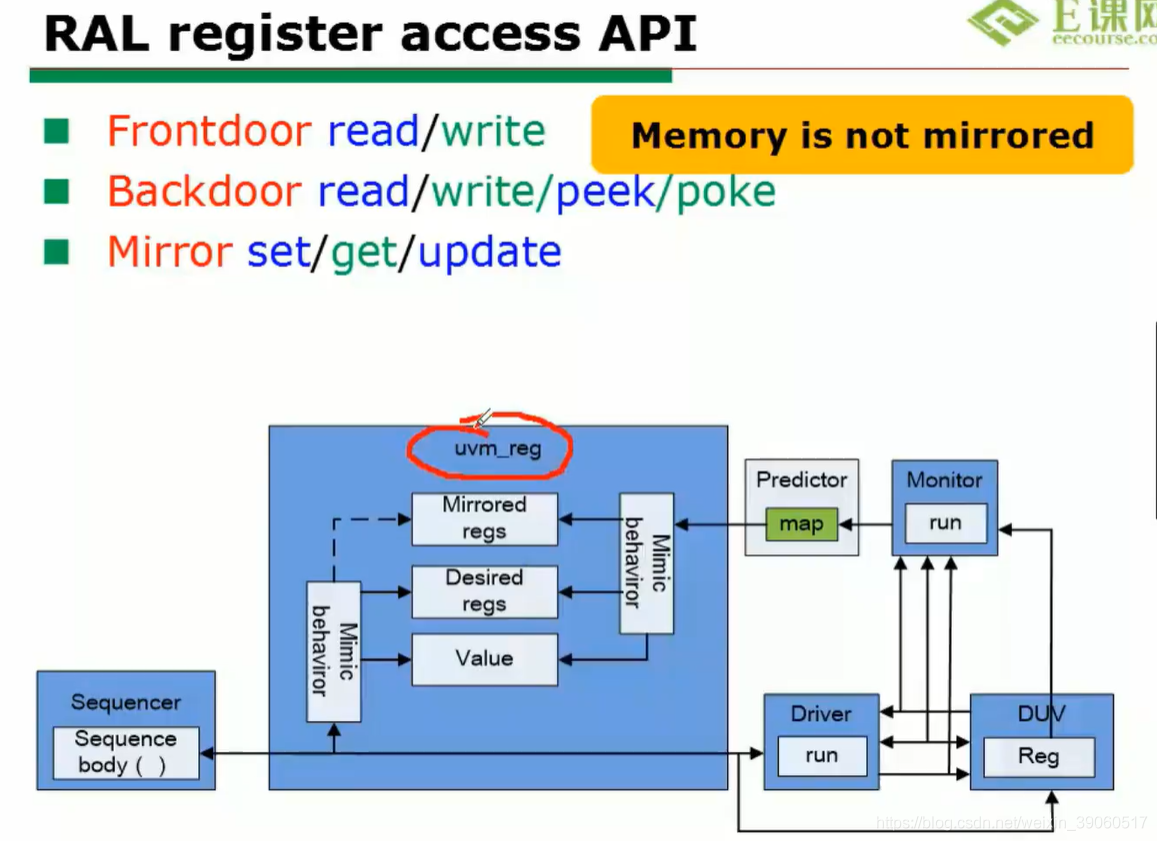

register model

uvm_reg_block

- 属于uvm_object

reg

field最小单位

- m_mirrored

- m_desired

至少包含一个reg_map

map

- 调用reg2bus /bus2reg函数

- 连接adapter/seqr

- 子map

uvm_mem

seq中访问register model的两种方法

a.通过config_db

往seq中传递一个句柄;

uvm_config_db #(reg_top_block)::set(this, "*", "reg_top_block", reg_rm);

b. 通过sequencer

通过p_sequencer调用sqr中的register model的句柄

connect_phase 中 ref_mdl.p_rm = this.p_rm;

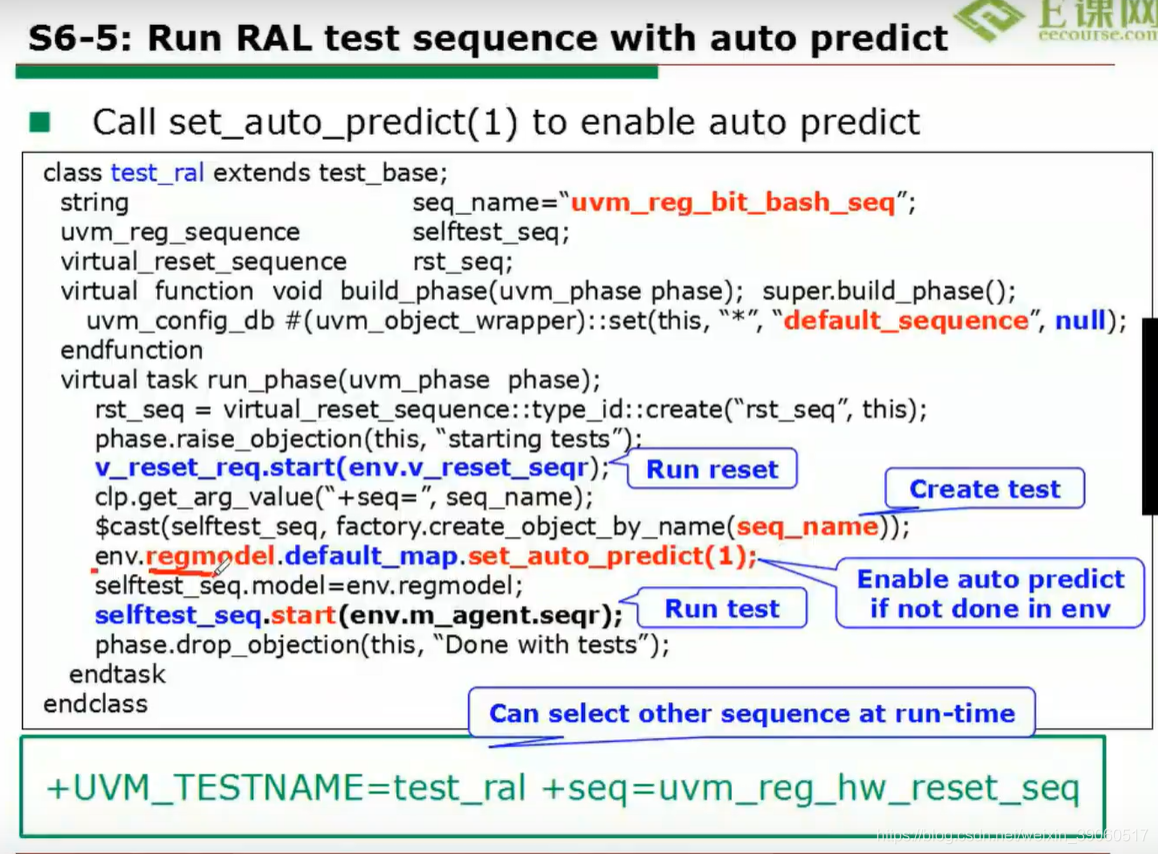

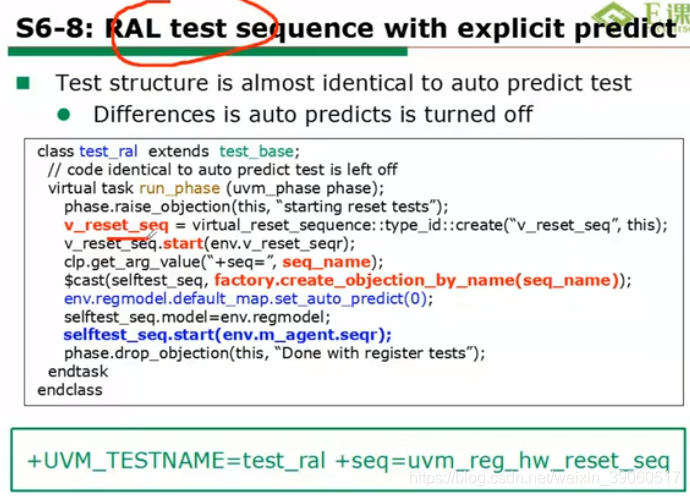

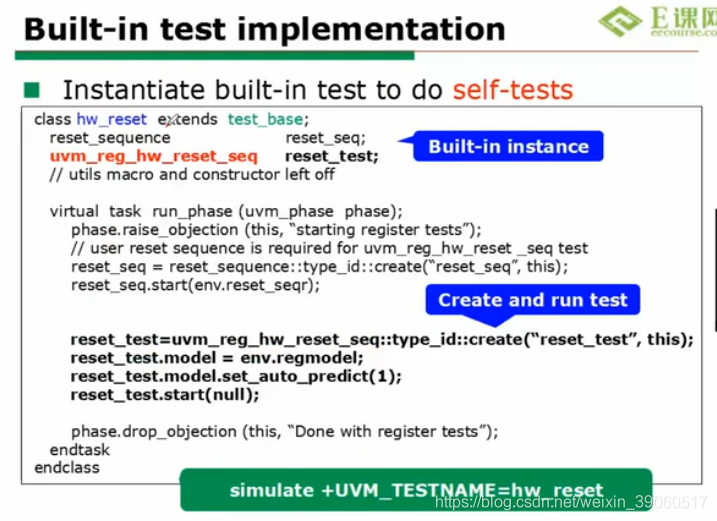

RAL内建的一些sequence

需要掌握下边两个sequence

- uvm_reg_hw_reset_seq

- uvm_reg_bit_bash_seq

uvm_reg_hw_reset_seq 检查上电复位后寄存器模型与DUT 寄存器的默认值是否相同

- 把register model的句柄赋值给这个sequence的model

- 此seq通过前门读取寄存器的值与ral模型中的mirror值做比较,不一样则报错. 调用reg的mirror方法

- 在测试时如果有些寄存器的默认值不需要关注,那么可以通过设置NO_REG_TESTS或者NO_REG_HW_RESET_TEST来实现.在实际的应用当中也支持对整个block做exclude处理.

UVM:7.6.2 检查默认值的sequence

uvm_reg_hw_reset_seq

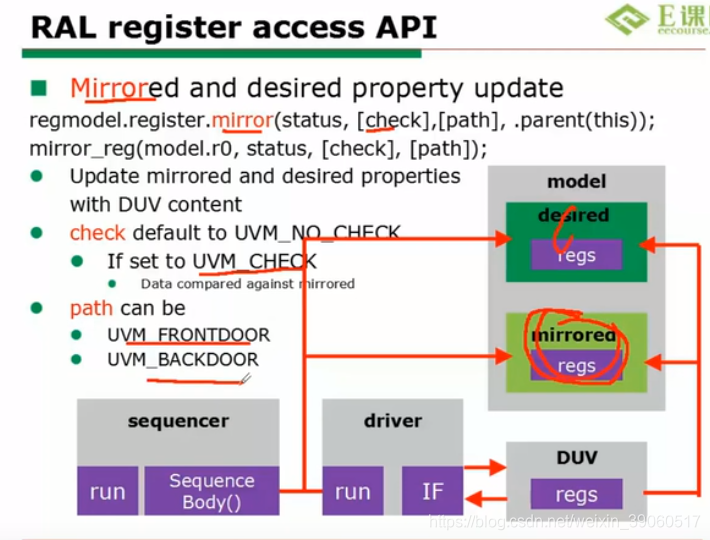

mirror

virtual task mirror( output uvm_status_e status, //报错

input uvm_check_e check = UVM_NO_CHECK,

input uvm_path_e path = UVM_DEFAULT_PATH,

input uvm_reg_map map = null,

input uvm_sequence_base parent = null,

input int prior = -1,

input uvm_object extension = null,

input string fname = "",

input int lineno = 0 )

读DUT中寄存器的值,与update操作相反。如果第二个参数check为UVM_CHECK,那么会检查读取的值与镜像值是否一样,如果不一样报错。通过mirror读取DUT的寄存器值之后,会调用predict函数,更新镜像值。

mirror有两种应用场景:一是在仿真中不断调用,但此时是UVM_NO_CHECK,保证镜像值与DUT中的值相等;二是在仿真结束的时候调用,这时是UVM_CHECK检查模型中的镜像值与DUT中的寄存器值是否一致。

uvm_reg_bit_bash_seq

Verify the implementation of all registers in a block by executing the uvm_reg_single_bit_bash_seq sequence on it.

Verify the implementation of a single register by attempting to write 1’s and 0’s to every bit in it, via every address map in which the register is mapped, making sure that the resulting value matches the mirrored value.

uvm_reg_bit_bash_seq实现对寄存器每个bit的遍历操作,通过前门写前门读确认每个bit读写操作是否ok.此操作对RW寄存器有效,因为本身其就要支持读写操作,如果读写有问题就可以发现错误;对于诸如RO、RC这样属性的寄存器,本身就不支持写操作,会导致误报错误,所以后续需要exclude掉.

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?