xilinx fpga的设计规范和时序问题解决

xilinx FPGA在设计时,代码编写尽量使用vivado中的代码模板,模板代码可以综合正确且结构简介的电路结构;Tools>>Language Templates;

代码框架:I/O模块和时钟尽量放在顶层,目的是资源共享,提高性能,降低功耗;输出采用寄存器输出,降低路径延时保证时序收敛。

复位:官方推荐采用高电平同步复位,降低资源使用和功耗,有助于时序收敛。

时序修正

时序问题主要有两个:建立时间(setup time)和保持时间(hold time)。

建立时间(setup time):指触发器的时钟上升沿到来之前,数据保持稳定的时间。导致建立时间违规主要有两个原因:逻辑级数(Logic Level)太大或者扇出(fanout)太大。

Logic Level:包含一个net和一个LUT延迟。logic level和器件的工作最高频率有关,级数不可以太大,否则会造成时序收敛困难。

解决由建立时间造成的时序收敛问题解决办法是采用重定时的方法,将冗长的组合逻辑进行寄存器打拍输出。

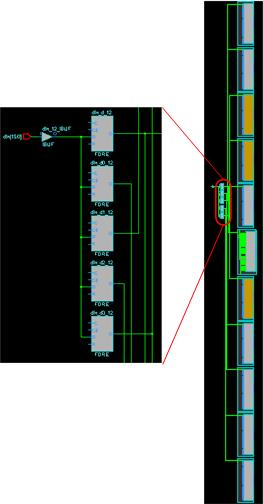

fanout:指模块直接调用下级模块的个数,fanout过大在FPGA表现出来的是netdelay较大,不利于时序收敛,同样和器件、设计频率有关。

上图是没有使用优化的输出,驱动了11个DSP48E11,最高工作频率为fmax=206.016MHz。

解决fanout的办法:

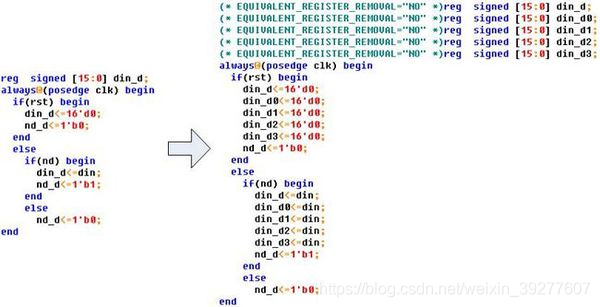

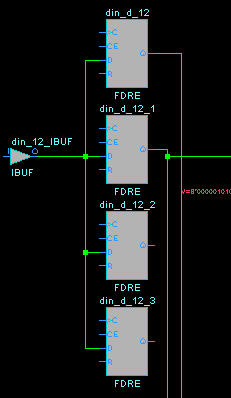

1,寄存器复制:

通过复制几个相同的寄存器来分担原先由一个寄存器驱动所有模块的问题,继而达到减小扇出的目的。

2,使用max_fanout约束:

在代码中设置信号属性(* max_fanout = “3” *)reg signed [15:0] din_d;

3,使用BUFG(主要针对时钟和复位的扇出太大)

2182

2182

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?