什么是加法器:

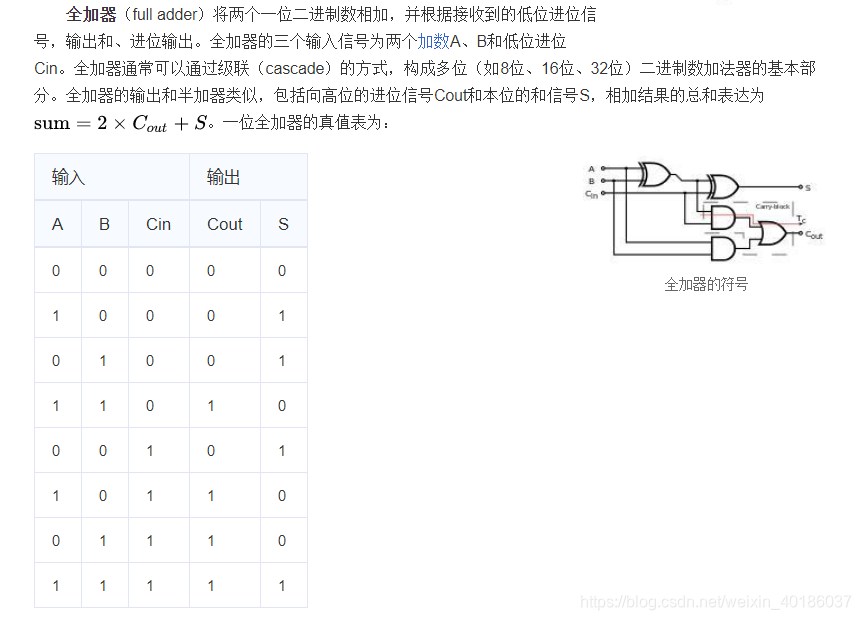

在电子学中,加法器(英语:adder)是一种用于执行加法运算的数字电路部件,是构成电子计算机核心微处理器中算术逻辑单元的基础。在这些电子系统中,加法器主要负责计算地址、索引等数据。除此之外,加法器也是其他一些硬件,例如:二进制数乘法器的重要组成部分。

尽管可以为不同计数系统设计专门的加法器,但是由于数字电路通常以二进制为基础,因此二进制加法器在实际应用中最为普遍。在数字电路中,二进制数的减法可以通过加一个负数来间接完成。为了使负数的计算能够直接用加法器来完成,计算中的负数可以使用二补数(补码)来表示,具体的细节可以参考数字电路相关的书籍。

VHDL代码:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder is

port(

A,B,Cin:in std_logic;

S,Cout:out std_logic

);

end adder;

architecture Behavioral of adder is

begin

S <= ((A xor B) xor Cin);

Cout <=((A xor B) AND Cin) OR (A AND B);

end Behavioral;

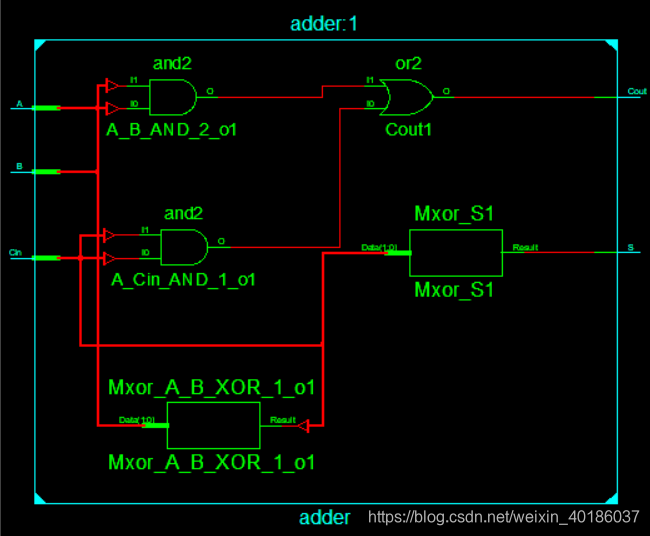

生成对应原理图:

testbench:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_adder IS

END tb_adder;

ARCHITECTURE behavior OF tb_adder IS

COMPONENT adder

PORT(

A : IN std_logic;

B : IN std_logic;

Cin : IN std_logic;

S : OUT std_logic;

Cout : OUT std_logic

);

END COMPONENT;

--Inputs

signal A : std_logic := '1';

signal B : std_logic := '0';

signal Cin : std_logic := '1';

--Outputs

signal S : std_logic;

signal Cout : std_logic;

signal clk,rst:std_logic;

constant clk_period : time := 10 ns;

BEGIN

uut: adder PORT MAP (

A => A,

B => B,

Cin => Cin,

S => S,

Cout => Cout

);

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

stim_proc: process

begin

rst<='0';

wait for 10 ns;

rst<='1';

wait;

end process;

END;

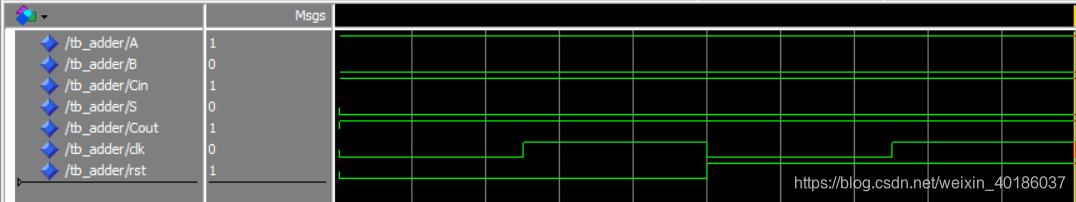

使用modelsim进行仿真,波形如下:

2024

2024

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?