目录

1.简介

FPGA开发的流程大体分为需求分析,模块划分,RTL开发,功能模块仿真,上版调试几个步骤。由于FPGA代码编译综合的时间相对比较长,因此上板调试也是工程实践中最耗费时间的一部分,但同时也是完成项目必不可少的一步。在上板调试过程中,xilinx提供了VIO IP核和ILA逻辑分析仪等工具提高调试效率。本文介绍VIO IP核,介绍使用场景,IP配置和快速使用的方法。

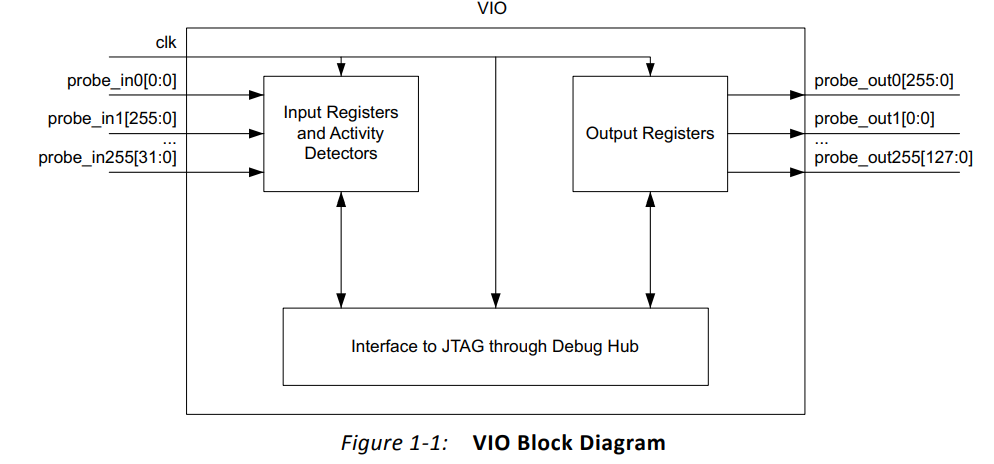

VIO(Virtual Input/Output)IP核是一种用于FPGA设计的IP核,它可以模拟输入/输出设备的功能,如键盘、鼠标、显示器等。VIO IP核可以在FPGA设计中用于调试和验证,帮助工程师快速定位问题并进行调试。如图所示,VIO通过JTAG接口与芯片内部互换信息,其中output指VIO IP的输出对于FPGA内部逻辑是输入信号。Input指VIO IP的输入对于FPGA内部逻辑是输出信号,用来监测信号变化,与ILA相比,VIO无需占用ram资源。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1685

1685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?