目录

前言

vivado自带的编辑器具有自动语法规则检查,字体设置,颜色配置等功能。但在实际编写代码的过程中,发现诸多不足,例如无法放大缩小,对齐功能不好用等缺点。文本编辑器有很多选择,例如Notepad、Sublime Text、VS Code等,选择一款适合自己的编辑器,有助于养成自己的代码风格并为FPGA开发提供极大方便。下面以VS Code为例,介绍如何配置文本编辑器。

1.安装VS Code

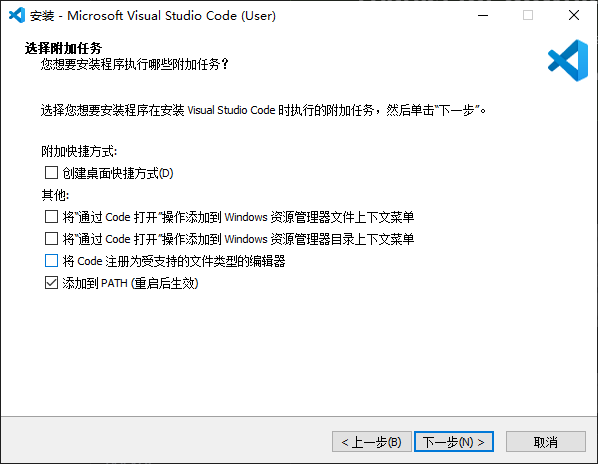

访问VS Code官网下载软件并且提供了使用说明,安装步骤按照如下勾选即可。中间省略了同意协议,选择路径和点击安装的简单步骤。

2.安装插件

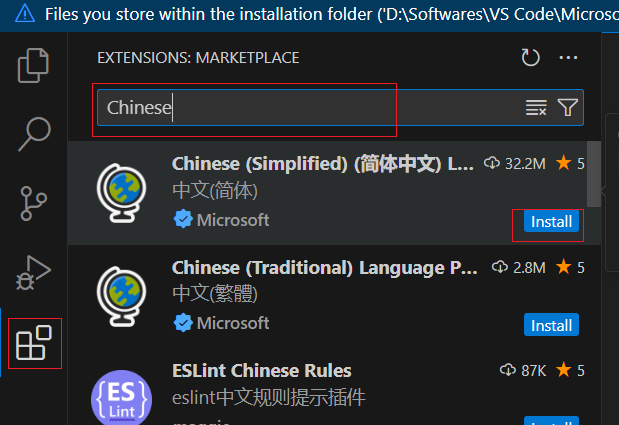

- ①安装汉化包插件,如下图所示。单击左侧工具栏的 extensions 或者使用快捷键【Ctrl+Shift+X】,输入 chinese,点击 Install 安装中文简体。

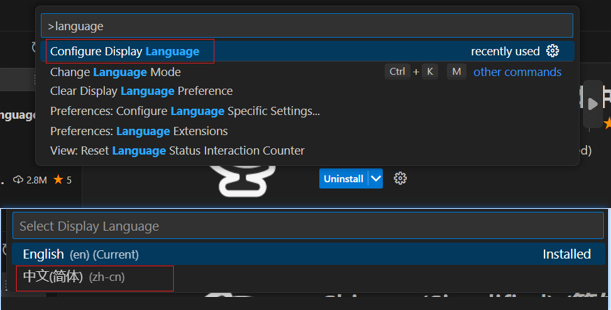

②配置VS Code语言包,使用快捷键【Ctrl+Shift+P】弹出查找命令框,输入 language, 找到 Configure Display Language,单击并选择 locale 属性为"zh-CN",如下图所示。

③重启软件,汉化环境已经就位。

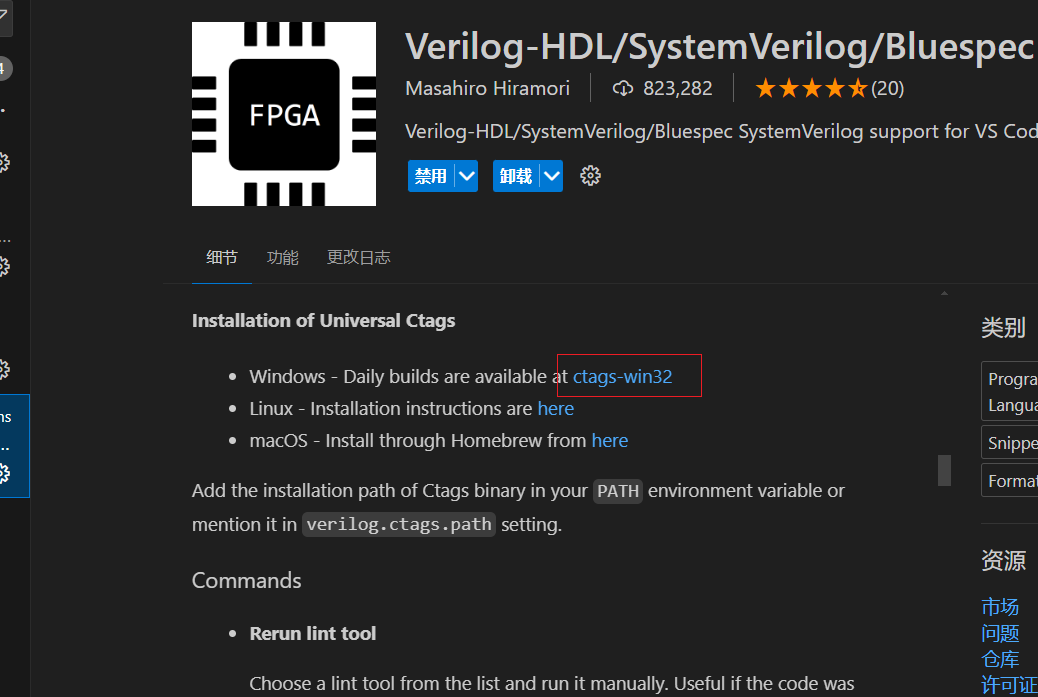

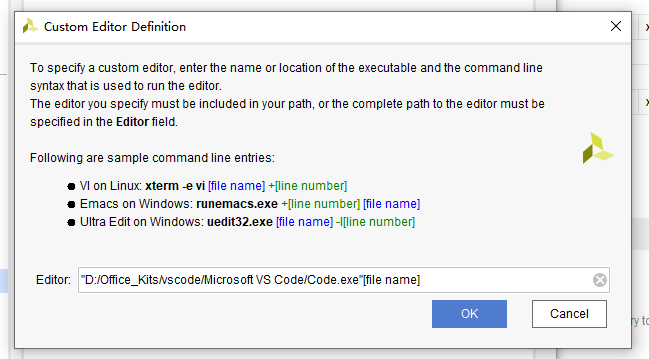

④使用安装汉化包一样的方式安装Verilog-HDL/SystemVerilog/Bluespec SystemVeril(后续简称Verilog-HDL)、Verilog Highlight、CTags Support三个插件。其中Verilog-HDL提供了vivado编辑器提供的大多数功能,如代码高亮(highlight)简单语法补全提示(snippets),以及静态语法检查(lint,需要自行配置linter组件),Ctags功能集成(需要额外安装ctags组件)。

⑤安装verilog-simplealign插件,用来对齐代码块,安装后选中想要对齐的代码ctrl+L即可。

⑥安装verilog-testbench插件,用于生成仿真文件所必要的一些格式,非常方便。安装这个插件需要安装python3的环境,并在windows命令行中输入pip install chardet安装chardet模块。在vs code中打开一个.v文件,为此文件生成仿真的tb文件只需ctrl+shift+P输入testbench即可。

⑦安装indent-Rainbow插件,代码中对齐的空白部分会添加上颜色,变得更加显眼,方便查看对齐。

⑧安装local history插件,用于自动备份之前的改动,有时候仅凭Ctrl+z撤销操作时不行的,安装完成在左边侧栏显示有local history目录。

3.安装并配置ctags

本节介绍Ctags功能部署方法。

1.在插件介绍页进入ctags开源github仓库,找到与自己电脑环境相匹配的zip文件,我这里下载的是

ctags-2024-06-06_p6.1.20240602.0-4-g08e07dc-x64.zip

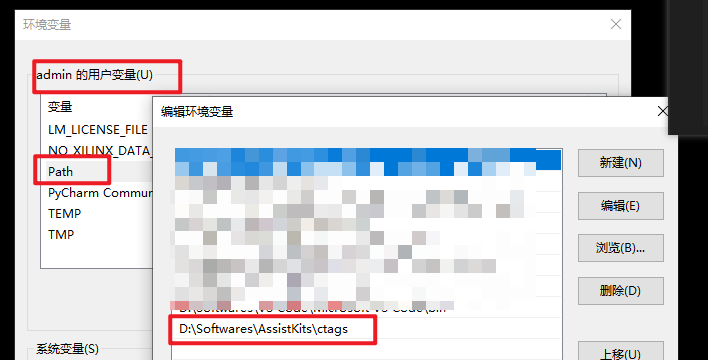

2.将解压后的ctags放在某个路径,并在用户变量,变量Path中新增环境变量。

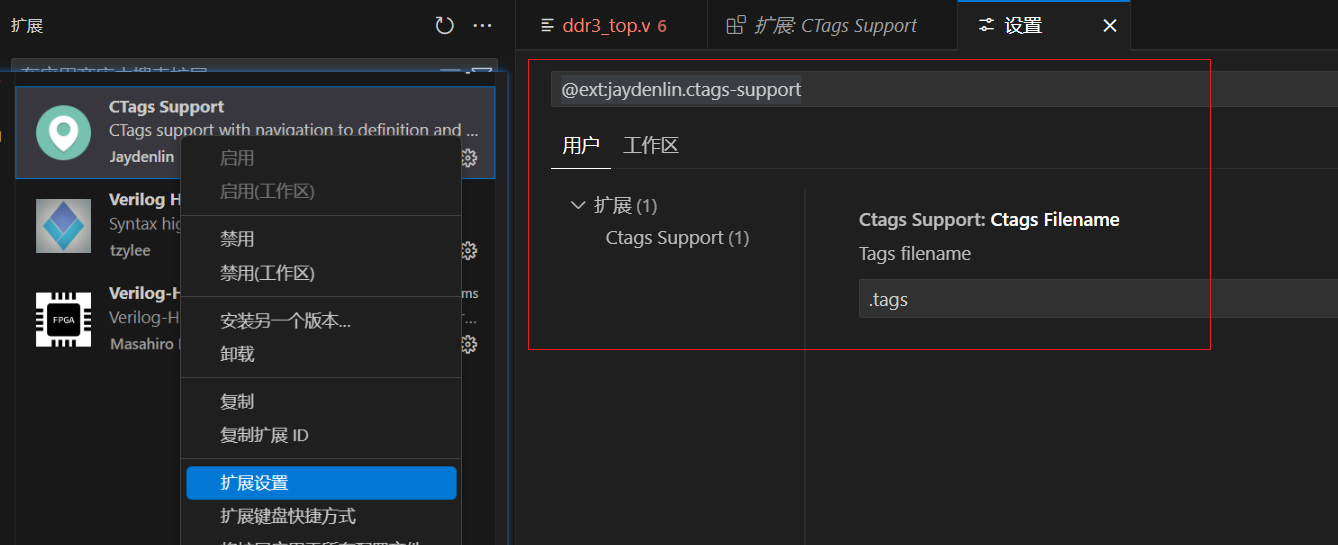

3. 在CTags-Support中做以下配置

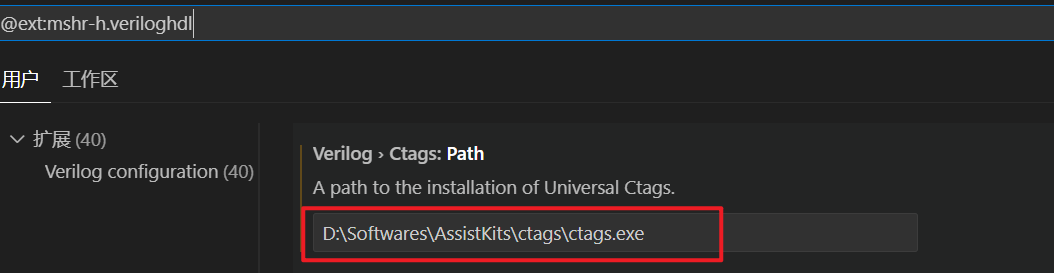

4.在Verilog-HDL插件中扩展设置中配置ctags路径如下

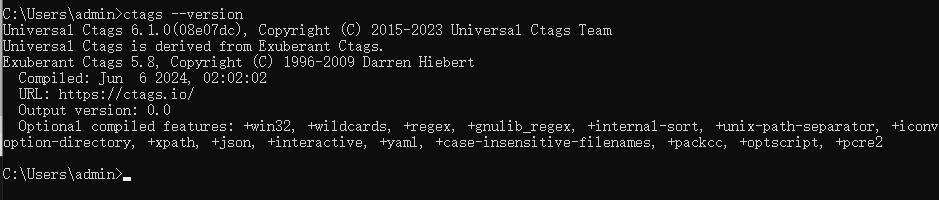

5.在windows命令行中输入ctags --verison,如果输出下图说明ctags配置就绪

4.安装iverilog语法检测工具

①访问iverilog官网下载Icarus Verilog,这里下载的是

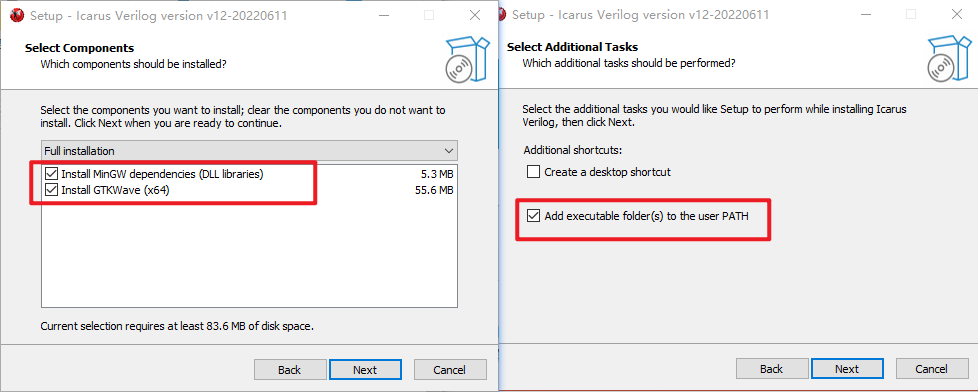

②安装过程中勾选(其余步骤省略)

注:杀毒软件可能会导致添加环境变量不成功,若未添加成功,可以手动添加即可。

C:\xxxxx\iverilog\bin (xxxxx 根据自己目录选择)

C:\xxxxx\iverilog\gtkwave\bin (xxxxx 根据自己目录选择)

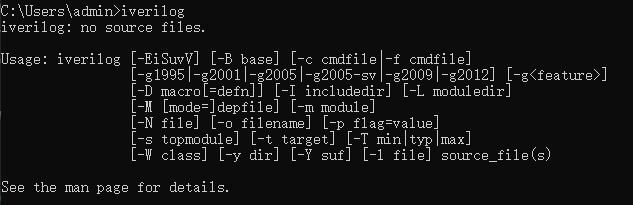

③打开CMD窗口,输入iverilog出现下图信息即为安装成功。

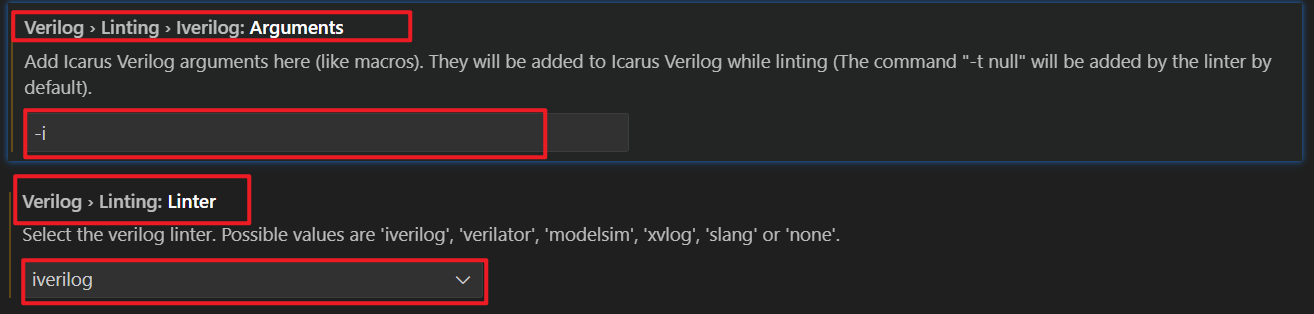

④打开已安装的Verilog-HDL插件,在扩展设置中进行如下两个配置,即完成iverilog的配置

5.VS Code与Vivado设置关联

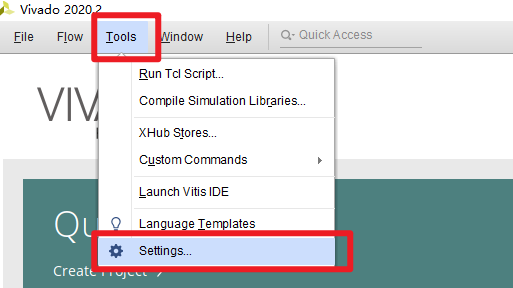

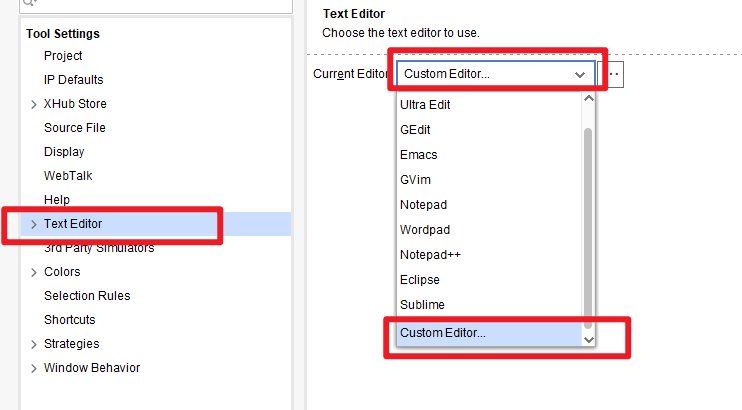

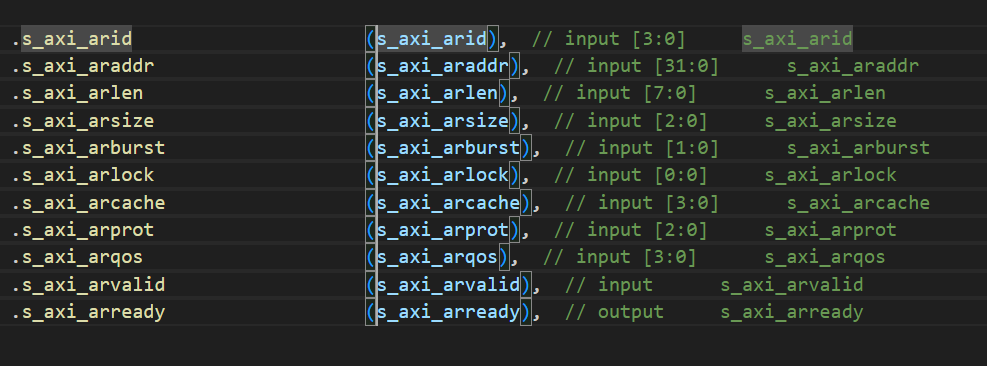

①打开vivado,单击tools-->选择settings

②单击"text editor",单击"箭头",选择"Custom Editor"进行自定义编辑器设置,然后单击省略号,配置编辑器的路径。

③双引号之内为编辑器的安装路径,其余部分照着写就ok。 注意这里必须全部是英文输入法下面的输入,否则会出错。

6.VS Code实用功能

①实际使用时,常常发现在vs或者notepad下编写的代码的中文注释在vivado编辑器中乱码,这是因为编码的问题,vs与notepad都是默认是UTF-8编码,vivado并不支持这一编码,因此在保存.v文件时,使用ANSI或者GBK编码保存即可解决这个问题。

②按住鼠标滚轮加右键可以实现竖行选择,这非常方便。

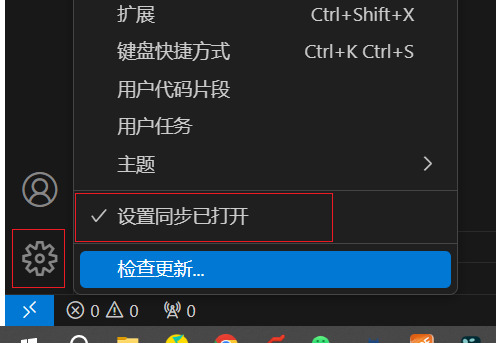

③使用账号登录VS Code可以同步本地的设置到其他主机

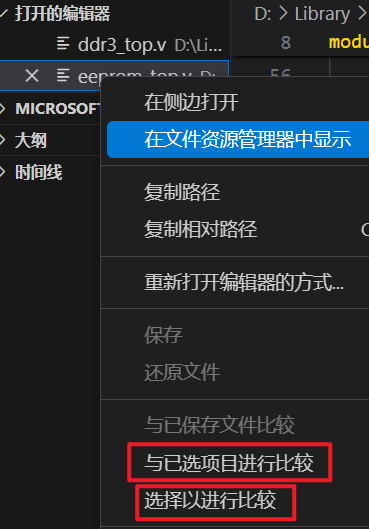

④vs code与beyond compare类似的对比功能,非常好用,如果要对比A、B两个文件,那先选择A文件右键选择“选择以比较”,然后选择B文件右键选择“与已选项目做对比”即可。

7.传送门

我的主页https://blog.csdn.net/weixin_40615338?type=blog

下一篇:FPGA开发技能(4)Vivado关联仿真ModelSim

END

💎文章原创,首发于CSDN论坛。

💎欢迎点赞💖收藏✨打赏💷!

💎欢迎评论区🎤或私信指出错误🎤,🗣️提出宝贵意见或疑问。

2459

2459

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?