目录

1.前言

在使用vivado烧写程序的时候,会遇到PCB上贴片的FLASH的型号不在vivado支持的flash列表中,导致无法烧写程序。Vivado的列表里只有几个常见大厂的芯片,例如镁光、issi等。在使用国内一些FLASH或者其他厂家的FLASH时往往找不到对应的器件型号。但是很多硬件工程师在做设计的时候并不会考虑vivado列表里有没有这个器件,他只会确认vivado支持该款FLASH。本文以华邦SPI FLASHW25Q128JVEIQ说明如何添加vivado列表中没有的器件并完成烧写。

2.了解FLASH命名规则

华邦winbond flash芯片按照W25Q xxx y z XX Y Z规范命名,以W25Q128 J V EI Q TR为例,其中

- ①xxx表示容量(单位 bit),比如 16表示 16Mbit(2Mbyte),256表示 256Mbit (32Mbyte),128表示128Mbit(16MB)

- ②y 表示第几代,按字母表顺序排列,比如 J 比 F的肯定要新,一般情况下,越新的支持的速度越高(J的速度一般都是133MHz,F的一般会在104MHz)。从winbond官网可知,最新的为 N。

- ③z表示器件的电压范围

- ⚪W:1.65/1,7V - 1.95V

- ⚪L:2.3V - 3.6V

- ⚪V:2,7V - 3.6V

- ⚪W:1.65/1,7V - 1.95V

- ④XX表示 封装类型

- ⚪SS = 8-pin SOIC 208-mil

- ⚪ZP = WSON8 6x5-mm

- ⚪XG = XSON 4x4x0.45-mm

- ⚪ SF = 16-pin SOIC 300-mil

- ⚪TB = TFBGA 8x6-mm (5x5 ball array)

- ⚪TC = TFBGA 8x6-mm (6x4 ball array)

- ⑤Z 表示特殊选项,意义不大

- ⑥有些型号会在后面有一个 DTR,他表示 Double Transfer Rate

- ⑦支持的SPI模式位宽x1_x2_x4

- ⚪TB = TFBGA 8x6-mm (5x5 ball array)

- ⚪ SF = 16-pin SOIC 300-mil

- ⚪XG = XSON 4x4x0.45-mm

- ⚪ZP = WSON8 6x5-mm

- ⚪SS = 8-pin SOIC 208-mil

- ⚪V:2,7V - 3.6V

- ⚪L:2.3V - 3.6V

- ⚪W:1.65/1,7V - 1.95V

3.添加Flash列表步骤

1.本地vivado安装目录...\Vivado\2020.2\data\xicom下,找到xicom_cfgmem_part_table.csv文件,这个表与vivado hardware manager中的器件一致。将该flash器件添加进表格即可。

2.表格表头含义,没提到的不用关注。

- CFGMEM_ID:序号

- NAME:为添加项起名字

- COMPATIBLE_DEVICES:兼容的FPGA型号

- MEM_DEVICE:芯片名称

- MEM_TYPE:芯片类型,spi/bpi,nand flash(手册中有)

- MEM_DENSITY:芯片容量

- DATA_WIDTH:接口支持位宽

- MEM_MANUFACTURER:芯片制造厂商

- DATA_WIDTH:接口支持位宽

- MEM_DENSITY:芯片容量

- MEM_TYPE:芯片类型,spi/bpi,nand flash(手册中有)

- MEM_DEVICE:芯片名称

- COMPATIBLE_DEVICES:兼容的FPGA型号

- NAME:为添加项起名字

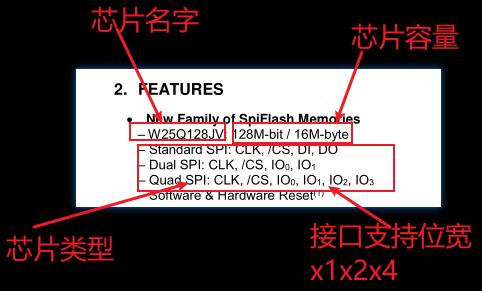

3.在芯片手册中查找各表头要求填写的信息。序号、添加项名字自己搞定,兼容的FPGA型号看自己的需求,其余项如下图所示,截取自winbond W25Q128JV datasheet。

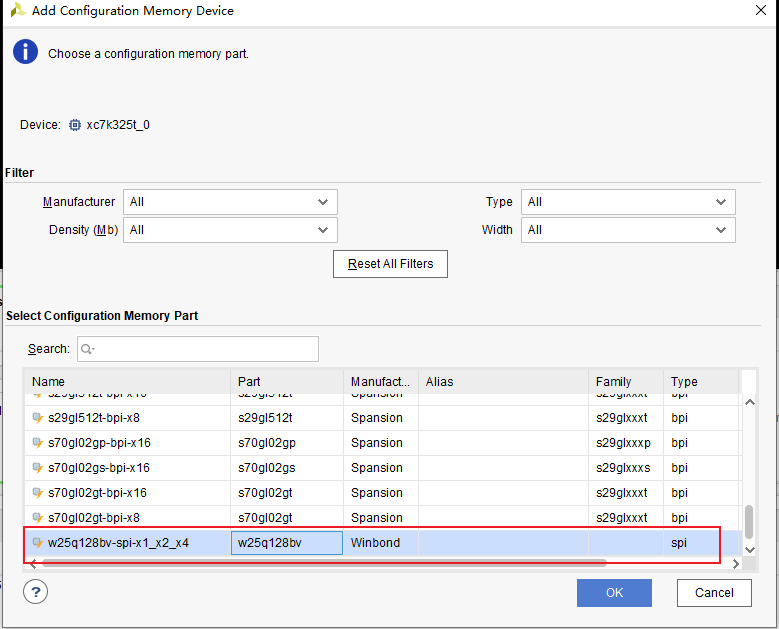

4.将上述表头填写完整保存excel表格并替换原有表格,重新打开vivado hardware manager,选择添加存储器件,可以看到,新加入表格的华邦Flash已经可以添加了。

4.传送门

我的主页https://blog.csdn.net/weixin_40615338?type=blog

上一篇:FPGA开发技能(4)Vivado关联仿真ModelSim

下一篇:FPGA开发技能(6)Qt生成ROM IP核使用的COE文件

END

💎文章原创,首发于CSDN论坛。

💎欢迎点赞💖收藏✨打赏💷!

💎欢迎评论区🎤或私信指出错误🎤,🗣️提出宝贵意见或疑问。

7787

7787

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?