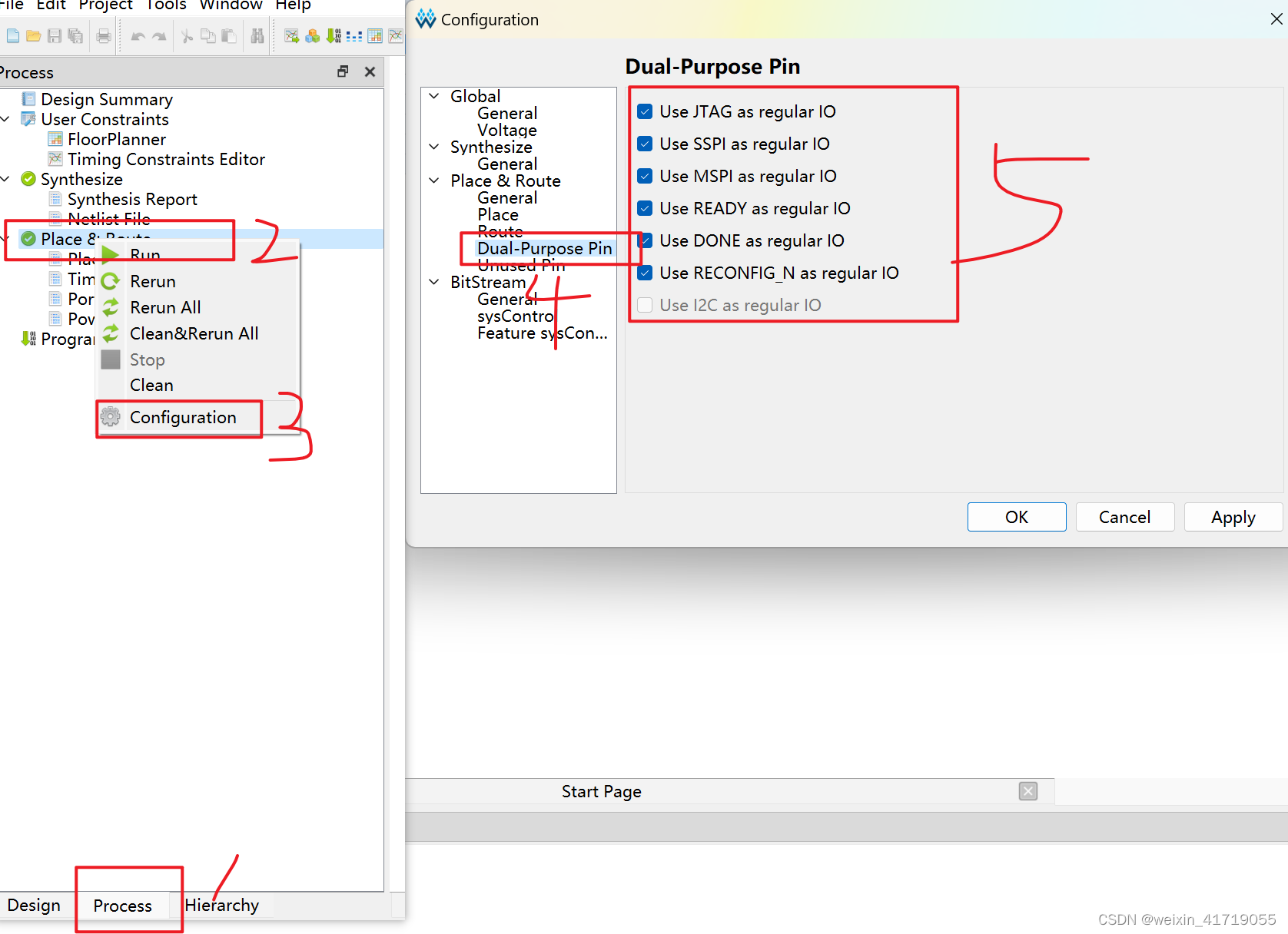

1、管脚复用

根据自己需求把复用管脚勾选上,管脚当普通管脚使用

JTAG设置成普通管脚,下载程序时候JTAGEN管脚需要上拉高电平(可以在下载器线上上拉个电阻,下载后把下载线拔走,否则JTAG管脚无法使用,管脚充裕最好不使用JTAG)

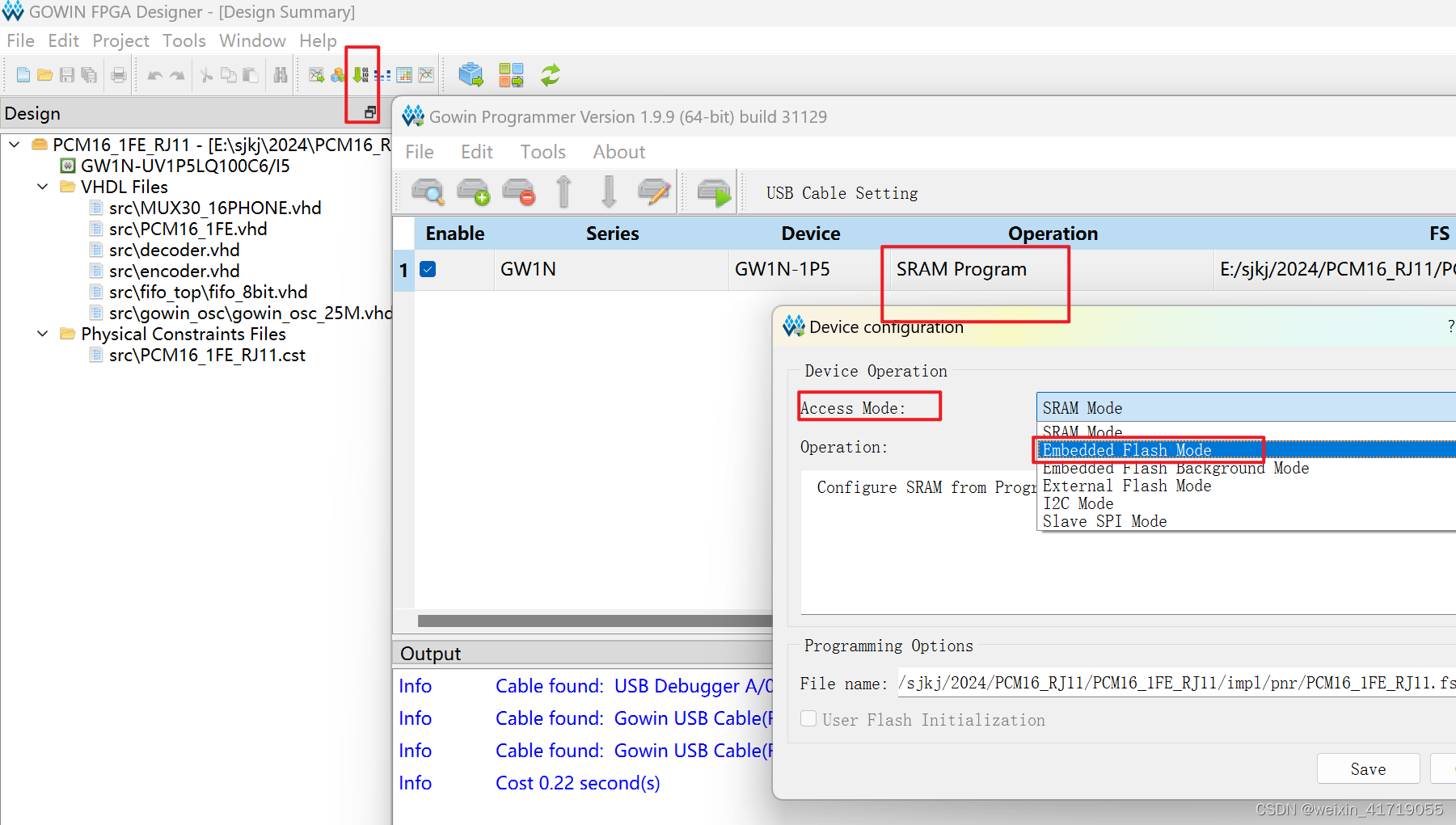

2、程序下载

下载Access Mode选择默认是SRAM,这下载是程序立即被启用,设备重启这程序会失效,主要测试时候使用。有重启操作程序下载到Flash中

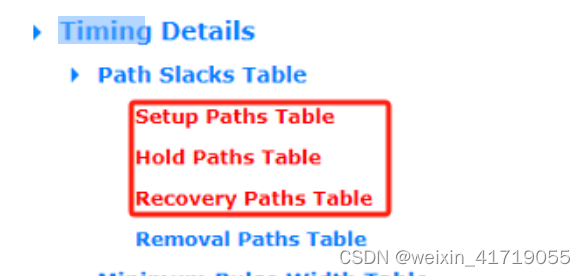

3、时序约束

最近使用GWINR-9芯片做项目,逻辑单元用到80%以上,下图红框显示告警,红色的

刚开始没搭理(以前做的都是低速的,资源充足,不影响业务) ,调试几天业务一直不正常,没辙,排除法。先把报警的解决。

问了高云技术支持,出现跨时钟域了,让加时序约束,抓瞎,以前没约束过。还好技术提供文档,谢谢!!。

时序约束主要约束时钟频率和不同时钟关系,跨时钟域主要是不同时钟域间的信号传递,编译时软件认为时钟间有关联。(我的理解,哈哈)

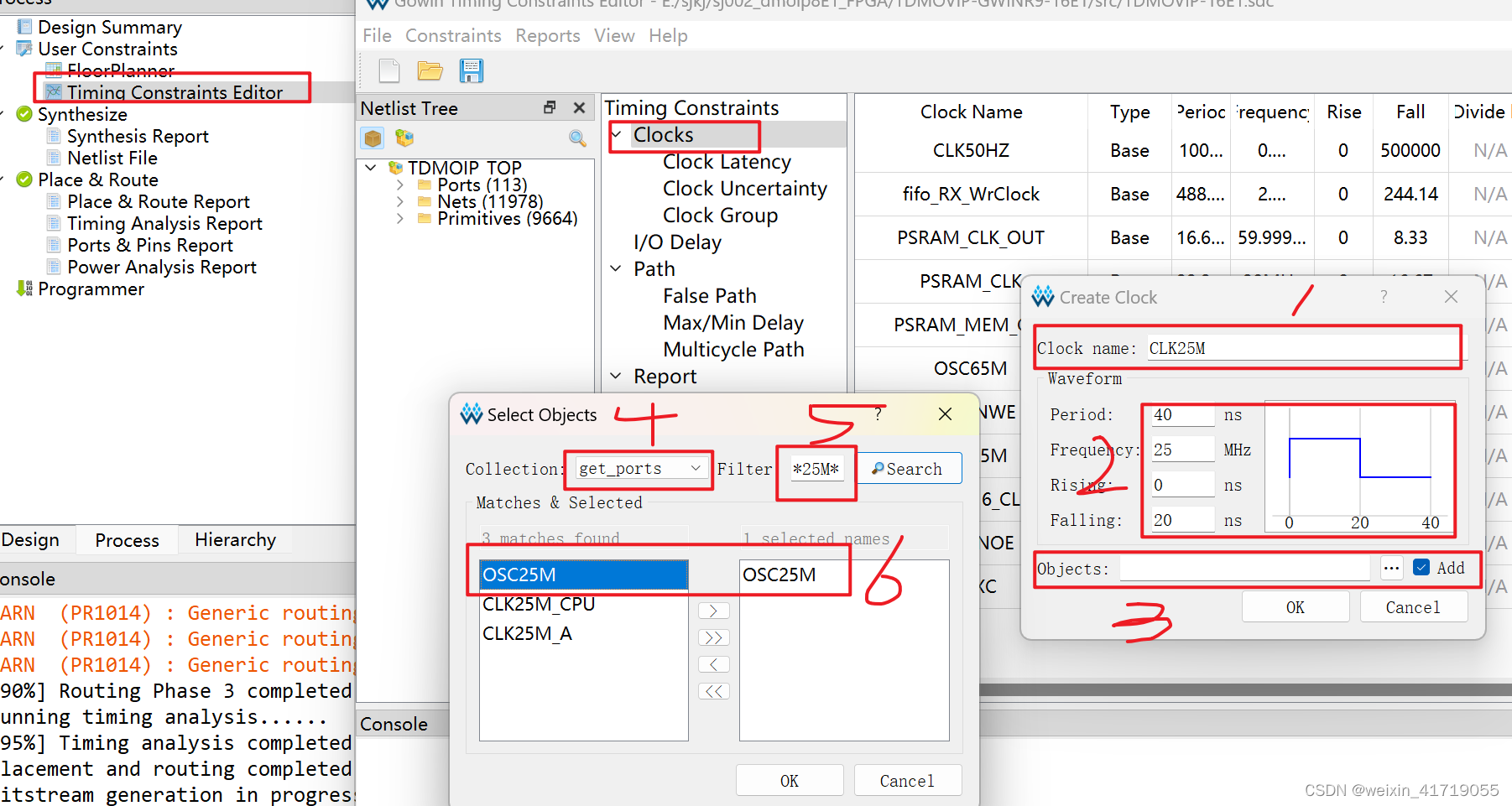

①编译完进入配置界面,后右击选择Create Clock,时钟频率约束,

在1填个方便记忆的名称,2选择大概的时钟频率(可以不准,可以比实际大,但不要比实际小很多),3点击...出现选择框,选择实际信号。

4选择信号类型,芯片管脚选get_ports,其他选择get_nets,在5填信号在程序中具体名称查找到后执行6,然后OK。时钟频率约束好了

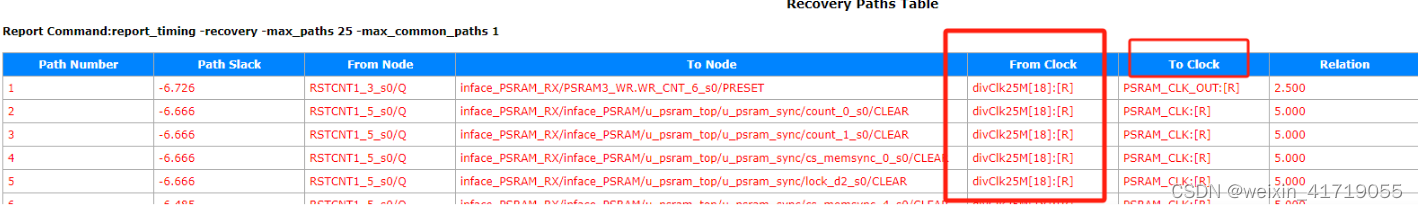

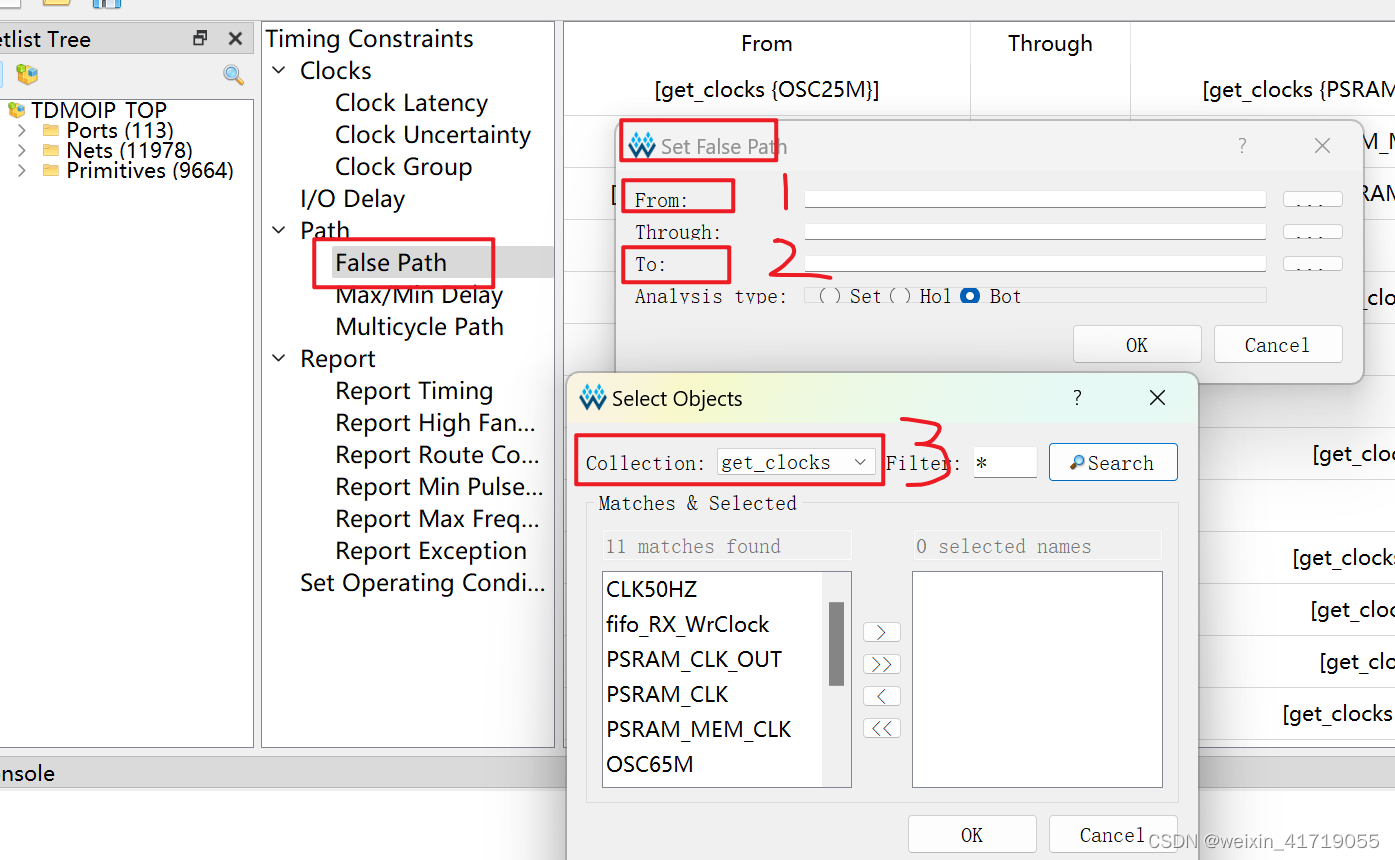

②时钟关系约束

点击false Path后在右边右击出现set false Path. 1与2后面...选择需要配置的时钟(直接用上面约束的时钟就可以)

理解:to时钟是from时钟衍生的或有紧密关系的,

设备晶振输入时钟CLK25M,可以在from不选,在to选择CLK25M,这样其他时钟就不会影响CLK25M时钟

设备计数复位时钟CLK50HZ,只有from,没有to,可以from选择CLK50HZ,to不选,这样CLK50HZ不会影响其他时钟

4、 GWINR-9中PSRAM的IP核使用

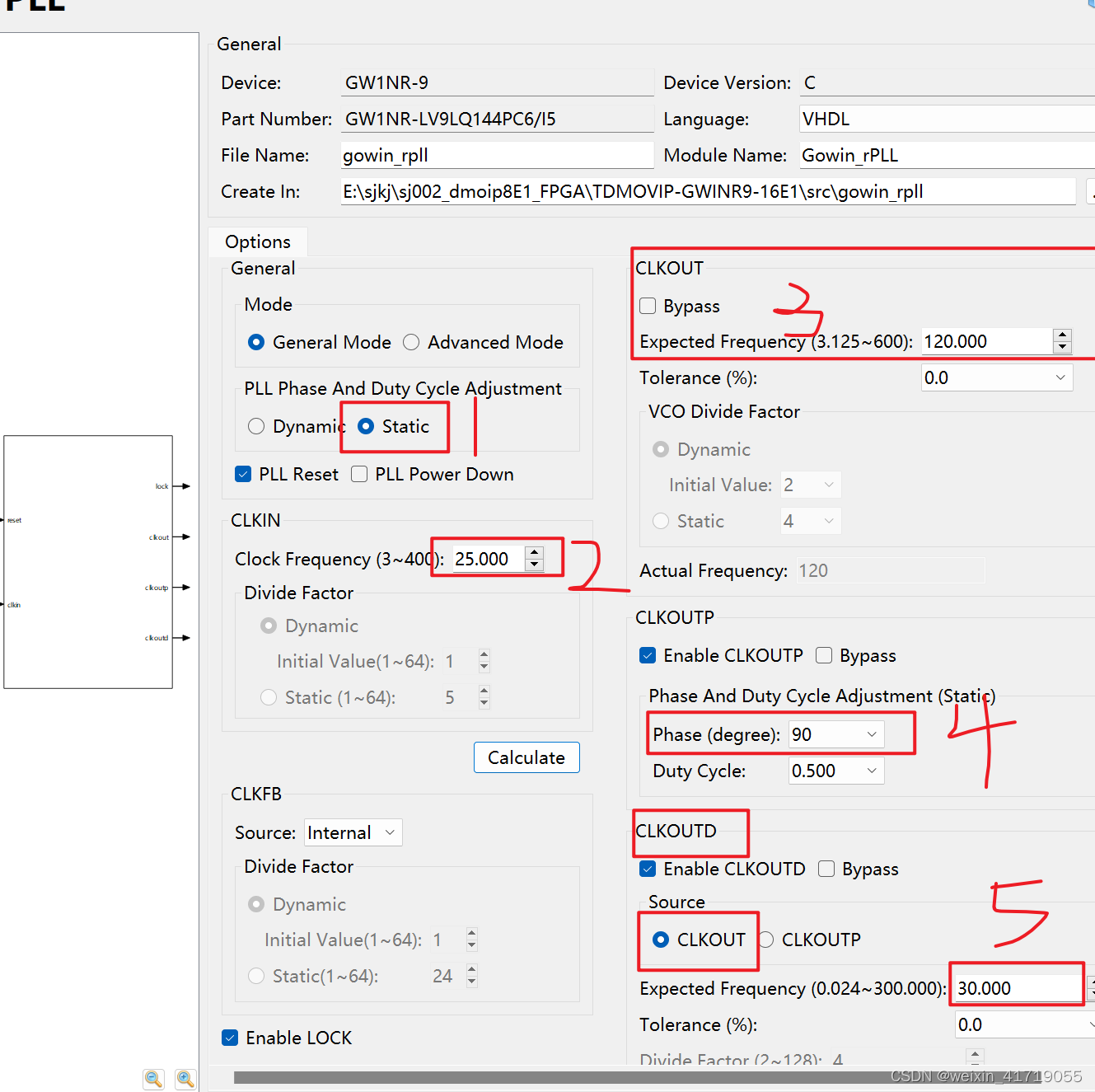

给PSRAM核时钟,4中选择90,不能错。3中CLKOUT是PSRAM核中操作SRAM的时钟,5中CLOCKD是业务逻辑使用时钟

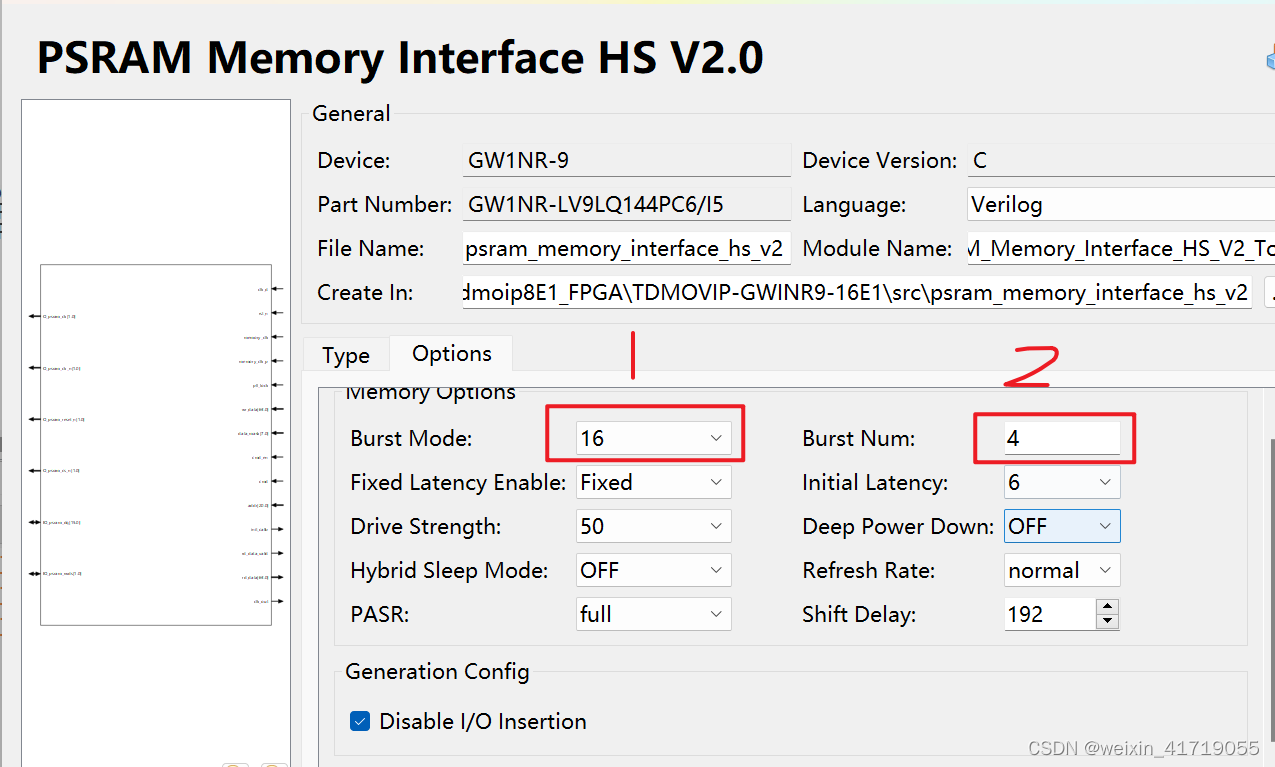

PSRAM的IP核:1默认是32根据自己需求,我这选择16,Burst Num自动变成4,意思一次写4个数据(4*数据宽度64bit)

问题:①地址+2(一个数据占2个地址,PSRAM中有2个颗粒)读写数据,连续读4个数据一样的,与写入数据不符

原因:burst Num是4,一次最少写4个数据,地址0写有效,2、4、6写无效。所以连续4个数据一样。(读可以+2读,但是读出来数据是4个,只是我这用第1个)

问题:②做个fifo,时钟1往里面写数据,时钟2读出数据做其他用,fifo一会出现空一会满现象,乱跳。

原因:时钟1和时钟2与PSRAM的IP核时钟域不一样,获取读写信号获取错误。

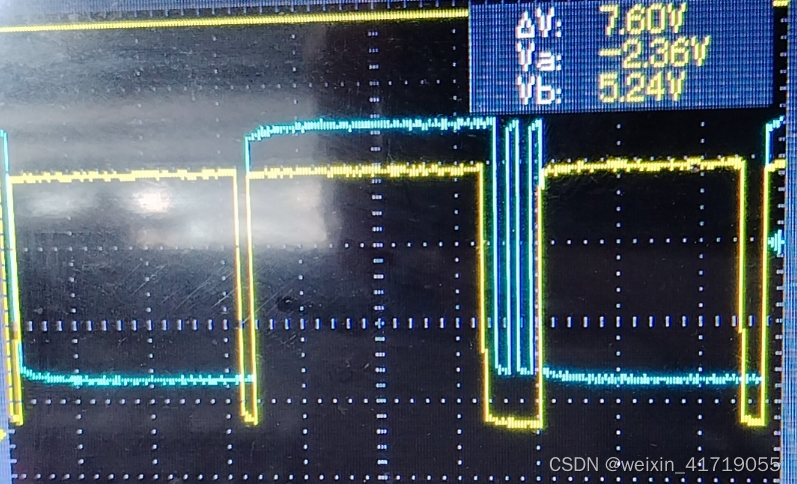

下图:时钟2读写操作:黄色是半空标志,出现后需要从PSRAM读数据,蓝色电平变换1次表示读出1个数据。正常应该是半空标志出现读1个数据,成功后半空标志消失,但是时钟2与PSRAM的IP核不在一个时钟域中,信号出现亚稳态

亚稳态产生消除: 亚稳态的产生机理、消除办法_亚稳态产生的原因及消除方法-CSDN博客

刚开始认为亚稳态是个斜线,造成影响只是获取信号可以比预期的快或慢一个周期,不会影响现在业务判断,现在发现亚稳态是波浪形的,不同时钟域采集肯定出问题

解决方法:fifo读写操作直接使用PSRAM的IP核同样时钟域时钟(rppl输出的CLKOUTD做读写需求判断,PSRAM接口输出的CLKOUT/2做具体读写操作)

5、高云IP核修改

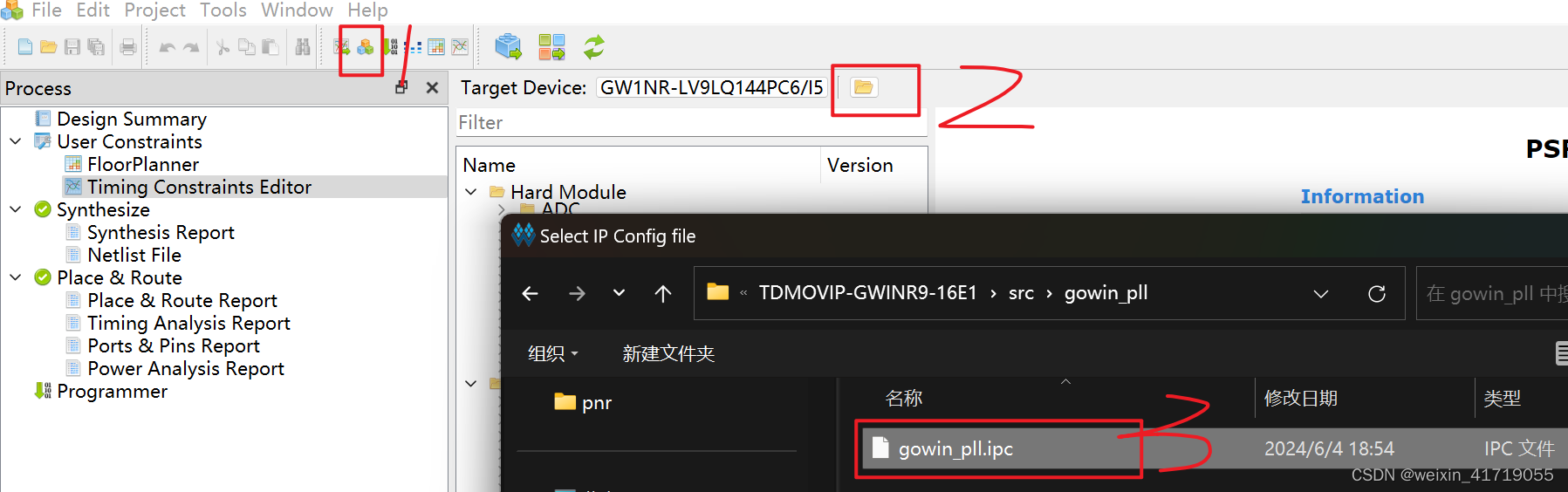

一直以为高云IP核配置好后,没修改功能,只能重新生成替换,每次查找*.ipc文件,按照里面参数重新生成一个IP。最近找到资料,是可以的!!按123步骤打开需要修改的IP核修改就可以

6、license到期更新:双击安装目录中的license_config_gui.exe

F:\Gowin\Gowin_V1.9.9_x64\IDE\bin\license_config_gui.exe

2023

2023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?