一个简单的状态机设计--序列检测器

序列检测器的逻辑功能描述:序列检测指的就是将一个指定的序列从数字码流中识别出来。本例中,我们将设计一个“10010”序列的检测器。设X为数字码流输入,Z为检出标记输出,高电平表示“发现指定序列”,低电平表示“没有发

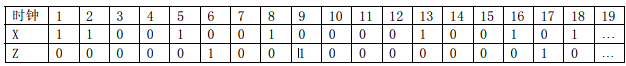

现指定序列”。考虑码流为“ 110010010000100101…” 则有下表:

在时钟2-6,码流X中出现指定序列“10010”,对应输出Z在第6个时钟变为高电平――“1”,表示“发现指定序列”。同样地,在时钟13-17码流,X中再次出现指定序列“10010”,Z输出“1”。注意,在时钟5-9还有一次检出,但它是与第一次检出的序列重叠的,即前者的前面两位同时也是后者的最后两位。

根据以上逻辑功能描述,我们可以分析得出状态转换图如下:

其中状态A-E表示5比特序列“10010”按顺序正确地出现在码流中。考虑到序列重叠的可能,转换图中

还有状态F、G。另外、电路的初始状态设为IDLE。

Verilog HDL代码。

module seqdet( x, z, clk, rst);

input x,clk, rst;

output z;

reg [2:0] state;//状态寄存器

wire z;

parameter IDLE= 'd0, A='d1, B='d2,

C='d3, D='d4,

E='d5, F='d6,

G='d7;

assign z=(state==D && x==0) ? 1 :0;

always @(posedge clk or negedge rst)

if(!rst)

begin

state<=IDLE;

end

else

casex( state)

IDLE: if(x==1)

begin

state<=A;

end

A: if (x==0)

begin

state<=B;

end

B: if (x==0)

begin

state<=C;

end

else

begin

state<=F;

end

C: if(x==1)

begin

state<=D;

end

else

begin

state<=G;

end

D: if(x==0)

begin

state<=E;

end

else

begin

state<=A;

end

E: if(x==0)

begin

state<=C;

end

else

begin

state<=A;

end

F: if(x==1)

begin

state<=A;

end

else

begin

state<=B;

end

G: if(x==1)

begin

state<=F;

end

default: state<=IDLE;

endcase

endmodule

测试用代码。

`timescale 1ns/1ns

module t;

reg clk, rst;

reg [23:0] data;

wire z,x;

assign x=data[23];

initial

begin

clk<=0;

rst<=1;

#2 rst<=0;

#30 rst<=1; //复位信号

data='b1100_1001_0000_1001_0100; //码流数据

end

always #10 clk=~clk; //时钟信号

always @ (posedge clk) // 移位输出码流

data={data[22:0],data[23]};

seqdet m ( .x(x), .z(z), .clk(clk), .rst(rst)); //调用序列检测器模块

// Enter fixture code here

endmodule // t

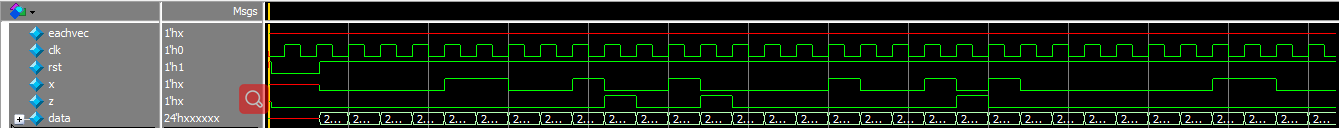

这是用modelsim做的仿真,和功能一样

这是用modelsim做的仿真,和功能一样

585

585

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?