代码如下:

class ctrl_reg extends uvm_reg;

`uvm_object_utils(ctrl_reg)

uvm_reg_field reserved;

rand uvm_reg_field pkt_len;

rand uvm_reg_field prio_level;

rand uvm_reg_field chnl_en;

...

virtual function void build();

...

//所在寄存器、field位宽、该filed的最低位在寄存器中的位置、该field的存取属性、是否是易失的(volatile)、复位值、该field是否有复位

//该field是否可随机化、该field是否可单独存取

reserved.configure(this, 26, 6, "RO", 0, 26'h0, 1, 0, 0);

pkt_len.configure(this, 3, 3, "RW", 0, 3'h0, 1, 1, 0);

prio_level.configure(this, 2, 1, "RW", 0, 2'h3, 1, 1, 0);

chnl_en.configure(this, 1, 0, "RW", 0, 1'h1, 1, 1, 0);

...

endfunction

...

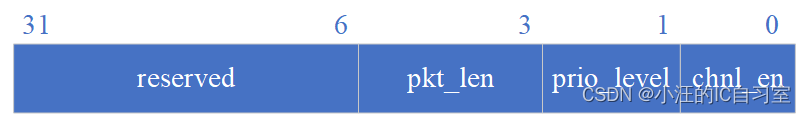

endclass对应寄存器如下所示:

单拎出来一个域 configure() 进行说明,其余相同:

pkt_len.configure(this, 3, 3, "RW", 0, 3'h0, 1, 1, 0);

configure() 函数参数列表说明如下:

- configure的第一个参数就是此域(uvm_reg_field)的父辈,也即此域位于哪个寄存器中,这里当然是填写this了。

- 第二个参数是此域的宽度,由于控制寄存器的pkt_len的域宽度是3,这里填写3。

- 第三个参数是此域的最低位在整个寄存器中的位置,从3开始计数。

- 第四个参数表示此字段的存器方式。UVM共支持25种存取方式:这里只列举常用的几种:

-

- WO(write-only,只写);

- RO:(read-only,只读);

- RW(read and write,读写);

- RC(clean-on-read,擦除模式);写入时无影响,读取时会清零

- …

- 第五个参数表示是否是易失的(volatile),这个参数一般不会使用。

- 第六个参数表示此域上电复位后的默认值。

- 第七个参数表示此域是否有复位,一般的寄存器或者寄存器的域都有上电复位值,因此这里一般也填写1。

- 第八个参数表示这个域是否可以随机化。这主要用于对寄存器进行随机写测试,如果选择了0,那么此域将不会随机化,而一直是复位值,否则将会随机出一个数值来。这个参数仅当第四个参数为RW、WRC、WRS、WO、W1、WO1时才有效。

- 就九个参数表示这个域是否可以单独存取。

2013

2013

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?