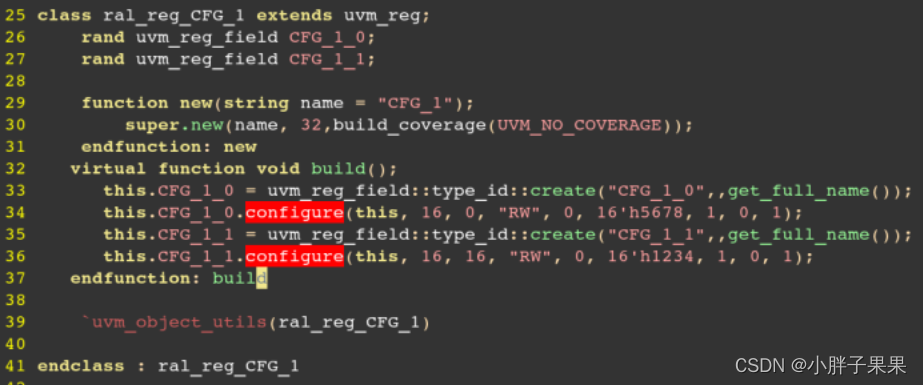

通常情况下,uvm_reg_model是uvm_reg集合,uvm_reg简单的示例如下所示:

其中uvm_reg_field是寄存器内的域,在ral_reg_CFG_1内包含两个域,分别为CFG_1_0和CFG_1_1。其中,configure函数对域进行配置:

function void configure(

uvm_reg parent, //指示field的parent uvm_reg

int unsigned size, //指示field的bit size

int unsigned lsb_pos, //指示该field的最低bit在uvm_reg的bit位置

string access, //指示access策略,包括“RW”、“RO”等

bit volatile, //

uvm_reg_data_t reset, //硬复位值

bit has_reset, //指示该字段是否确实会复位,如果为0则忽略复位值

bit is_rand, //指示该字段是否可以随机化

bit individually_accessible //指示该字段是否为唯一占用该字段

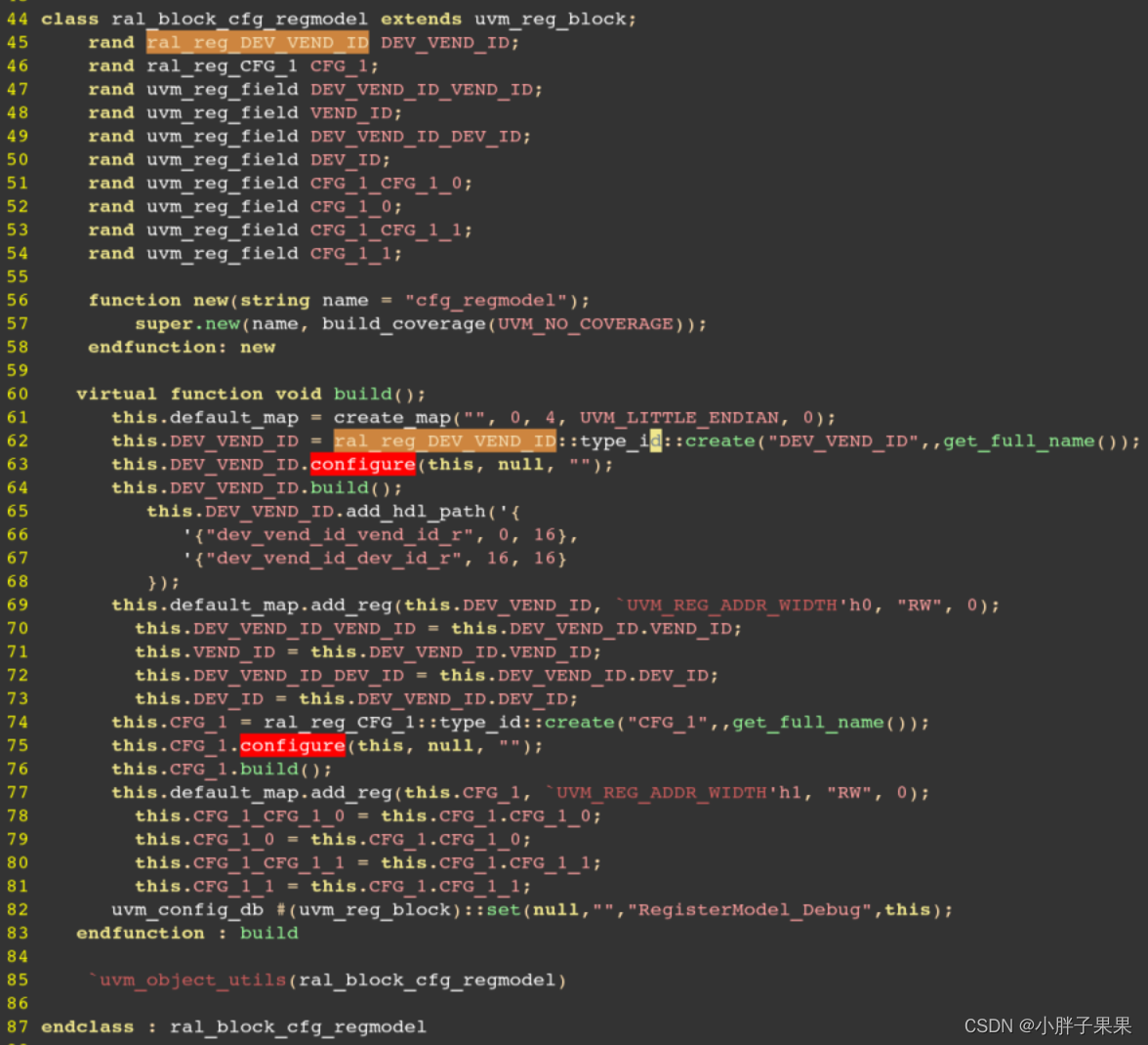

) 一个简单的reg_model如下所示:

create_map的函数原型如下所示,其功能是创建一个map。

virtual function uvm_reg_map create_map(

string name, //map名

uvm_reg_addr_t base_addr, //map基地址

int unsigned n_bytes, //总线byte宽度

uvm_endianness_e endian, //指示字节排序格式

bit byte_addressing = 1 //地址递增方式是按照字节(1)还是按照n_bytes(0)

)uvm_reg的configure函数原型如下,设置了uvm_reg所属于的uvm_reg_block和uvm_reg_file;以及设置hdl路径;

function void configure (

uvm_reg_block blk_parent, //寄存器所属于的uvm_reg_block

uvm_reg_file regfile_parent = null, //寄存器所属于的uvm_reg_file

string hdl_path = "" //指示DUT路径

)uvm_reg的add_hdl_path函数原型如下,设置uvm_reg_field的路径;

function void add_hdl_path (

uvm_hdl_path_slice slices[], //指示uvm_reg_field rtl路径

string kind = "RTL"

)uvm_reg_map的add_reg函数原型如下:

virtual function void add_reg (

uvm_reg rg, //添加的寄存器

uvm_reg_addr_t offset, //地址偏移

string rights = "RW", //map指定该reg的访问权限

bit unmapped = 0, //若为1则表示该寄存器不占用物理地址

uvm_reg_frontdoor frontdoor = null

)

1212

1212

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?