1- 前言

📓 记录IC后仿的流程与注意事项

2- 后仿运行前

后仿前期准备 库文件、网表、sdf、makefile

1️⃣库文件,网表更新在filelist中

##库文件

/home/xx/xx.v

##网表文件

/home/xx/xx.v

2️⃣ SDF文件反标在dut_top中

...

initial begin

$sdf_annotate ("/home/xx/post_sim/Digital_top_worst.sdf",dut,,"worst_sdf.log","MAXIMUM","1.0:1.0:1.0",);

end

Digital_top dut(

/*input */ .clk (clk ),

/*input */ .por_rst (rstb ),

...

-

$sdf_annotate是 Verilog 的系统任务,专门用于加载 SDF 文件中的时序信息。这些时序信息包括路径延迟、建立时间、保持时间等,通常用于后仿真;$sdf_annotate("①sdf_file.sdf", ②dut_instance, ③NULL, ④"sdf_annotation.log", ⑤"MINIMUM", ⑥"1.0:1.0:1.0", ⑦"1.0:1.0:1.0");$sdf_annotate的6个参数:1、SDF文件路径;

2、 模块实例名;

3、 标志位(Optional, NULL 默认),写作

NULL,表示不对SDF指定任何特殊操作;4、 日志文件路径,记录反标是否成功;

5、 延迟模式(Optional,默认是TYPICAL):SDF 文件中的延迟通常包含三类:

"MINIMUM":最小延迟值。

"TYPICAL":典型延迟值(默认值)。

"MAXIMUM":最大延迟值6、 比例因子(Optional,默认是1.0:1.0:1.0);

7、延迟标志(Optional, 1.0:1.0:1.0 默认);

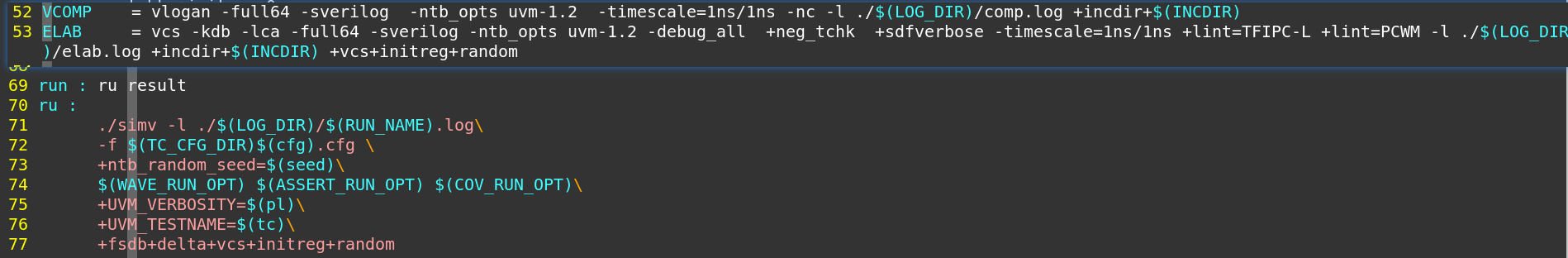

3️⃣增加Makefile选项(以verdi为例)

1、编译和仿真阶段都要加上+vcs+initreg+random1

2、编译阶段加上 +neg_tchk +sdfverbose

+neg_tchk negative timing check是一个在仿真过程中控制负时序检查的选项,允许仿真器忽略负的时序检查结果,从而减少不必要的警告或错误

+sdfverbose 用于在 SDF 文件注释过程中提供更详细的信息输出

3- 后仿运行中

通过运行make run tc=xx等命令运行前仿时的testcase;

🤔前仿/后仿共用同一套testbench和testcase时,一定要注意以下问题:

- TB所有变量声明后给上初值;

- TB/TC所有的信号驱动由interface clock blocking 驱动;

- 所有dut intput 在TB连接时,给初值,不要floating;

4- 后仿运行后

运行后,主要任务为分析结果,确定是否存在x态,追踪产生原因。

⭐️在后仿中产生x态的主要原因:

-

建立/保持时间不符合要求;

-

DUT 输入端口没有赋初始值(floating状态/Z高阻态),Z经过触发器输出X ;

-

寄存器初始化未成功;

https://blog.csdn.net/qq_16423857/article/details/122649458 ↩︎

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?