7系列FPGA IOB

1 7系列FPGA IOB

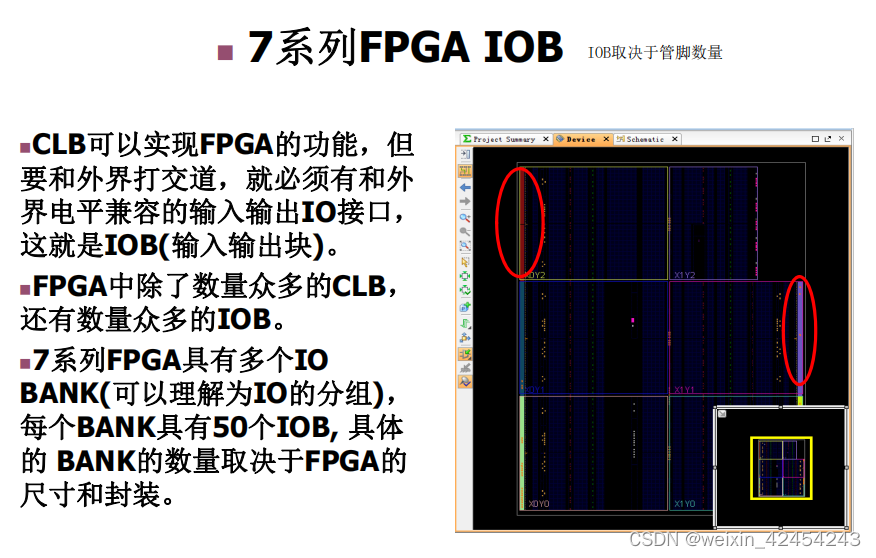

CLB可以实现FPGA的功能,但要和外界打交道,就必须有和外

界电平兼容的输入输出IO接口,这就是IOB(输入输出块)。

FPGA中除了数量众多的CLB,还有数量众多的IOB。

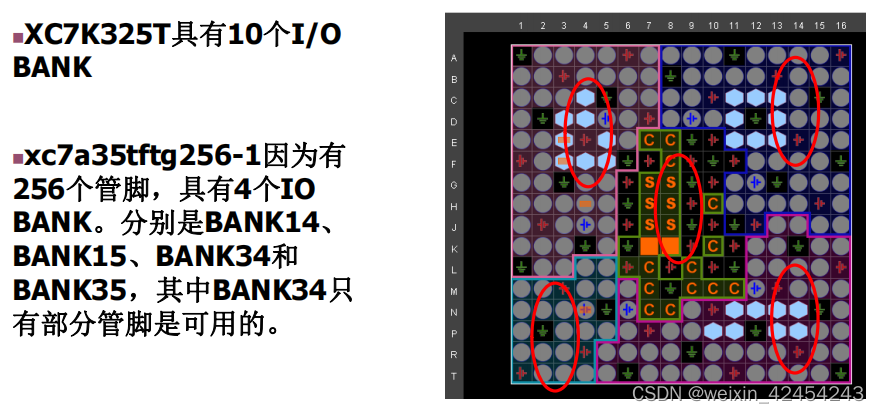

7系列FPGA具有多个IO BANK(可以理解为IO的分组),每个BANK具有50个IOB, 具体的 BANK的数量取决于FPGA的尺寸和封装

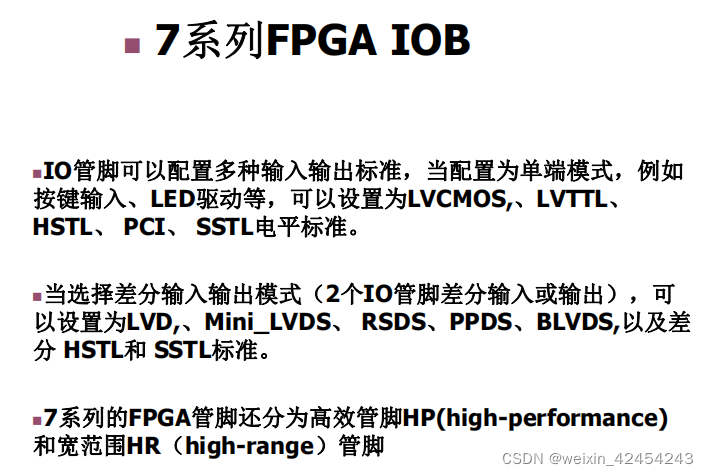

IO管脚可以配置多种输入输出标准,当配置为单端模式,例如

按键输入、LED驱动等,可以设置为LVCMOS,、LVTTL、

HSTL、 PCI、 SSTL电平标准。

当选择差分输入输出模式(2个IO管脚差分输入或输出),可

以设置为LVD,、Mini_LVDS、 RSDS、PPDS、BLVDS,以及差

分 HSTL和 SSTL标准。

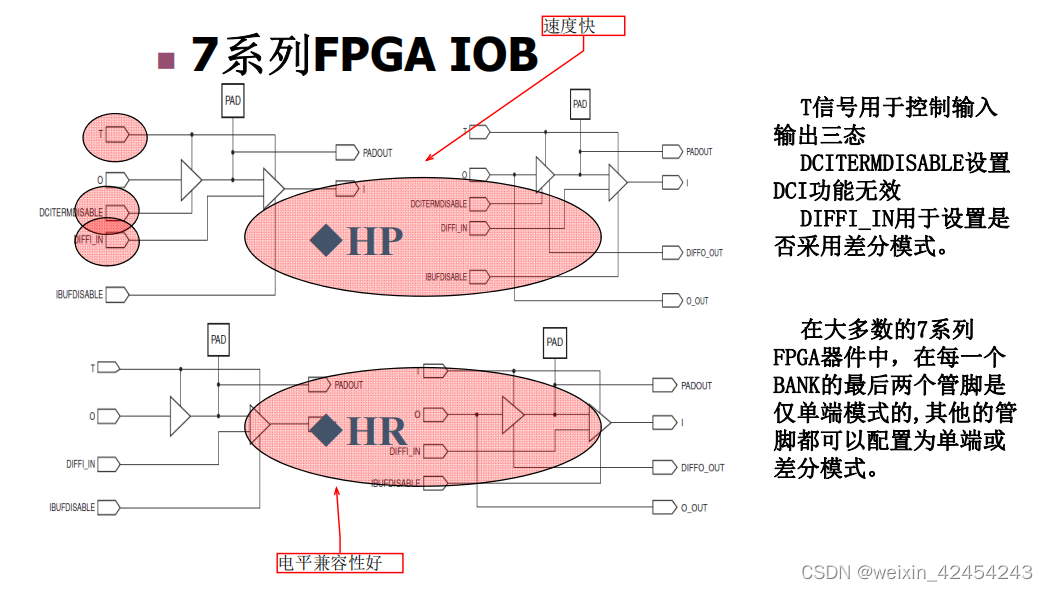

7系列的FPGA管脚还分为高效管脚HP(high-performance)

和宽范围HR(high-range)管脚。

2 IOB的约束方法

为了保证FPGA输入输出接口的时序,一般会要求将输入管脚首先打一拍再使用,输出接口也要打一拍再输出FPGA。这样做的目的是为了让这打一拍的寄存器约束到IOB上,从而使得每一次编译输入或者输出的时序不会发生改变。这是因为,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,并且位置固定。当你输入或者输出采用了IOB约束,那么就可以保证从IO到达寄存器或者从寄存器到达IO之间的走线延迟最短、最大限度保证时序满足要求,同时由于IO的位置是固定的,所以每一次编译都不会造成输入或者输出的时序发生改变。

IOB的应用一般有两种,一种是在代码中添加约束,另一种可以在约束文件xdc中添加。

在约束文件中加入下面约束:

set_property IOB true [get_ports {port_name}]

直接在代码中加约束,在寄存器前加入下面约束,需要注意的是,对于输入IOB约束,这里的寄存器是第一级寄存器,对于输出IOB约束,这里的寄存器是最后一级寄存器,且寄存器输出不能再作为组合逻辑输入。

(* IOB = "true" *) reg O_data;

3 IOB约束使用注意事项

对于输出IOB约束,在使用的时候有一些限制:

1、约束的端口必需是寄存器输出,这点比较好理解,因为IOB约束本质上是约束最后一级寄存器的位置,将最后一级寄存器的位置放在IOB上,而不是增加一级寄存器。所以你必须要是寄存器输出,才能进行IOB约束,这是前提。

2、最后一级寄存器的输出不能再作为输入反馈到内部逻辑中,必需是开路的。举个例子,比如如下代码:

always @ (posedge clk)

begin

if(cnt == 2'b1 || cnt == 2'b3)

spi_clk <= ~spi_clk;

else

spi_clk <= spi_clk;

end

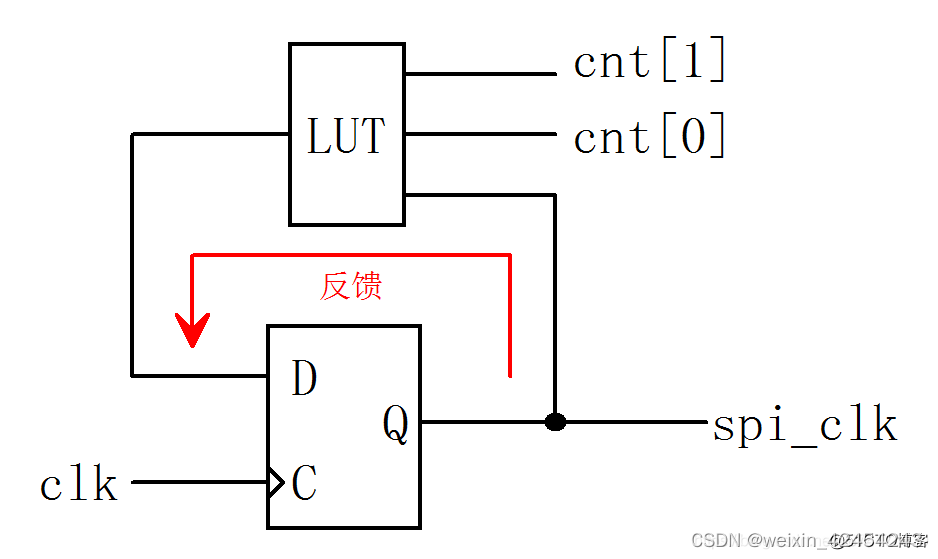

上面描述了一个分频器,当计数器cnt为1和3的时候spi_clk翻转,那这个时候spi_clk就是一个输出又作为输入反馈到内部的寄存器,得到的综合结果如下图:

由于需要将寄存器的输出作为输入其他逻辑的输入,这种情况下是无法将spi_clk寄存器放到IOB上的,因为IOB的输出直接对接IO,无法再作为输入反馈到内部逻辑。

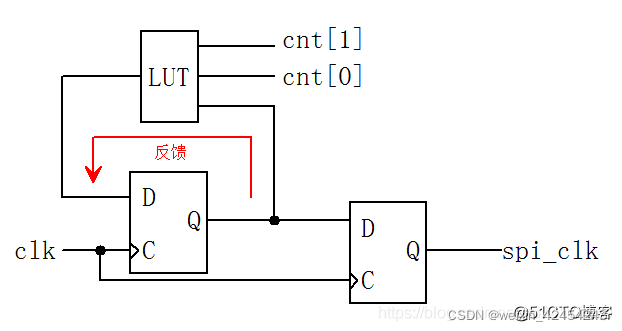

所以可以将spi_clk输出再加一级寄存器,将加入的寄存器放到IOB上,相应的需要对时序做出一定的调整,和sip_clk有时序关系的都需要打一拍以保持同步。

1242

1242

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?