本篇博文讲了三个内容:时序约束基本概念、时序约束命令、时序收敛技巧

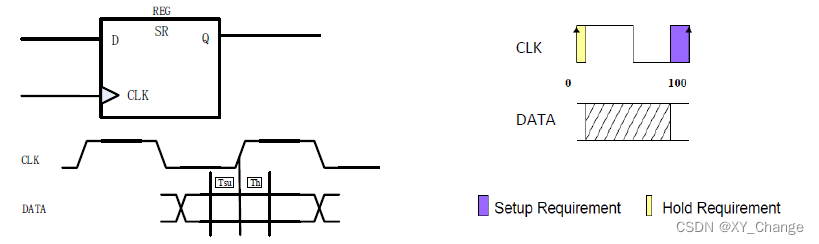

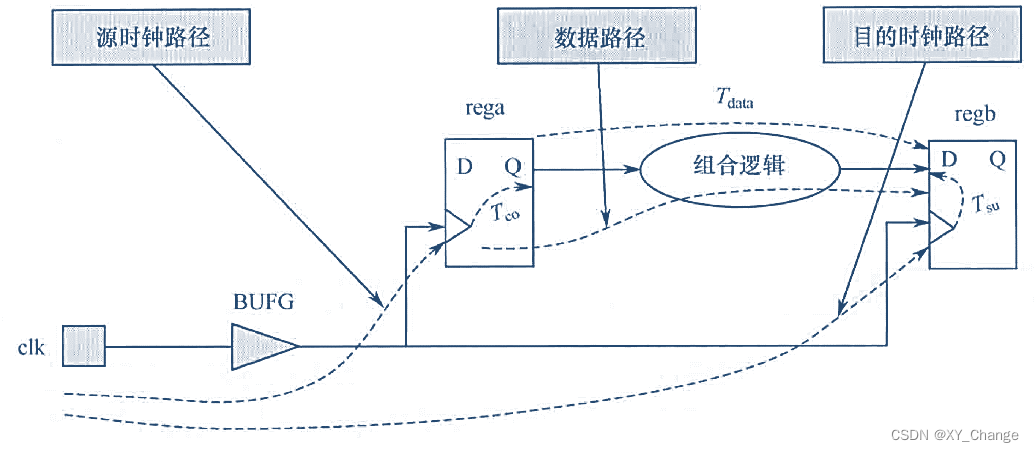

那么当使用FPGA开发软件时,时序报告的建立保持时间余量是如何计算的呢?见下图:

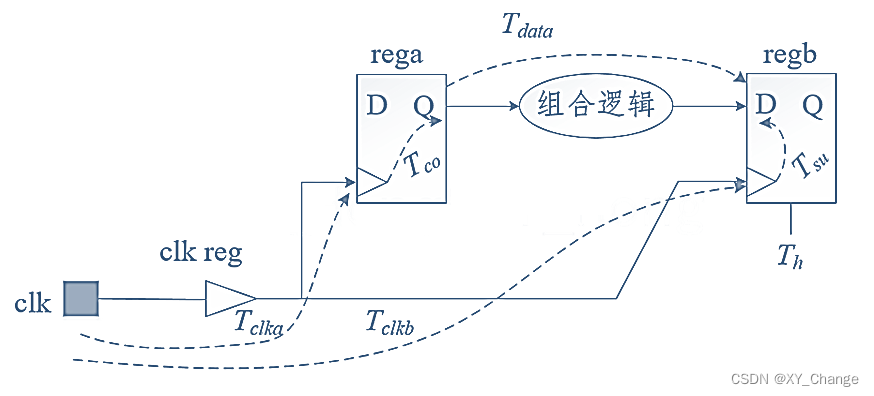

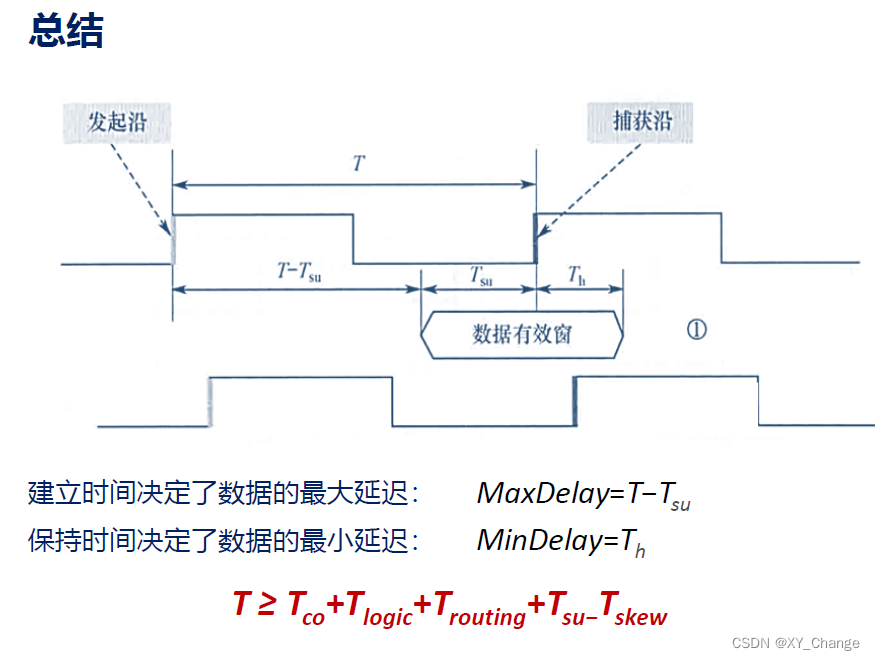

建立时间的数据需求时间,是数据要满足数据建立时间的理论时间,数据被捕获沿稳定捕获到的最小需求时间,顾名思义,肯定要是捕获寄存器时钟沿之前的那段稳定时间,数据需要至少提前Tsu 到达,捕获沿才能稳定捕获到正确的数据。数据延迟过来到捕获寄存器不要紧,但是最大的延时肯定是T-Tsu,因为此时是刚好能满足建立需求时间,若是数据的到达时间大于它,即数据来的延时更大,就不满足建立需求时间了。意味着当刚好能满足数据建立时间需求时,数据的实际延迟时间是一个最大临界值。

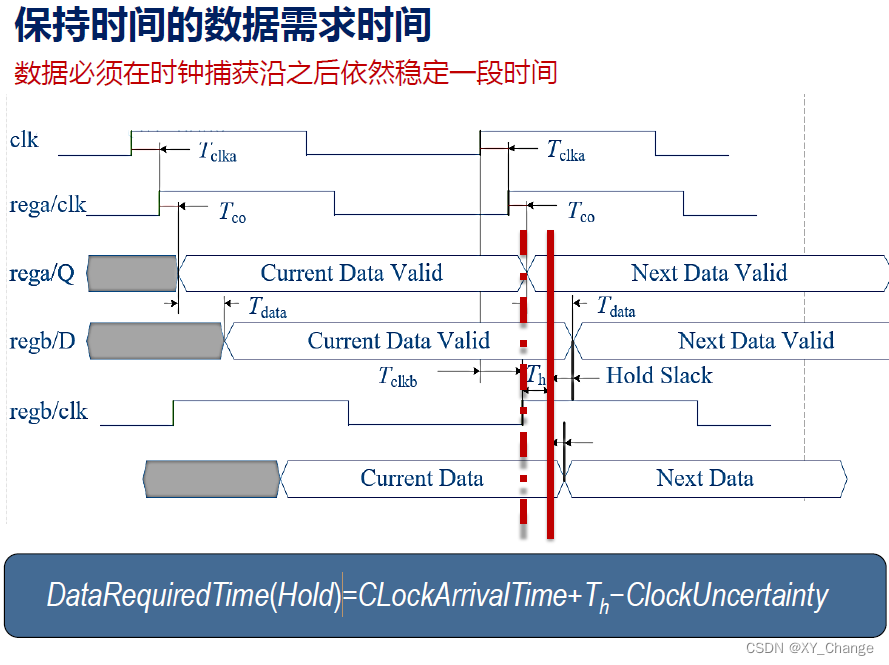

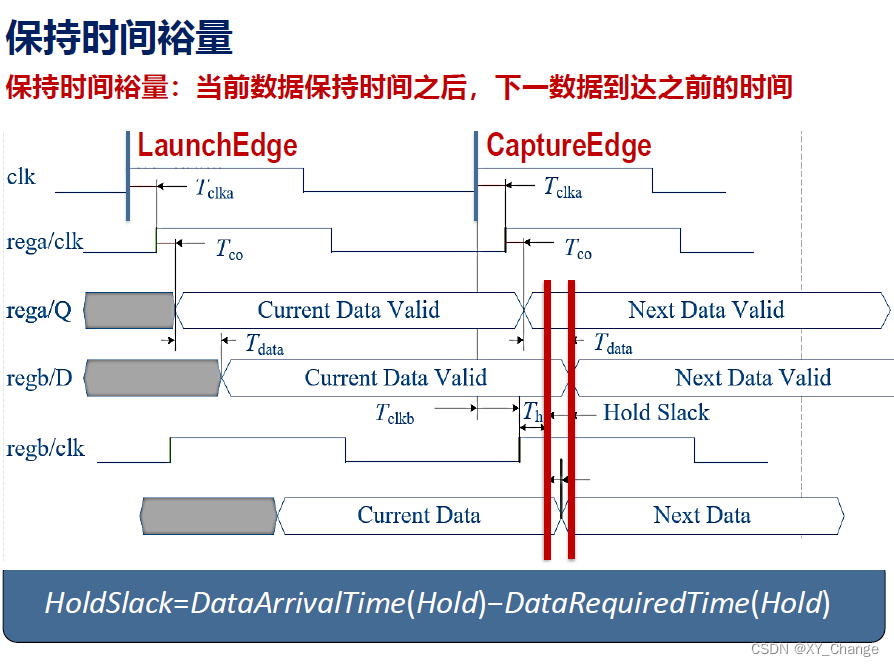

保持时间的数据需求时间,是数据要满足数据保持时间的理论时间,顾名思义,肯定要是捕获寄存器时钟沿之后的那段稳定时间。数据延迟过来到捕获寄存器,如果数据延迟特别小,那么对于建立时间需求肯定能满足,没得说,但是其保持需求时间就不见得能满足了,所以数据实际的最小的延迟时间也要保证刚好能满足保持需求时间。

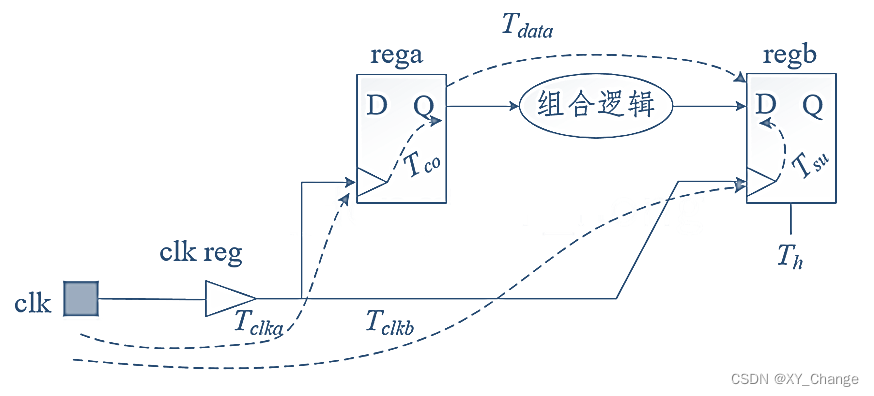

数据实际到达时间DataArrivalTime,是数据走过的路径实际延时时间。指当前的数据经过源端时钟,输出到寄存器的Q 端,再加上逻辑延迟和网络延迟,到达第二级寄存器的D 端,实际在电路中存在的延迟。那么这个数据实际到达时间对于建立需求来说,其是从Launch Edge作起点开始来算。那么这个数据实际到达时间对于保持需求来说,其是从Capture Edge作起点开始算,保持时间余量是为了保证下一个数据不影响当前数据的锁存。目的寄存器在锁存当前数据的时候,源端寄存器也在锁存数据(或者说同时源端寄存器要对目的寄存器发送下一个数据,那么如果目的寄存器的保持时间Th > (Tco+Tdata),那么对目的寄存器来说下一个数据冲了当前的数据

注意,在算保持时间余量的时候,Data_arrival_time和Required_time都是从一个时钟沿算的。意思是,Data_arrival_time算的是捕获沿后下一个数据的到达时间,而Data_required_time是当前数据理论上要保证的在捕获沿后的保持时间。

假设REG1为前级寄存器,REG2为后级寄存器。保持时间比较难理解,它的意思是reg1的输出不能太快到达reg2,这是为了防止采到的新数据太快而冲掉了原来的数据。保持时间约束的是同一个时钟边沿,而不是对下一个时钟边沿的约束。reg2在边沿2时刻刚刚捕获reg1在边沿1时刻发出的数据,若reg1在边沿2时刻发出的数据过快到达reg2,则会冲掉前面的数据。因此保持时间需求约束的是同一个边沿。而建立时间的起点是按reg1的法射沿来作为起点的(傅里叶的猫公众号)。人话就是,我们算保持时间约束时,从REG2的捕获沿那个时刻作为起点,在REG2捕获当前数据同时,REG1发送新的数据过来,在REG2这叫下一个数据,那这个发送过来的下一个数据所用时间是input_delay+Tdataint。

对于保持时间的要求,正是解决下一个数据与当前数据的到来时间矛盾,他们的起点都是一起,即同时的,即意味着在同一个边沿来观察的。建立时间需求是从一个边沿(发射沿)到下一个边沿(采样沿),所以是俩个时钟沿来看的。要十分注意这一点。

时序约束基本概念

时序设计的实质就是满足每一个触发器的建立(setup)时间和保持(hold)时间。

建立时间(Tsu)

触发器的时钟信号沿到来以前,数据需要稳定的时间。

保持时间(Th)

触发器的时钟信号沿到来以后,数据稳定不变的时间。

Launch Edge

源端寄存器发送数据的时钟边沿。

发起沿与捕获沿通常差一个时钟周期(共用时钟情况下)

Latch Edge

目的寄存器捕获数据的时钟边沿,也叫Capture Edge

Tco

时钟到输出的延时时间

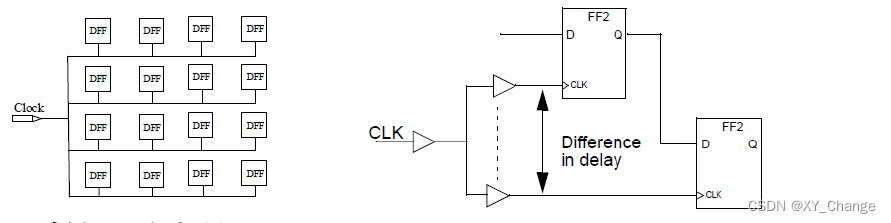

延时偏差Skew

时钟源到不同DFF时钟总输入端的延时差异,这个Skew的存在,会对DFF的时序造成影响。比较坏的情况可能会使得DFF的

setup或hold时序要求无法满足。

时钟不确定性

时钟不确定性是时钟沿的实际到达时间与理想到达时间,可能存在的偏差。主要因素为时钟抖动,

在FPGA器件中,抖动包含有三种,分别是输入抖动、周期抖动、系统抖动。

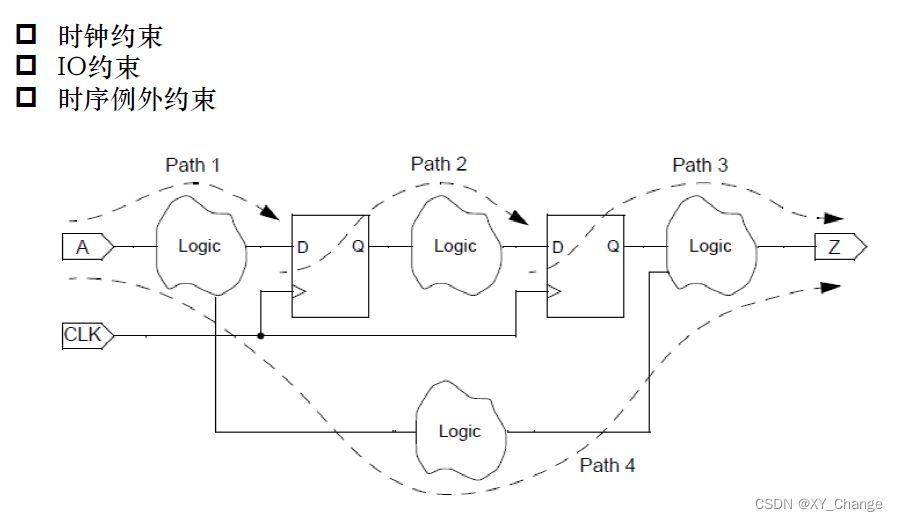

典型时序路径

所谓的输入延迟是外部器件到FPGA输入端口,而FPGA输入端口到器件内部逻辑单元的延迟是调的是IO constraint;

所谓的输出延迟是FPGA输出端口到下级器件的逻辑单元,而FPGA内部末级触发器到FPGA输出端口调的是IO内部延时;

/************************************************************************************************************************************************/

时序分析基本模型

时序分析前要首先树立序模型。那么在FPGA设计中,主要基于下面的俩个模型:

一、Laucch Clock与Capture Clock相同时钟

二、Laucch Clock与Capture Clock不同时钟

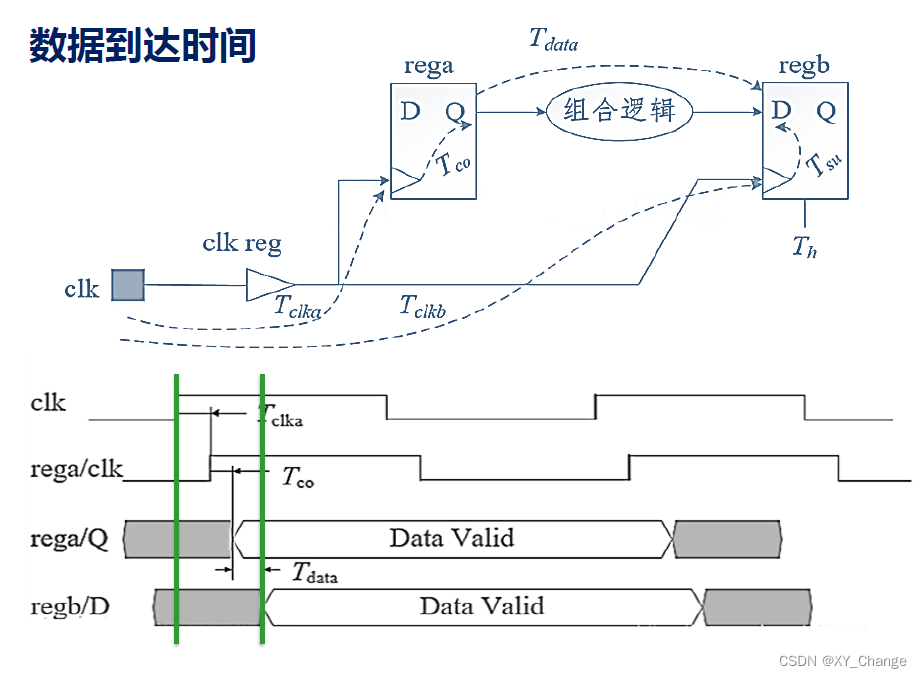

数据到达时间:以发起沿为时间基准点(通常定义是0时刻)

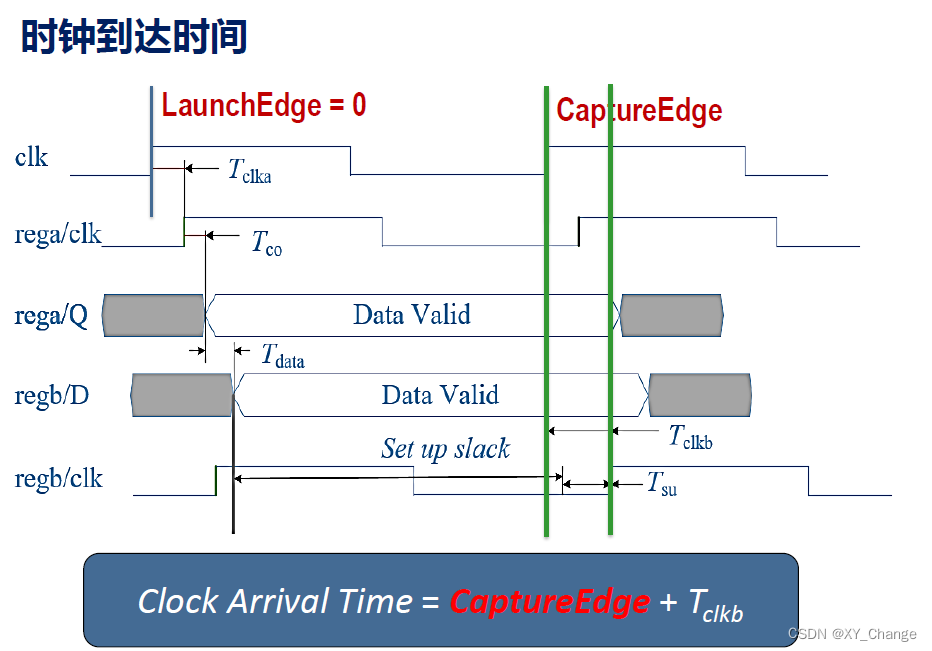

时钟到达时间:以发起沿为时间基准点(通常定义是0时刻)

DataArrivalTime= LaunchEdge+Tclka +Tco +Tdata

TimeArrivalTime= CaptureEdge+Tclkb(TimeArrivalTime = ClockArrivalTime)

1828

1828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?