AXI3.0 & AXI4.0 五大通道接口详细介绍

概述

AXI3 是第三代AMBA协议的一部分,AXI4 是第四代AMBA协议的一部分。

AXI架构分为5个独立的传输通道,读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。数据总线可为(8/16/32/64/128/256/512/1024bit),最大为单次传输一个字节的数据。

五个通道的接口描述

全局信号

| 信号名 | 源 | 描述 |

|---|---|---|

| ACLK | 时钟源 | 全局时钟信号 |

| ARESETn | 复位源 | 全局复位信号,低有效 |

写地址通道信号

| 信号名 | 源 | 位宽 | 描述 |

|---|---|---|---|

| AWID | 主机 | 用户根据slv port 传输任务个数自己定义 | 写地址ID,用来标志一组写信号 |

| AWADDR | 主机 | 如果是访问从机寄存器,则根据寄存器地址大小而定义 | 写地址,给出一次写突发传输的写地址 |

| AWLEN | 主机 | AXI3支持16次突发传输,位宽[3:0]。AXI4 INCR模式支持256次突发传输,位宽[7:0],其余模式位宽[3:0] | 突发长度,给出突发传输的次数 |

| AWSIZE | 主机 | [2:0] | 突发大小,给出每次突发传输的字节数 |

| AWBURST | 主机 | [1:0] | 突发类型 |

| AWLOCK | 主机 | AXI3中[1:0]。AXI4中1位 | 总线锁信号,可提供操作的原子性 |

| AWCACHE | 主机 | [3:0] | 内存类型,表明一次传输是怎样通过系统的 |

| AWPROT | 主机 | [2:0] | 保护类型,表明一次传输的特权级及安全等级 |

| AWQOS | 主机 | [3:0] | 质量服务QoS |

| AWREGION | 主机 | [3:0] | 区域标志,能实现单一物理接口对应的多个逻辑接口 |

| AWUSER | 主机 | 具体位宽由用户自行定义 | 用户自定义信号 |

| AWVALID | 主机 | 1位 | 有效信号,表明此通道的地址控制信号有效 |

| AWREADY | 从机 | 1位 | 表明“从”可以接收地址和对应的控制信号 |

写数据通道信号

| 信号名 | 源 | 位宽 | 描述 |

|---|---|---|---|

| WDATA | 主机 | 具体大小和位宽根据AWSIZE大小定义 | 写数据 |

| WSTRB | 主机 | 写数据有效信号,具体大小为数据大小/8 | 写数据有效的字节线,用来表明哪8bits数据是有效的 |

| WLAST | 主机 | 1bit | 表明此次传输是最后一个突发传输 |

| AUSER | 主机 | 用户自定义大小和位宽 | 用户自定义信号 |

| WVALID | 主机 | 1位 | 写有效,表明此次写有效 |

| WREADY | 从机 | 1位 | 表明从机可以接收写数据 |

写响应通道信号

| 信号名 | 源 | 位宽 | 描述 |

|---|---|---|---|

| BID | 从机 | 用户根据slv port 传输任务个数自己定义 | 写响应ID tag |

| BRESP | 从机 | [1:0] | 写响应,表明写事务的状态:OKAY,EXOKAY,SLVERR,DECERR |

| BUSER | 从机 | 用户自定义大小和位宽 | 用户自定义信号 |

| BVALID | 从机 | 1位 | 写响应有效 |

| BREADY | 主机 | 1位 | 表明主机能够接收写响应 |

读地址信号

| 信号名 | 源 | 位宽 | 描述 |

|---|---|---|---|

| ARID | 主机 | 用户根据slv port 传输任务个数自己定义 | 读地址ID,用来标志一组读信号 |

| ARADDR | 主机 | 如果是访问从机寄存器,则根据寄存器地址大小而定义 | 读地址,给出一次读突发传输的写地址 |

| ARLEN | 主机 | AXI3支持16次突发传输,位宽[3:0]。AXI4 INCR模式支持256次突发传输,位宽[7:0],其余模式位宽[3:0] | 突发长度,给出突发传输的次数 |

| ARSIZE | 主机 | [2:0] | 突发大小,给出每次突发传输的字节数 |

| ARBURST | 主机 | [1:0] | 突发类型 |

| ARLOCK | 主机 | AXI3中[1:0]。AXI4中1位 | 总线锁信号,可提供操作的原子性 |

| ARCACHE | 主机 | [3:0] | 内存类型,表明一次传输是怎样通过系统的 |

| ARPROT | 主机 | [2:0] | 保护类型,表明一次传输的特权级及安全等级 |

| ARQOS | 主机 | [3:0] | 质量服务QoS |

| ARREGION | 主机 | [3:0] | 区域标志,能实现单一物理接口对应的多个逻辑接口 |

| ARUSER | 主机 | 具体位宽由用户自行定义 | 用户自定义信号 |

| ARVALID | 主机 | 1位 | 有效信号,表明此通道的地址控制信号有效 |

| ARREADY | 从机 | 1位 | 表明“从”可以接收地址和对应的控制信号 |

读数据通道信号

| 信号名 | 源 | 位宽 | 描述 |

|---|---|---|---|

| RID | 从机 | 用户根据slv port 传输任务个数自己定义 | 读ID tag |

| RDATA | 从机 | 具体大小和位宽根据ARSIZE大小定义 | 读数据 |

| RRESP | 从机 | [1:0] | 读响应,表明读传输的状态:OKAY,EXOKAY,SLVERR,DECERR |

| RLAST | 从机 | 1 bit | 表明读突发的最后一次传输 |

| RUSER | 从机 | 用户自定义大小和位宽 | 用户自定义信号 |

| RVALID | 从机 | 1位 | 表明都通道有效 |

| RREADY | 主机 | 1位 | 表明主机能够接收读数据和读响应信息 |

接口信号的具体位宽和功能描述

ID 信号

ID类信号(AWID、BID、ARID、RID)

ID信号指示的是传输任务序号,主机可以设置传输任务的序号指示执行的顺序。其中,来自同一个主机,同一个序号的指令只能顺序执行;来自同一主机不同序号的或来自不同主机的传输任务没有执行顺序的要求。因此传输任务ID的作用是指定某些特殊传输任务的顺序,当存在明确的先后顺序时,可以用相同的任务ID标识。

同时在这里还要特别指出,上篇文章当中有一些小错误,写通道的ID在AXI4协议中被取消了,这也就意味着写通道的写顺序必须与写地址通道保持一致。spec中讲取消这一信号的原因是AXI4取消了AXI3协议中对交织写数据的支持,AXI4只能进行连续写数据,因此WID信号变得冗余,为了节省端口数将WID取消掉了。

四个ID信号的位宽可以使用一致的宽度,建议作为模块参数进行自定义,笔者定义位宽为4。

地址类信号(AWADDR、ARADDR)

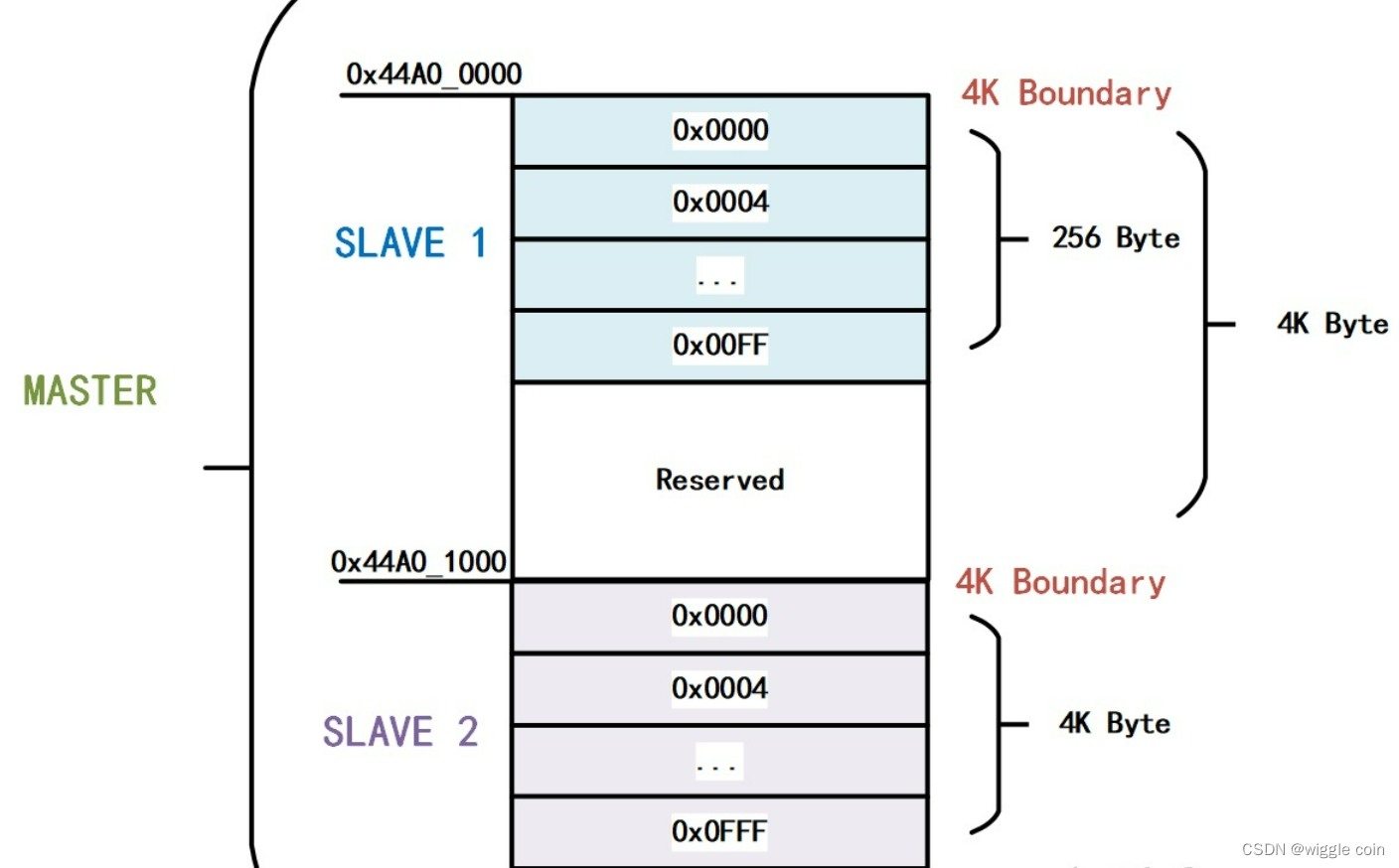

地址类信号的位宽代表了本个从机的地址映射区的大小。这里再废话几句,主机对从机的控制其实是通过访问从机的寄存器实现的。如下图所示,两个从机的寄存器(寄存器大小均为32位)被映射在一个主机的访问地址中,其中0x44A0_0000是第一个从机的偏置地址, 占用空间256 Bytes,(此处及下图中的错误已改正,在这里特别感谢读者Diewelle指出错误)0x44A0_1000是第二个从机的偏置地址,占用空间4KB。如果想要访问第一个从机的第二个寄存器,只需要访问0x44A0_0004地址的寄存器即可。

AXI4协议规定主机上寄存器块的最小分块单元为4K Byte,每个从机的开始映射地址都是4KB的边界。这也影响了AXI4的一个读写规则,那就是一个burst传输不能跨越4KB的界限,否则就会引入将数据错误写入其他从机的风险。注意这个4KB的界限指的是MASTER的地址界限,例如一个burst中不能越过0xXXXX_X000的地址位。

地址位的位宽也可以自定义设置,建议定义为模块参数,笔者设置为了8位,也就是说设计的从机共有64个寄存器,每个寄存器含有一个32位数据。

数据类信号(WDATA、RDATA、WSTRB、WLAST、RLAST)

其中WDATA与RDATA为总线的数据位宽,也是每个地址下的寄存器大小。位宽可以根据总线需要设定,本设计中使用较为常用的32位。

WSTRB为写选通信号,指示当前传输的有效数据段。有效数据段单位是8bit,也就是32bit数据位宽的总线的WSTRB信号会有4位,WSTRB[3]指示WDATA[31:24]的有效性。

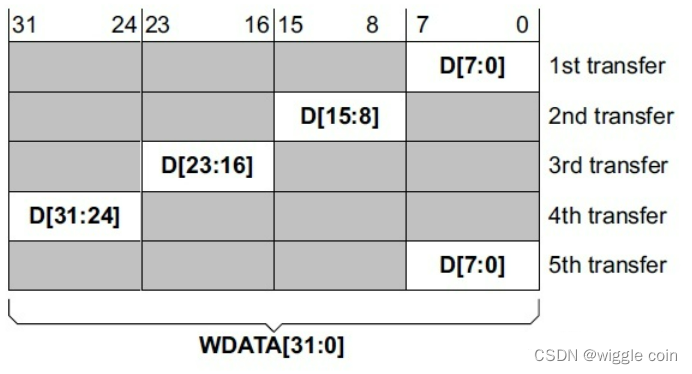

① WSTRB可以用在AXI4总线的“Narrow Transfer”特性中:当burst传输的数据位(burst size)小于总线位宽时,可以通过选通信号进行部分写入。如图所示,当burst size表示传输数据位为8且传输类型为递增(INCR)时,32位数据总线位宽的写入情况(此时的写入选通信号依次为:4’b0001,4’b0010,4’b0100,4’b1000,4’b0001):

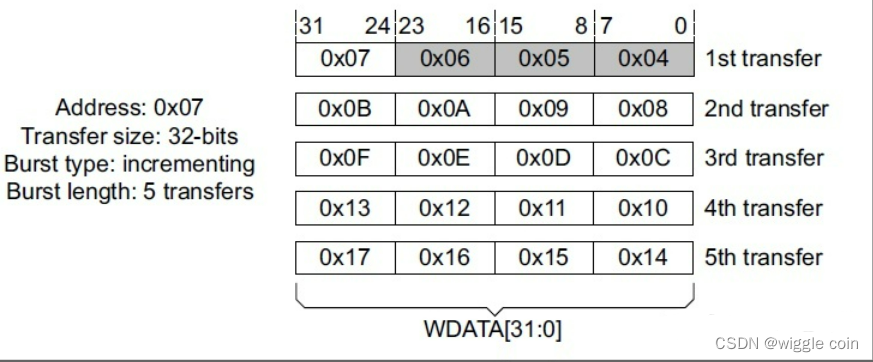

② WSTRB信号也可以用在AXI4总线的“Unaligned Transfer”中:当传输的目标地址与寄存器的边界未对齐时,可以使用非对齐传输,如下图所示,在寄存器位宽32位时,起始传输地址0x07时的传输情况:

WLAST信号指示最后一个写数据,与最后一个写数据的WVALID信号同步拉高。只有当WLAST由高变为低,一个传输任务才完成。在此之前无法中断传输过程。RLAST信号也类似。

传输配置信号(AWLEN、ARLEN、AWSIZE、ARSIZE、AWBURST、ARBURST、AWLOCK、ARLOCK、AWCACHE、ARCACHE、AWPROT、ARPROT、AWQOS、ARQOS、AWREGION、ARREGION)

AWLEN/ARLEN:

传输任务中的传输数据包个数,在INCR传输类型下可以传输1至256个数据包,在其他传输类型下只能传输1-16个数据包,特别地,WRAP传输类型下只能传输2,4,8或16个固定的数据包个数。因此AWLEN与ARLEN的位宽为8位,其中LEN=0代表传输一个数据包。

AWSIZE/ARSIZE:

传输数据包大小,位宽为3位,具体值的意义如下表所示(Bytes=2^Burst_size):

| Axsize | 传输字节数 |

|---|---|

| 3‘b000 | 1 |

| 3’b001 | 2 |

| 3’b010 | 4 |

| 3’b011 | 8 |

| 3’b100 | 16 |

| 3’b101 | 32 |

| 3’b110 | 64 |

| 3’b111 | 128 |

AWBURST/ARBURST:

传输类型,位宽为2位,具体含义如下:

| AxBURST | 传输字节数 |

|---|---|

| 2’b00 | 固定 (FIXED) |

| 2’b01 | 递增(INCR) |

| 2’b10 | 回环(WRAP) |

| 2’b11 | 未定义 |

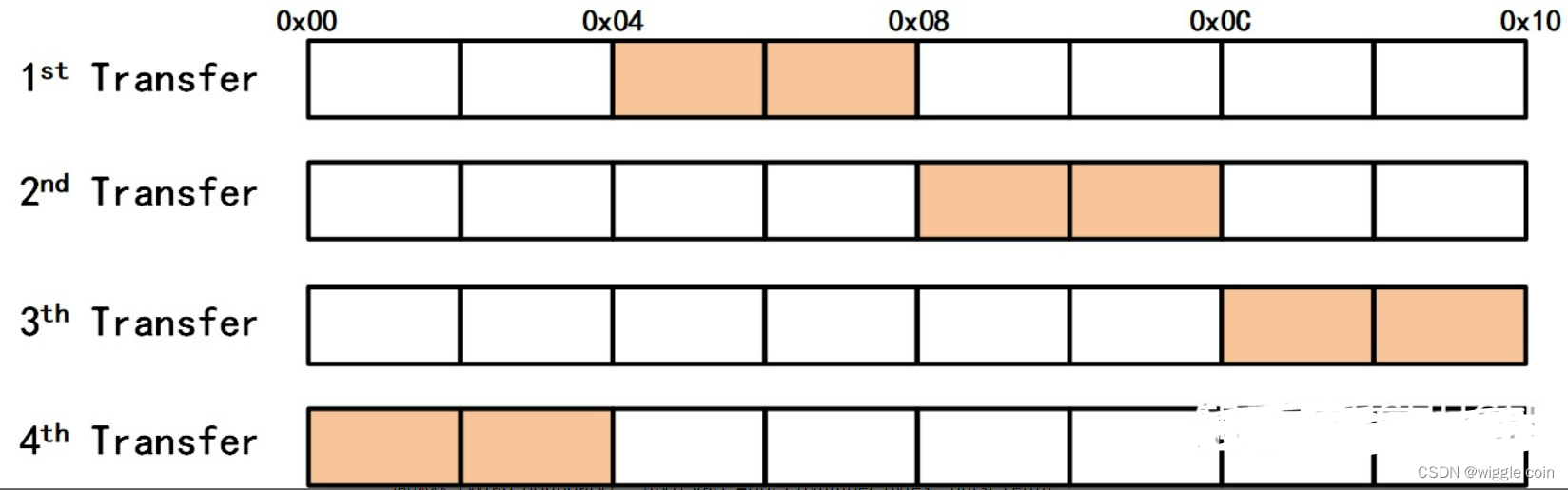

固定传输类型是对一个地址重复写入数据,递增传输类型是地址自动增长,不断写入数据流。需要特别说明的是回环传输类型,其实故名思义,就是地址递增到一定边界后从初始位置继续递增,如下图所示,传输长度为8,传输数据包大小为4 byte,起始传输地址为0x04:

也许这样简单地说不能解决大家的一些疑问,因此将手册中的计算公式也一并给出:

起始地址(Start_Addr): AxADDR

数据包字节数(Number_Bytes):2^(AxSIZE)

传输长度(Burst_Len):AxLEN + 1

对齐地址(Aligned_Addr):(INT(Start_Addr / Number_Bytes))*Number_Bytes

回环界(Wrap_Boundary):(INT(Start_Addr / (Number_Bytes * Burst_Len))) * (Number_Bytes * Burst_Len)

当地址递增至Wrap_Boundary + (Number_Bytes * Burst_Len)时:

当前传输地址:Address = Wrap_boundary

下一个传输地址:Address = Start_Addr + ((N-1)*Number_Bytes) - (Number_Bytes * Burst_Len)

其中N表示数据包在整个Burst传输长度中的序号

AWLOCK/ARLOCK:

这个信号在AXI3协议中用于锁定从机,占用总线,但在AXI4中取消了相关支持,仅 留下一位信号用作指示传输为正常传输(1’b0)还是独有传输(1’b1)。

AWCACHE/ARCACHE:

该信号指明了总线中的存储类型,信号位宽为4位。

| ARCACHE | AWCACHE | Memory TYPE |

|---|---|---|

| 0000 | 0000 | Device Non-bufferable |

| 0001 | 0001 | Device Bufferable |

| 0010 | 0010 | Normal Non-cacheable Non-bufferable |

| 0011 | 0011 | Normal Non-cacheable Bufferable |

| 1010 | 0110 | Write-through No-allocate |

| 1110(0110) | 0110 | Write-through Read-allocate |

| 1010 | 1110(1010) | Write-through Write-allocate |

| 1110 | 1110 | Write-through Read and Write-allocate |

| 1011 | 0111 | Write-back No-allocate |

| 1111(0111) | 0111 | Write-back Read-allocate |

| 1011 | 1111(1011) | Write-back Write-allocate |

| 1111 | 1111 | Write-back Read and Write-allocate |

AWPROT/ARPROT:

指明访问是否被允许的信号,位宽为3位,具体可见下表:

| AxPROT | 值 | 功能 |

|---|---|---|

| AxPROT[0] | 0 | 非优先访问 |

| AxPROT[0] | 1 | 优先访问 |

| AxPROT[1] | 0 | 安全访问 |

| AxPROT[1] | 1 | 非安全访问 |

| AxPROT[2] | 0 | 数据访问 |

| AxPROT[2] | 1 | 指令访问 |

AWQoS/ARQoS:

Quality of Service, 位宽为4位,手册中并没有固定该信号的确切用途,但是建议将该信号用于优先级声明信号,值越高代表优先级越高。

AWREGION/ARREGION:

区域标记,位宽为4位。4位的区域标记信号可以标记16个区域。当从机有很多分离的地址空间时,使用这个信号可以仅仅使用一个物理总线就能实现多个逻辑总线的功能。经典的应用是一个外设控制寄存器与数据寄存器分离的时候,使用该信号可以在不对地址解码的情况下访问到两块地址空间。

例如,当一个外设控制寄存器的地址空间为0x0000 - 0x00FF,数据寄存器的地址空间为0x1000 - 0x1FFF,就可以将地址位设置为12位(0x000-0xFFF),控制寄存器的区域标记为4’b0000,数据寄存器的区域标记为4’b0001,实际寻址的地址为区域标记+地址位,其中区域标记位作为高位加在地址位前就可以了。

需要注意的是,每4KB的地址空间上仅能有一种REGION标记,也就是区域分割的最小单元为4KB。

1185

1185

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?