1,AXI 总线

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM 公司提出的 AMBA(Advanced Microcontroller Bus Architecture)3.0 协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是 AMBA 中一个新的高性能协议。AXI 技术丰富了现有的 AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

AXI 特点: 单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低

2,通道说明

AXI总线共5个通道分别为:写地址,写数据,写响应;读地址,读数据.

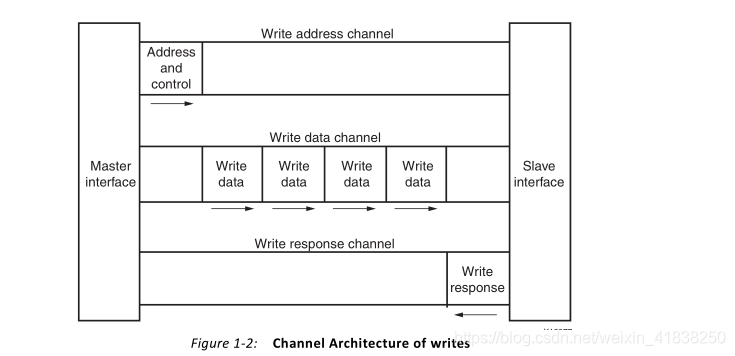

写数据过程如下(图来源于ug761):

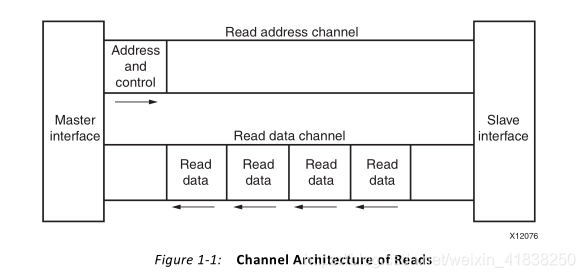

读数据过程如下(图来源于ug761):

3,信号定义

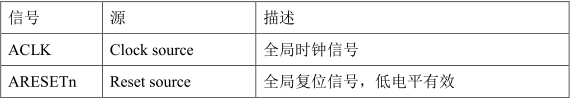

(1)全局信号:

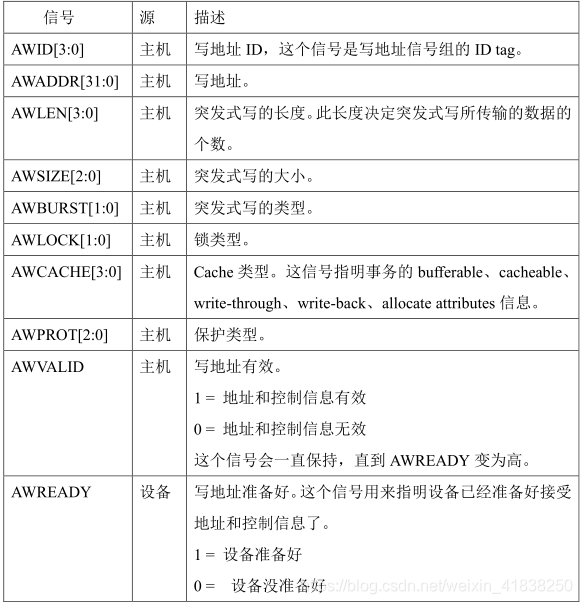

(2)写地址通道信号:

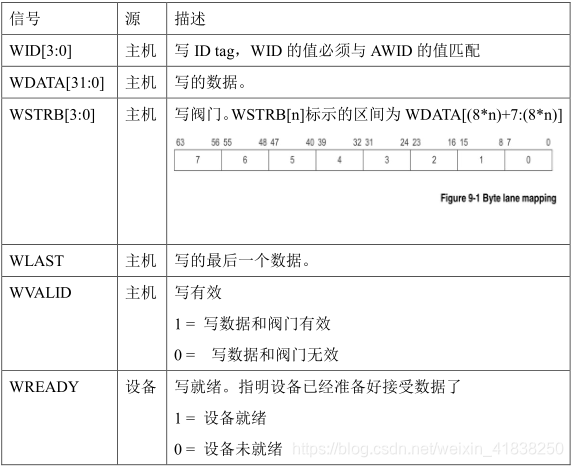

(3)写数据通道信号:

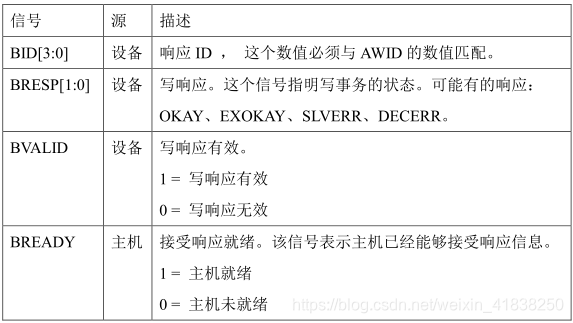

(4)写响应通道信号:

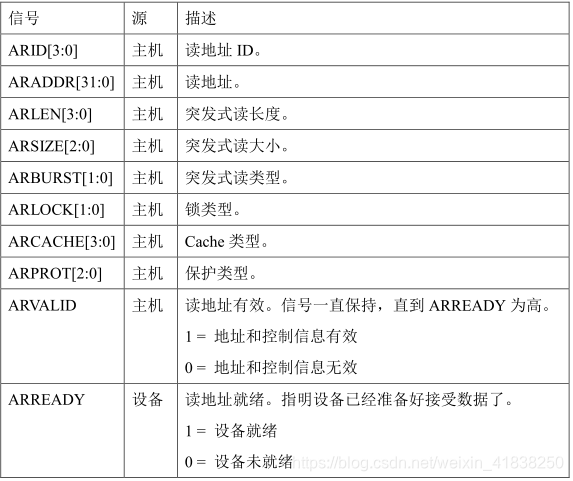

(5) 读地址通道信号:

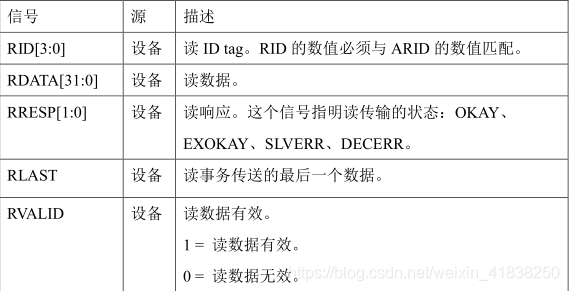

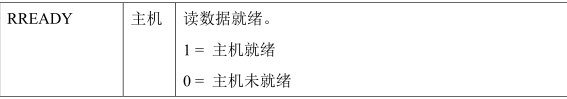

(6)读数据通道信号:

4,信号说明

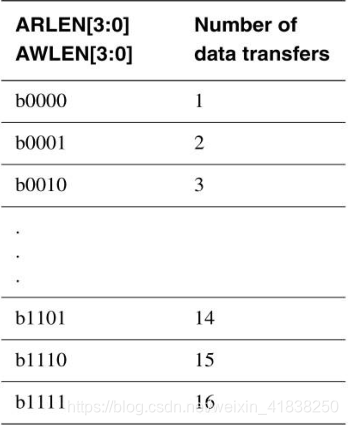

(1)awlen和arlen对应突发长度(字节)。

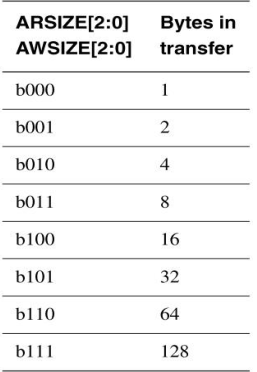

(2)arsize和awsize对应数据位宽(8bit)

6,AXI总线为了简化使用,有两个精简版的协议,就是AXI-Lite和AXI-stream.

AXI-Lite : 一次读写一个地址数据。没有突发等相关信号参数。

AXI-Stream : AXI数据流,没有地址,直接通过ready,valid握手成功就为一拍数据。这也是现在设计用的最多的协议总线.

AXI(Advanced eXtensible Interface)是ARM公司提出的高性能片内总线协议,包含写地址、写数据、写响应、读地址和读数据五个通道。其特点是单向通道、独立的地址和数据通道,支持突发传输和乱序访问,简化时钟域间桥接,提高数据吞吐能力和系统性能。AXI还有AXI-Lite和AXI-Stream两个精简版协议,分别适用于简单读写和数据流操作。

AXI(Advanced eXtensible Interface)是ARM公司提出的高性能片内总线协议,包含写地址、写数据、写响应、读地址和读数据五个通道。其特点是单向通道、独立的地址和数据通道,支持突发传输和乱序访问,简化时钟域间桥接,提高数据吞吐能力和系统性能。AXI还有AXI-Lite和AXI-Stream两个精简版协议,分别适用于简单读写和数据流操作。

3420

3420

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?