使用ACE_LITE接口的IP属于snooping的Master,它们的主要缺陷如下:

-

单向一致性: ACE_LITE接口支持I/O一致性,这意味着设备可以snoop处理器内部的cache,但处理器不能snoop设备内部的cache。这种单向一致性限制了系统的整体一致性,可能导致数据不一致的问题。

-

不支持full coherency: 与ACE接口相比,ACE_LITE接口不支持full coherency,即设备和处理器之间不能互相snoop对方的cache。这限制了系统的灵活性和扩展性,特别是在需要全缓存一致性的场景下。

-

增加的coherency traffic: 由于ACE_LITE Master主要用来snoop其他的ACE-compliant master,它们自己不能被snooped,这可能导致coherency traffic增加,影响系统性能。

-

系统复杂性: ACE_LITE接口的设计可能导致系统设计更加复杂,因为需要处理单向snooping和不一致性问题,这可能需要额外的硬件和软件支持来维护数据一致性。

-

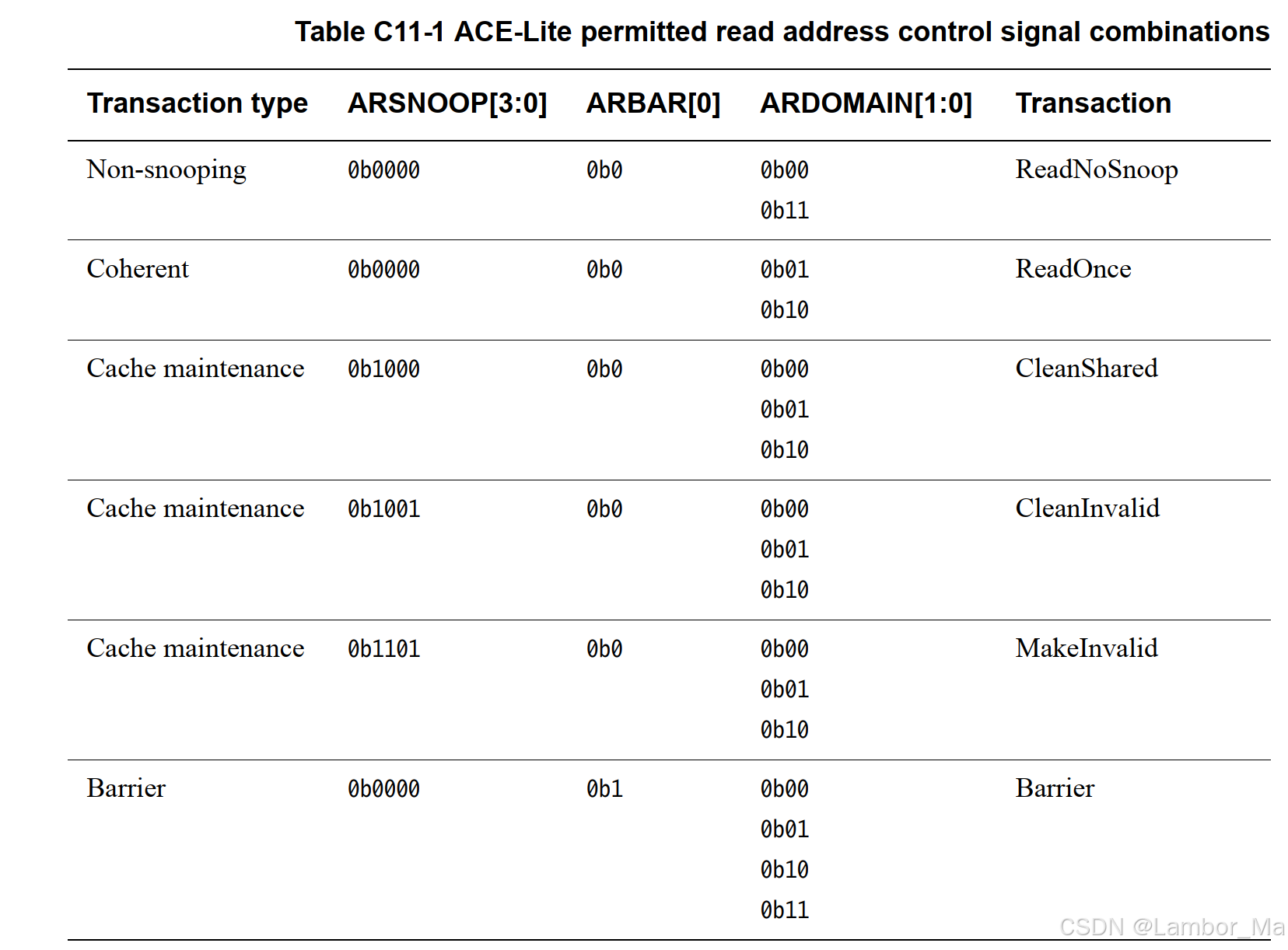

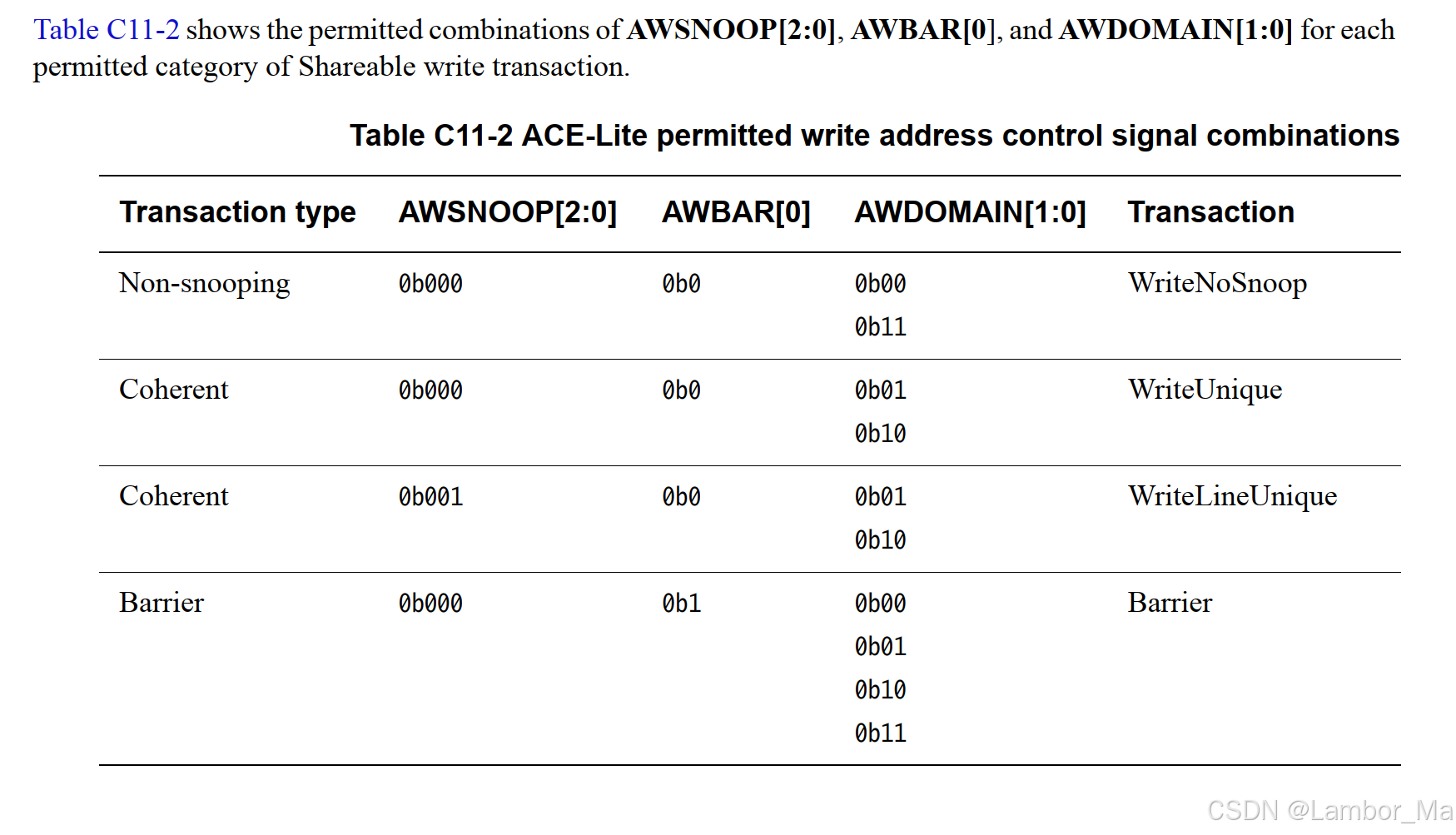

限制的事务类型: ACE_LITE Master只能实现Non-shared、Non-cached和Cache Maintenance事务,限制了其在更复杂场景下的应用。

-

可能的性能损失: 由于ACE_LITE Master不能被snooped,可能无法充分利用缓存一致性协议的性能优势,导致在高负载时性能损失。

-

兼容性问题: ACE_LITE接口可能与其他支持full coherency的系统组件存在兼容性问题,这可能限制了系统的扩展性和升级能力。

2549

2549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?