静态时序分析,通过遍历所有的传输路径,寻找所有组合逻辑电路最坏延迟情况,检查建 立时间和保持时间是否满足要求,检查恢复时间、移除时间;时钟脉冲宽度、时钟抖动偏移, 验证设计在时序上的正确性,并确定能否在要求的工作频率下运行。

STA 优缺点

优点:执行速度快;不需要测试向量;覆盖率可达 100%

缺点:只能验证时序特性,如果设计中有较多的异步电路,要通过门级动态仿真来验证。 不能识别多周期路径、伪路径等。

建立、保持时间

建立时间 Tsetup:时钟有效边沿之前输入数据有效且稳定不变的时间。

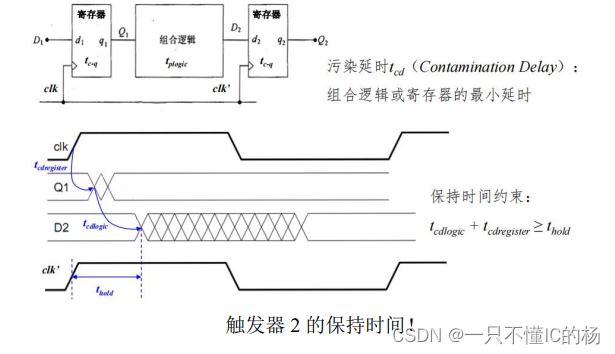

保持时间 Thold:时钟有效边沿之后输入数据有效且稳定不变的时间。

传播延时 Tcq: 时钟有效边沿到寄存器 Q 输出更新的时间。

组合逻辑延时 Tplogic:组合逻辑最大延时。

时钟周期约束

保持时间约束

正时钟偏斜 skew 对于建立时间 Tsetup 的满足是有益的,而对保持时间 Thold 的满足是有害的。

时钟约束修复

PVT:制造工艺 Process、工作电压 Voltage、温度 Temperature

PVT 对芯片运行速度影响很大。在静态时序分析时,会在 PVT 条件下分析芯片时序是否满足要求。 分析建立时间用 ss 慢速模型:高温+低压+慢速模型;(最差情况) 分析保持时间用 ff 快速模型:低温+高压+快速模型。电压低组合逻辑延时大。(最好情况)

Tsetup 建立时间不满足,采用措施

◼ 降低时钟频率;(T 增大)

◼ 采用流水线;(组合逻辑延时减小)

◼ 提高工作电压;减少信号延迟。

◼ 使用反应速度更快的 D 触发器

建立时间与工艺、温度、电压,时钟周期有关。 建立保持时间是芯片本身的特性,他们的存在是触发器内部的特性又在屏蔽毛刺方面起到了一定作用。建立 保持时间与组合逻辑延迟有关,对于组合逻辑的延迟,也即触发器之间的门延迟,不能太大,也不能太小,太大会导致(关键路径)建立时间不满足,太小会导致(关键路径)保持时间不满足。

Thold 保持时间修复

保持时间与 工艺、电压、温度有关。

◼ 插入 Buffer 缓冲器延时

◼ 做时钟树平衡

◼ 提高温度,降低电压。(延时加大)

降低时钟频率无法解决,保持时间公式里没有 T,与 T 无关。

恢复、去除时间

Recovery time 恢复时间:异步信号在时钟来临之前有效稳定保持不变的时间。与同步电 路中的建立时间类似。与寄存器的复位有关,在时钟有效沿来临之前,复位就要撤销,数据就 要开始恢复正常的时间。

Removal time 去除时间:异步信号在时钟边沿之后输入数据有效且稳定不变的时间。

时钟偏差、时钟抖动

⚫ 时钟偏差(Clock Skew):由于时钟的路径长短和经过负载的延时不同,造成时钟在空间上的差别。

⚫ 时钟抖动(Clock Jitter):时钟周期变长或缩短,时钟周期 T 变化。

⚫ 区别:Jitter 是在时钟发生器内部产生的,和晶振或者 PLL 内部电路有关,布线对其没有影响。Skew 是由不同布线长度导致的不同路径的时钟上升沿到来的延时不同。

如何时序收敛

时序收敛要保证建立时间和保持时间收敛。

方法:

流水线、retiming 重定时、逻辑复制、采用树型加法器、关键信号后移、消除优先级等解决办法。

(1)流水线。时序不收敛是因为两个触发器之间的组合逻辑延时太大,采用流水线技术, 将组合逻辑分解,降低了组合逻辑延时,

(2)寄存器重定时。在不改变电路功能的情况下,将大块组合逻辑分成小块的组合逻辑, 分布到寄存器之间。通过改变寄存器的位置来优化关键路径,减少组合逻辑最大延时,从而改进最高时钟频率。

(3)逻辑复制。当信号扇出很大时,该信号到各个目的逻辑节点的路径变得很长。通过对寄存器进行复制来降低扇出,复制几个相同的寄存器来分担原来一个寄存器驱动模块的任务。 逻辑复制另一种方法,是在 DC 软件的约束文件中,设置 max_fanout 属性,一般将max_fanout设置为 3,当实际设计中该信号的 fanout 超过了3,综合器会自动优化。

(4)操作符平衡,将串行逻辑并行化处理,积之和变为和之积。例如 Z=A*B*C*D,利用括号进行操作数平衡 Z=(A*B)*(C*D)。变成树状乘法器、树状加法器。 (5)其他方法有关键信号后移,消除优先级等方法。

代码风格上

1、不要使用多层嵌套的条件语句。 多层嵌套代码被综合成具有优先级的电路。使用 case 综合并行结构,关键路径延时明 显减小。

2、用寄存器对模块的输入与输出进行缓存。 对异步电路,用寄存器缓存能减小亚稳态发生的概率,消除组合逻辑竞争冒险带来的 毛刺。对同步电路,用寄存器缓存可以降低 fanout 被逻辑复制。 但缓存占用资源,还带来一个时钟延迟。完成子模块连接的顶层模块就不该缓存输入输出。

项目中电路时序没有很高,主要考虑的是跟面积平衡。如果增加乘法器数量提高并行度,会提高速度。时序违规主要是路径中的组合逻辑过长或者高扇出导致。CPU 关键路径是取指译码模块,主要是代码中逻辑过于复杂和多层的 if-else 导致的。硬件加速器关键路径主要包含大量的加法器逻辑,导致延时过大。针对逻辑复杂的问题可以加入流水线级数分割逻辑;而多层的嵌套条件语句则需要优化代码。

4747

4747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?