助力转向电机中(EPS)一般除了接收CAN节点,还接收来自于转向管柱下端的扭住传感器信号,所以要想电机正常工作,需将这一路信号给模拟出来并和下位机模型能实现数据的实时交互,这主要分为三个大的步骤。

一:信号协议的学习和解析

二:板卡的选择和仿真应用(FPGA仿真应用)

三:软件集成-(Veristand CD应用)

一:信号协议的学习和解析

因为扭矩传感器都在助力转向电机中,没有对外接口,因此仿真时最困难的是去确定协议,但市面上相关传感器所有协议基本就几种,一般而言,厂家也会对协议进行部分修改,以满足设计或者安全的需求,但也不会改变太多,变更太多可能会导致硬件层的变更,因此解析难度也不算高。

采集前,最好先用示波器在各PIN的样件端和ECU端各测一次,确定芯片输出模式。(漏极、源极)

实采波形如下:

根据实采数据,可大概推测出可能协议,

协议的内容,本案例不做展开,有了此波形数据,确定我们的仿真目标

(注:最好办法就是查看其芯片,根据芯片手册,即可知道协议内容以及校验方式等信息)

芯片查询网址:

二:板卡的选择和仿真应用(FPGA仿真应用)

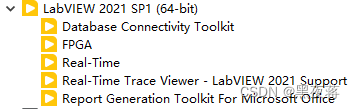

1>环境搭建

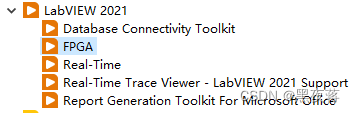

首先环境配置,请注意62bit Labview 2021无法生成FPGA模板。

硬件为:NI实时机和PXI-7856

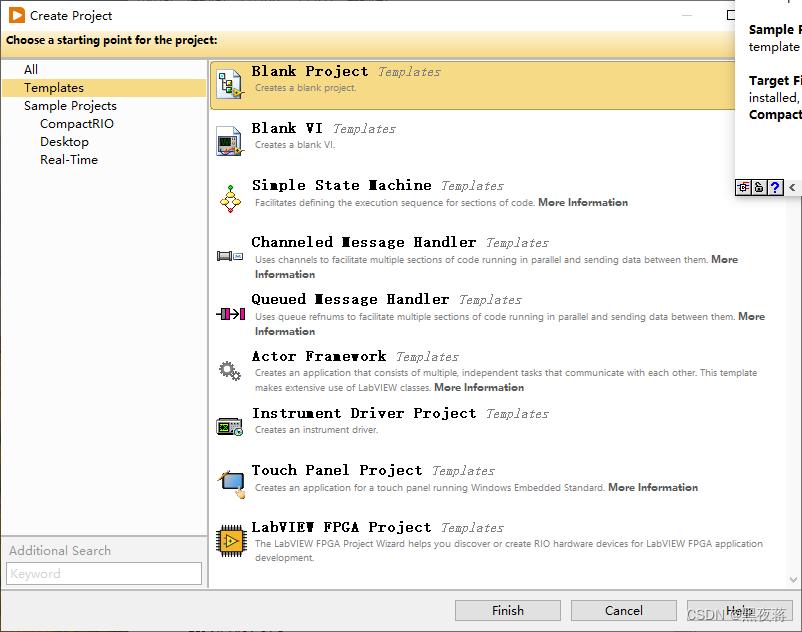

环境配置完成后,就开始创建一个

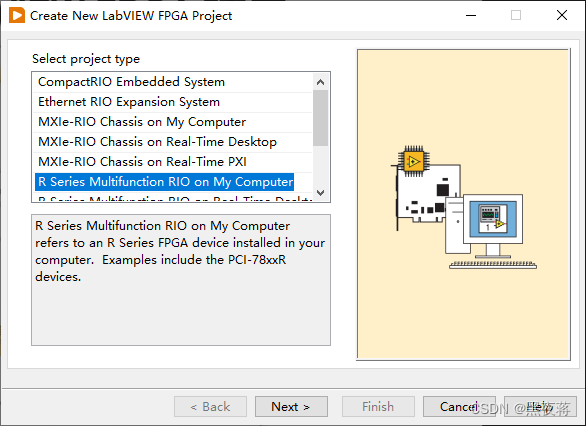

选择完成后,选择项目类型

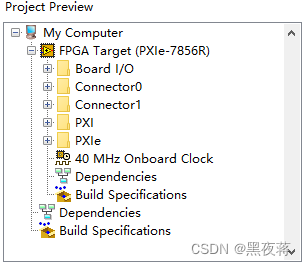

然后进入系统设置,可以选择已连接上的硬件,或者创建一个新的硬件。建议是新建一个硬件(PXI-7856),一切选择完成后,会出现下图关于此硬件的一些基本情况,其中40 MHz Onboard Clock即为此硬件的时钟周期(Ticks),换算下来(1/40MHz)等于0.025us,可以理解为,要是你想隔1us发一个电平,此板卡中需要设置40个实时周期(Ticks),Connector0/1为板卡的IO,也是这次的调用对象。

综上,FPGA编程环境搭建完成

2>FPGA编程

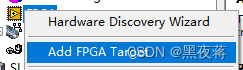

进入项目主界面,在FPGA Target下面新建VI ,如下图

进入后面板,可看到关于板卡的函数

本案例中主要操作的函数有:

此函数主要用于IO的选择,并赋值,比如IO赋真

此函数提供了一些常用的操作方法,比如等待下降沿触发

此函数主要用于时间的控制

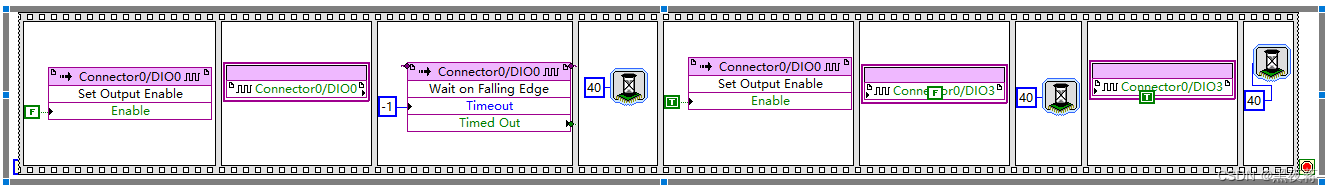

举个小例子:

接收到上位机给出的下降沿指令后,令板卡通道1上面发送一个周期为1us的方波(当然了方波的高低电平在板卡输出和输入范围之内)

但一般,我们需将控制变量放在上位机进行实时控制,并和主程序进行互动,这就需在上位机新建VI,如下图

主要是open->read/write/close,本例中就不做详细展开了

(注意:open时,一般选择编译好FPGA的文件,此步骤一般也是在编译完成之后,调试阶段除外)

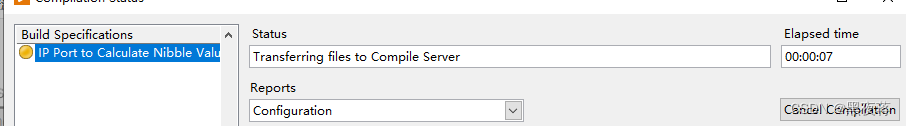

3>FPGA编译

将例子中的VI点击运行,即开始编译(有云端编译和本地编译,云端不占用本地内存,但需注册NI账号且只有90天试用期)

编译完成后,会有提示并生成xxx.lvbitx文件,上位机调用时,即可选用此文件。

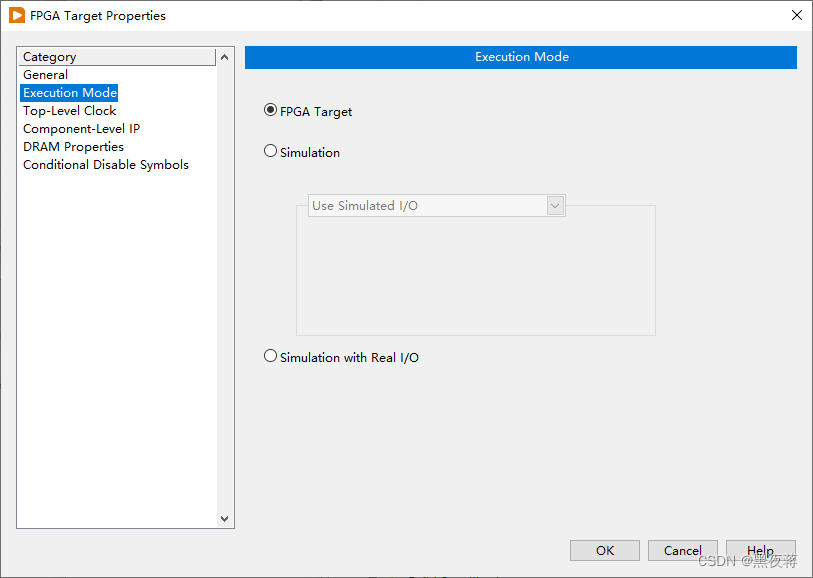

一般调试时,因避免编译浪费时间,可选择仿真,这样就可以直接运行,查看逻辑是否正确。

至此,我们完成了扭矩信号的FPGA的仿真。

三:软件集成-(Veristand CD应用)

此案例中是NI 实时系统,但NI veristand中对FPGA板卡的应用只提供的了几个简单常见的调用接口,对于此类自定义的,我们需要从custom devices中添加并实现数据交互。

(注意本段学习最好有一定的Labview编程基础)

1>环境搭建

此模板中选用 64bit labview,32位无法正常识别驱动。

veristand的版本:2021

需安装CD 开发驱动环境,如下:

- ni-custom-device-development-tools-2021-support_23.0.0.10_windows_x64.nipkg

- ni-veristand-2021-custom-device-labview-support-common_23.0.0.10_windows_x64.nipkg

- ni-labview-memory-management-tools-labview-2021-support_23.0.0.10_windows_x64.nipkg

- ni-custom-device-wizard-labview-2021-support_23.0.0.1_windows_x64.nipkg

2>驱动编程

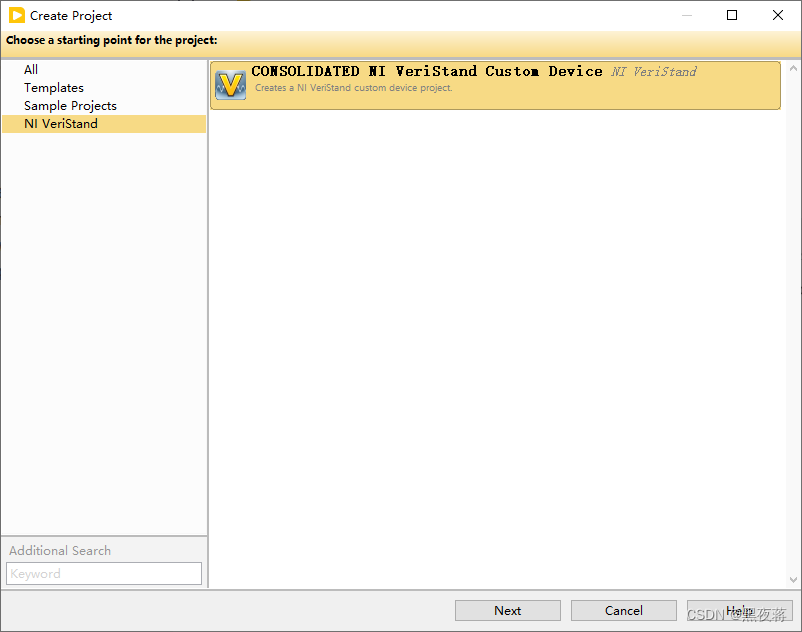

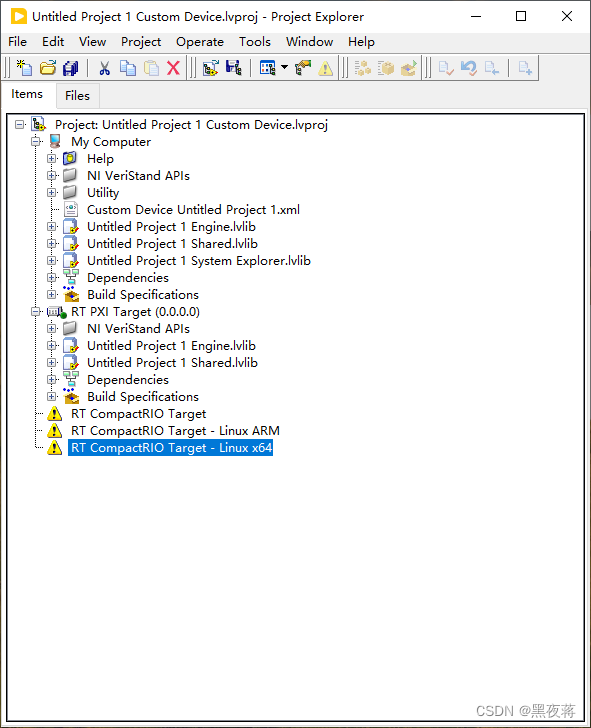

如下图,新建一个模板程序

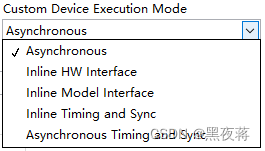

选择异步执行

此模板程序用于板卡和veristand的交互口定义和数据传输,但并没有规定具体的板卡和交互,这一块也正是我们所需要在模板程序中添加的部分。编译完成后,既可以在veristand配合模型中完成板卡的数据交互

这里面有三个VI比较重要,如下图两个VI主要是用于变量的定义和控制,本案例中不详细展开,可自行搜索,相关解释挺多的。

主要讲解 RT Driver VI.vi,

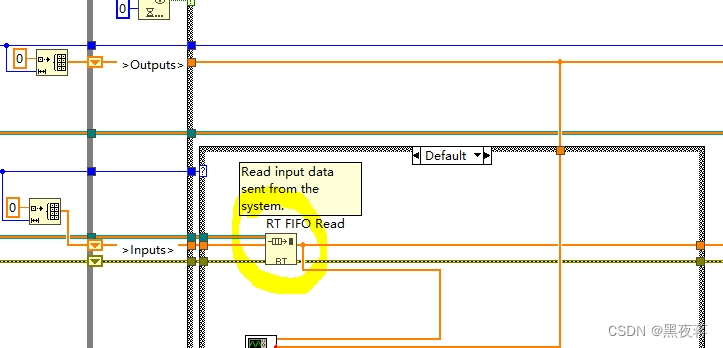

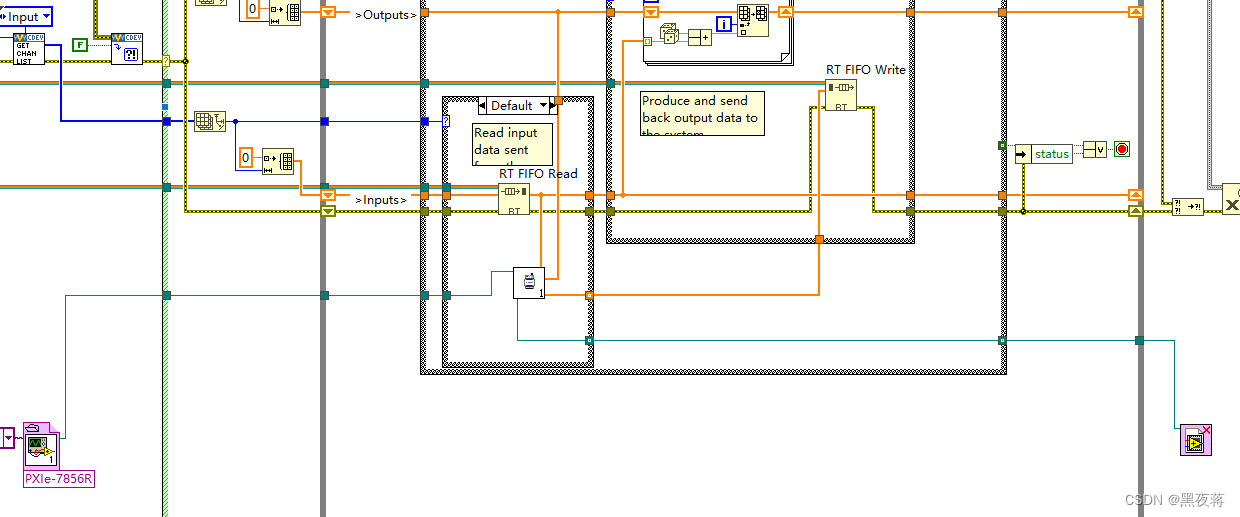

下图中,黄色框部分即为函数从veristand中读取数据,我们需在此将控制板卡写入的VI插入

(可理解为将FPGA上位机控制的部分)

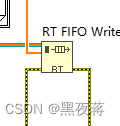

同理,此部分为板卡采集的数据需在此插入,写入到veristand中

举个小例子:

此处重点强调下,Veristand的中的参数如下图,是依顺序依次传入到FIFO中,无需人为匹配

其中的交互程序就是FPGA板卡的上位机控制程序

3>CD编译

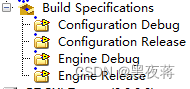

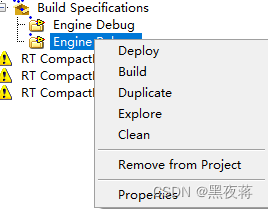

编译需在上下位机各进行一次,如下图,点击右键->build

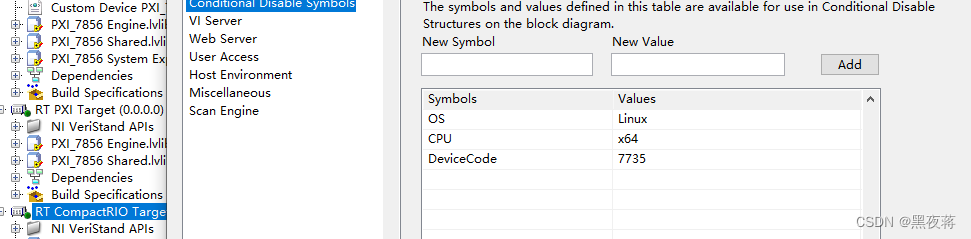

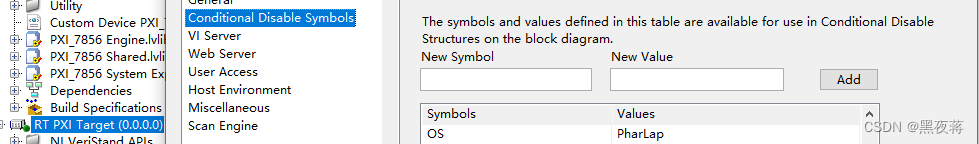

下位机编译时,请确保操作系统为Linux,

下图中的系统则是不对的, 编译完成后,导入veristand会显示路径报错!如何处理此类型报错,本文不做展开。

(PharLap是NI公司早期的实时系统,较Linux相比,有点像windows,现已基本不用)

下位机编译如下

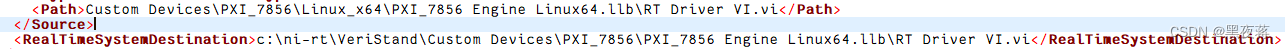

编译后生成文件的地址:

C:\Users\Public\Documents\National Instruments\NI VeriStand 2021\Custom Devices

其中的xxx.xml文件即为Veristand的可识别文件

综上,完成基于Veristand环境下CD驱动的编写,导入Veristand CD模块,即可正常使用

2246

2246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?