1 锁存器的寄存器的区别

锁存器:电平敏感

always@(enable or d)

?? if (enable) ? q <= d;由以上代码可知,在enable有效的时间内,q完全跟踪d的值,比如在这个时间d变化了,q跟着变化,当enable失效的时候,q存储d最后的值。

触发器:边沿敏感。(输出只在时钟某个时刻变化)

always@(posedge enable)

?? if (enable) q <= d;寄存器:在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。

锁存器与寄存器的区别:

- 寄存器是同步时钟控制,而锁存器是电位信号控制。锁存器一般由电平信号控制,属于电平敏感型。寄存器一般由时钟信号控制,属于边沿敏感型。

- 寄存器的输出端平时不随输入端变化而变化,只有在时钟有效时才将输入端的数据传递到输出端(打入寄存器),而锁存器的输出端平时总随输入端变化而变化,只有当锁存器信号到达时,才将输出端的状态锁存起来,使其不再随输入端的变化而变化。

- 虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合电路的特性。这样就容易有冒险,竞争之类的问题产生毛刺。

2 DFT设计增加的电路一般包括

SCAN 边界扫描

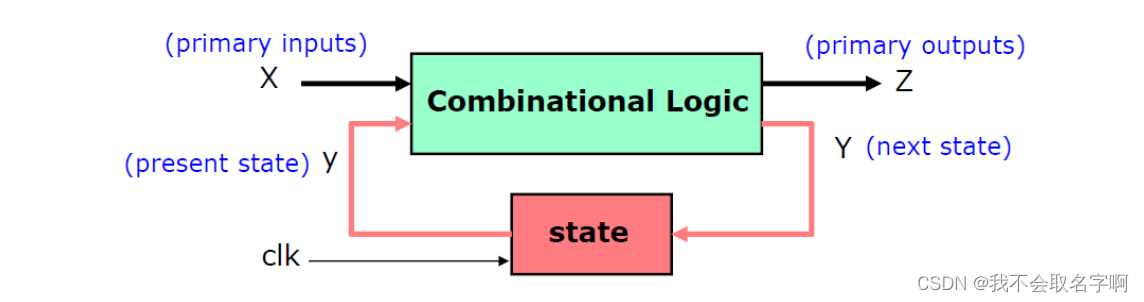

将时序电路用下图的模型表示:

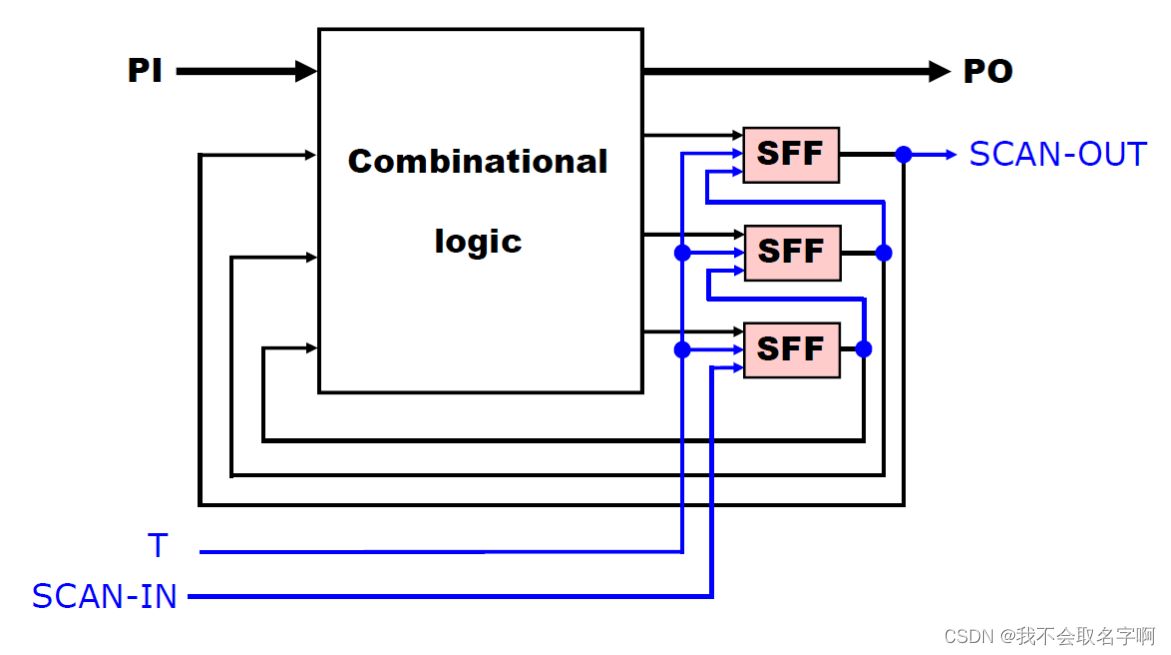

为了使state vector元素controllable和observable,我们添加:

- A TEST mode pin (T)

- A SCAN-IN pin (SI)

- A SCAN-OUT pin (SO)

- A MUX (switch) in front of each FF (M)

添加SCAN的结构如下:

Scan设计规则:

- Use only clocked D-type of flip-flops for all state variables.

- At least one PI pin must be avaliable for test; more pins, if avaliable, can be used.

- All clocks must be controlled from PIs.

- Clocks must not feed data inputs of flip-flops.

Scan测试步骤:

- 转换到shift-register模式,通过shift in由0和1组成的序列来检验SR操作。例。00110(功能测试)。

- 初始化SR——载入第一个pattern。

- 切换回常规模式并应用test pattern。

- 切换到SR模式,在设置下一测试的初始状态时,移出最终状态。回到步骤3。

BIST (Built-in Self-test)自建内测试

BIST——一个电路测试它自身的能力

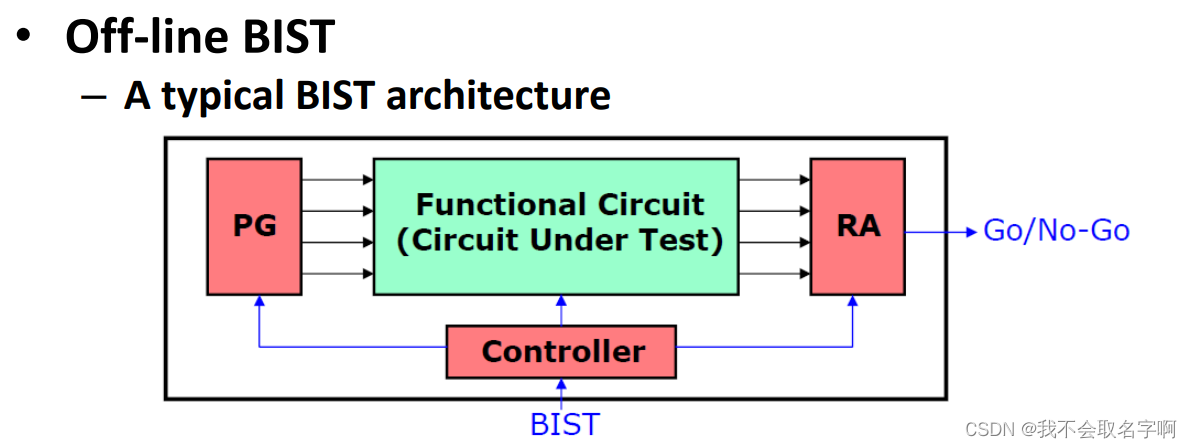

一个典型的Off-line BIST结构如下图所示:

MBIST 存储器自建内测试

3 False Path

False-Path: 指不希望工具分析的路径。一般是异步路径,即跨时钟域的路径。另一种是与电路正常工作不相关的电路,比如测试逻辑的电路。

4 建立时间&保持时间

建立时间:Tclk > Tc2q + Tlogic,max + Tstp

保持时间:Tc2q + Tlogic,min > Thold

5 跨时钟域处理

注意事项:

- 同步器前不能有组合逻辑电路。在前一个时钟域的DFF输出和后一个时钟域输入之间不能有组合逻辑,原因是组合逻辑会造成毛刺现象,后一级时钟域的DFF很可能敲到毛刺,进而引入错误。

- 避免重收敛(reconvergence)和分叉(divergence)。可能导致与预期功能不一致的错误。

解决方案1:多个1bit信号待同步时,必须在原时钟域完成组合汇聚和寄存处理,不能分别同步到另一个时钟域再汇聚。

解决方案2:同源信号复制跨时钟域时,需要先进行跨时钟域,再进行复制。

单bit信号:

- (慢->快)两级触发器同步

- (慢->快)边沿检测同步器

- (快->慢)脉冲同步器=脉冲扩展同步器

步骤:

(1)展宽

(2)打两拍

(3)边沿检测

注意:输入脉冲的间隔至少是两个同步时钟周期(慢时钟)才行,否则signal_slow区分不开signal_fast的两个脉冲。

- (快->慢)握手

多bit信号:

- 握手

- DMUX同步器——数据使能选通设计

- 异步FIFO

注意:只有相邻两个时钟周期最多变化13位的情况才可以进行打拍处理,故一般对地址总线使用异步fifo进行跨时钟域处理,而对数据总线不适用。

6 触发器的分类

按逻辑功能不同分为:RS触发器、D触发器、JK触发器、T触发器。

按触发方式不同分为:电平触发器、边沿触发器和脉冲触发器。

按电路结构不同分为:基本RS触发器和钟控触发器。

按存储数据原理不同分为:静态触发器和动态触发器。

按构成触发器的基本器件不同分为:双极型触发器和MOS型触发器。

1578

1578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?