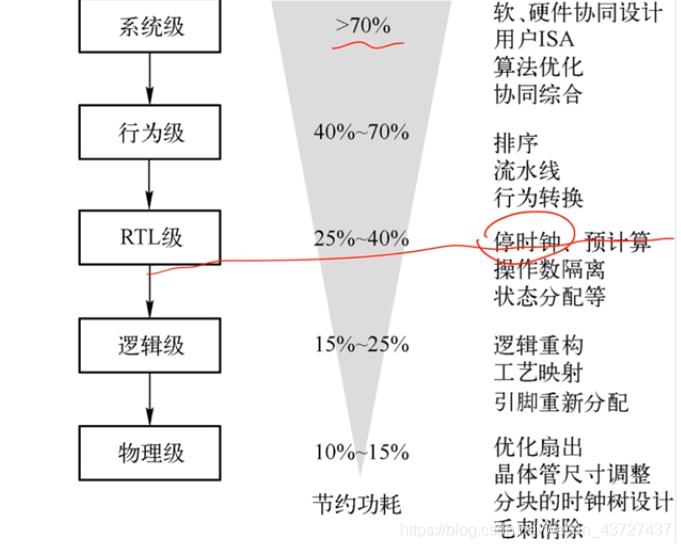

on- chip Variations

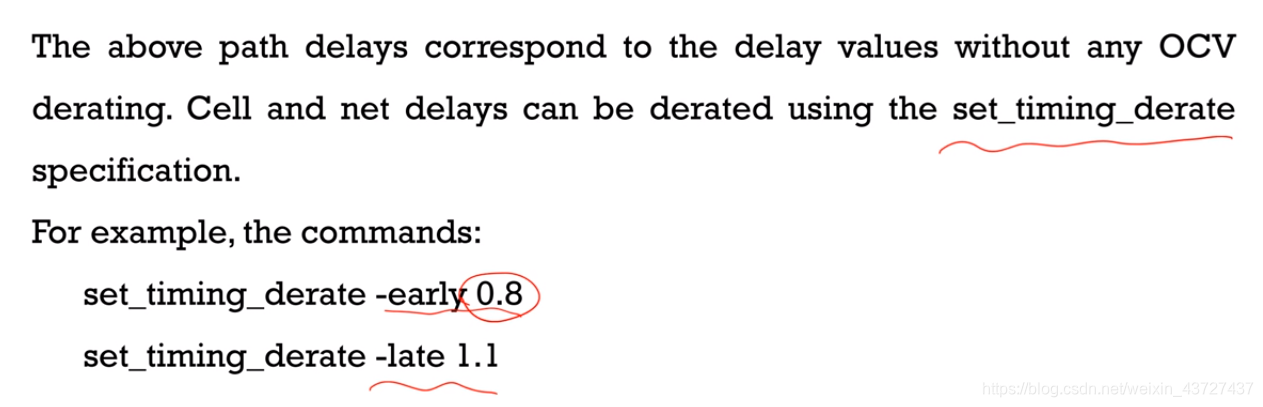

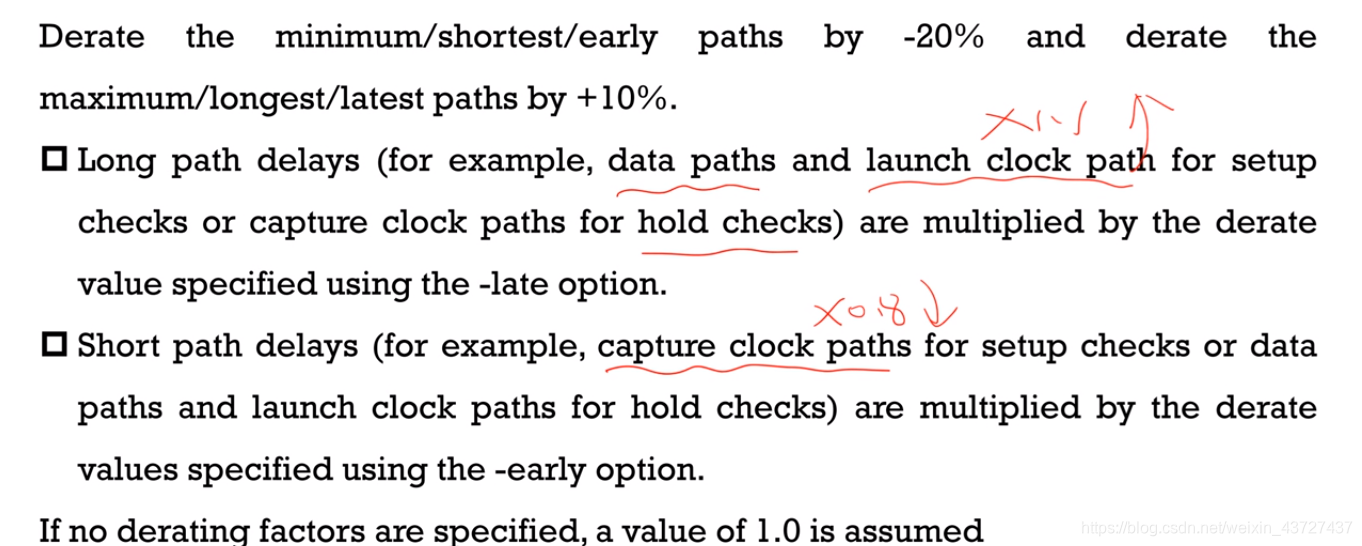

对于setup的path,让其变得更大。对于接收变得小。

set_timing_derate -cell_delay -early 0.9

set_timing_derate -cell_delay -late 1.0

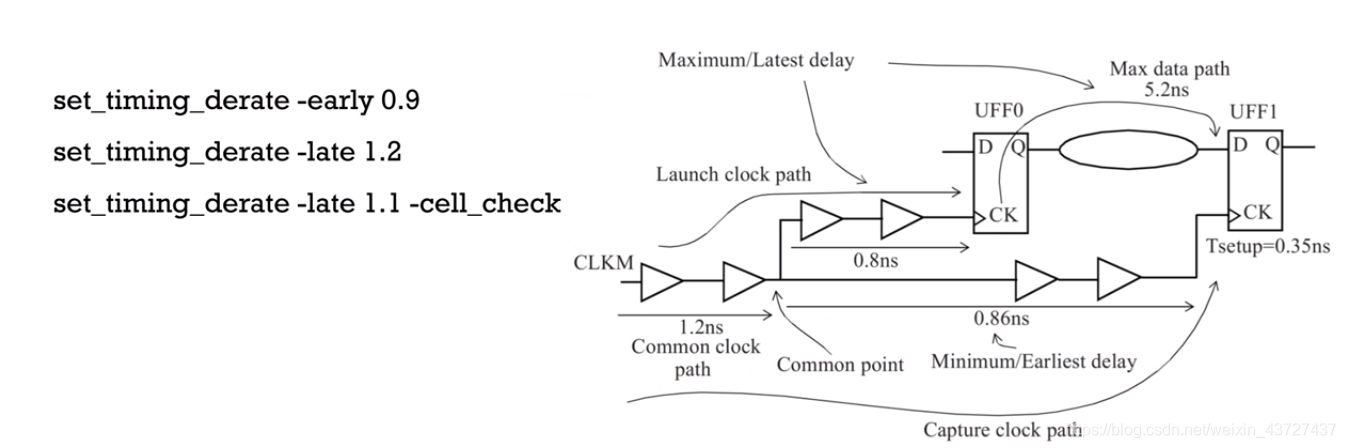

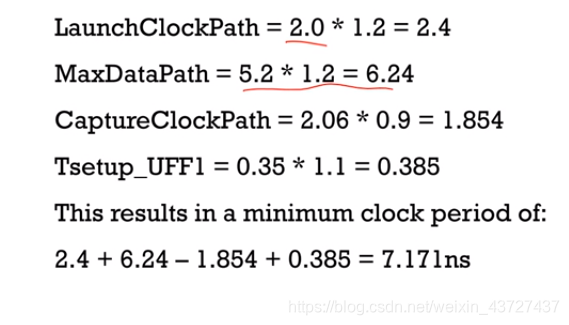

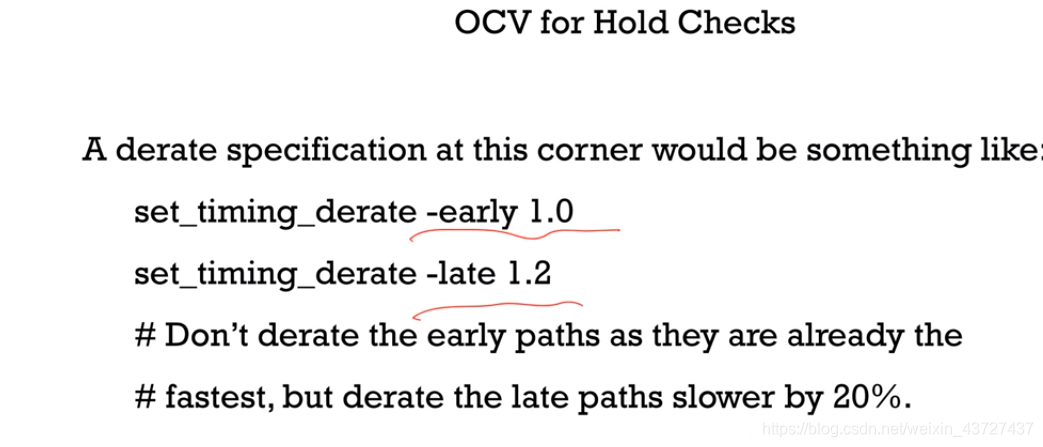

set_timing_derate -early 0.9

set_timing_derate -late 1.2

set_timing_derate -late 1.1 -cell_check

考虑OCV会让时钟变得更严苛。

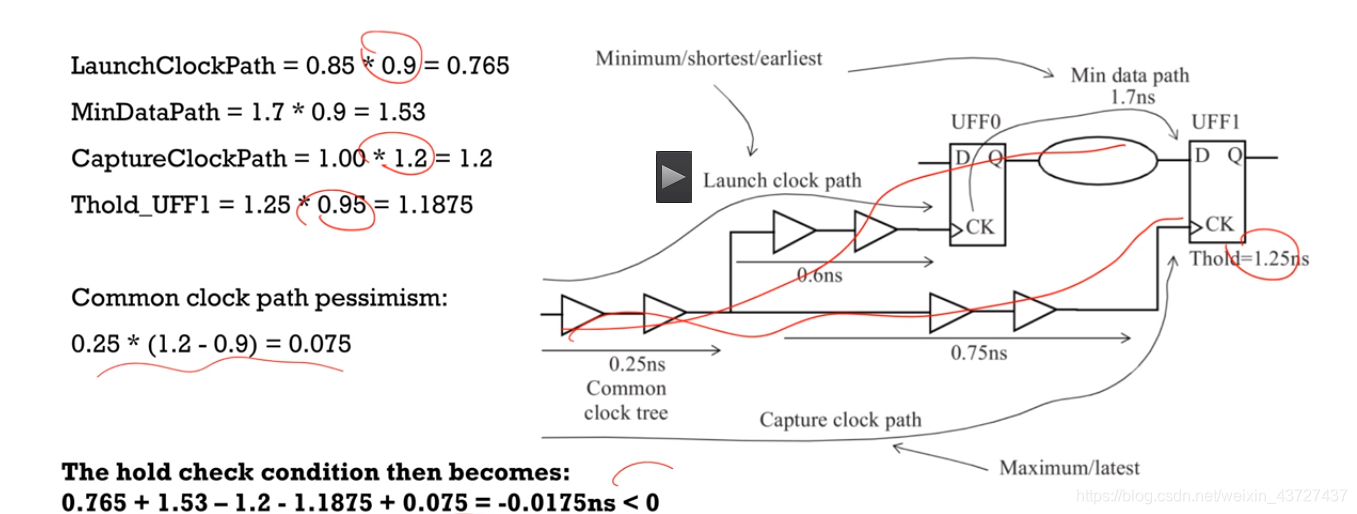

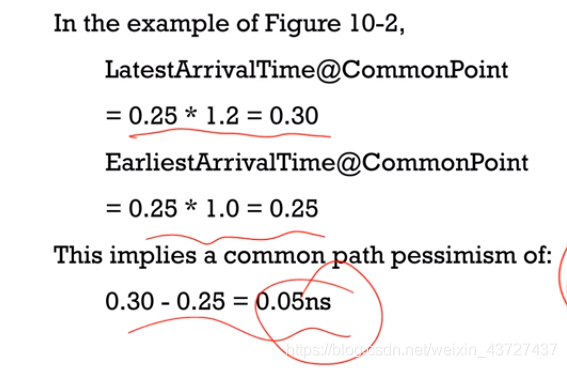

公共部分,如果重复用,那就更悲观了。

CPPR

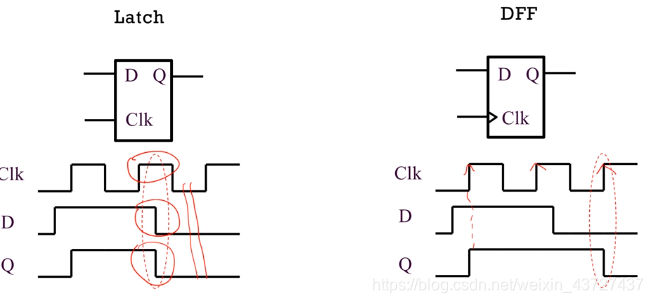

Timing Borrowing

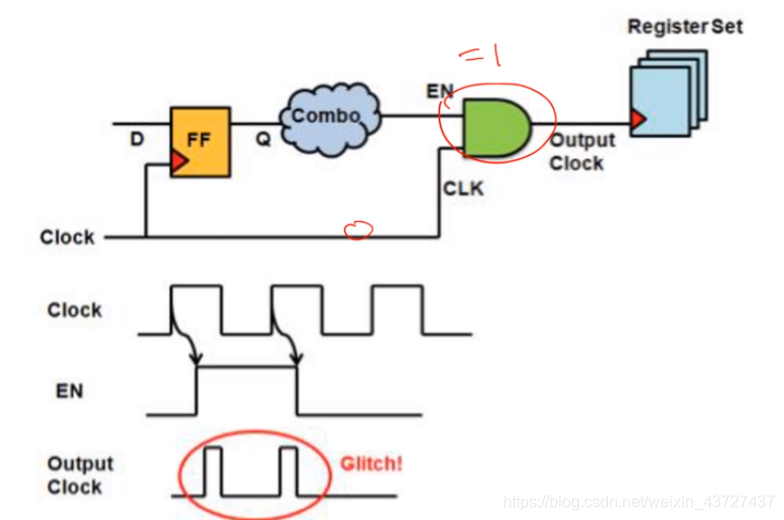

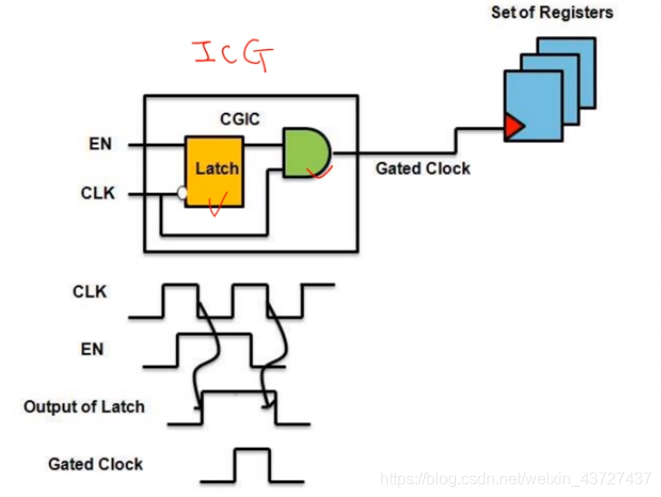

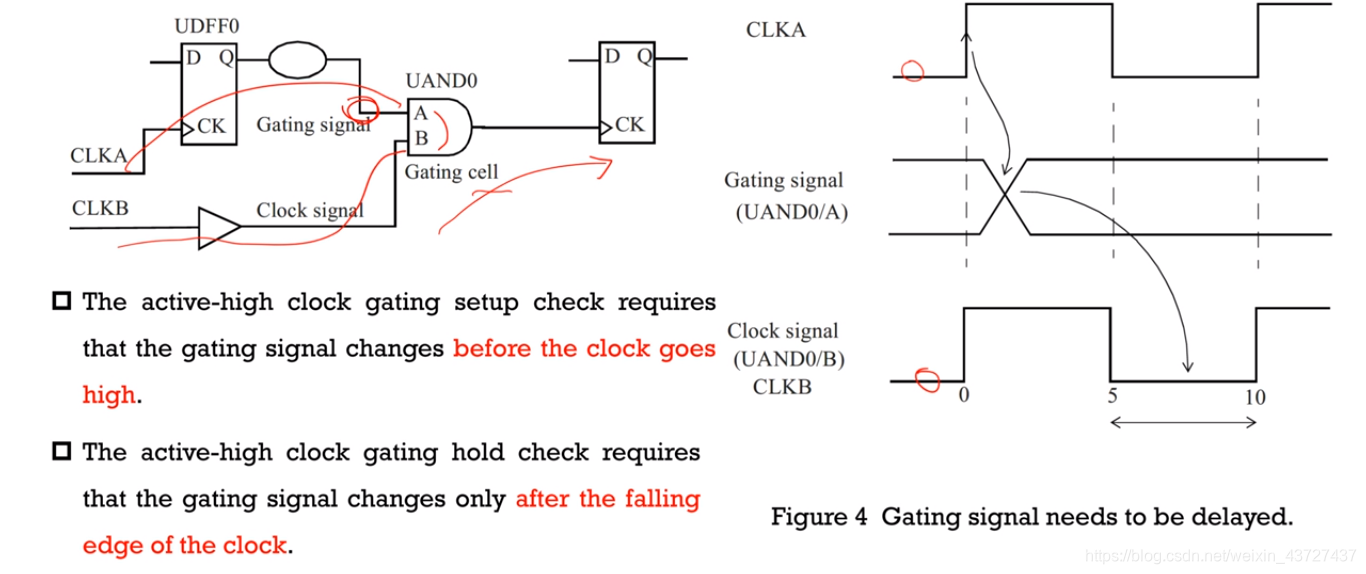

clock gating

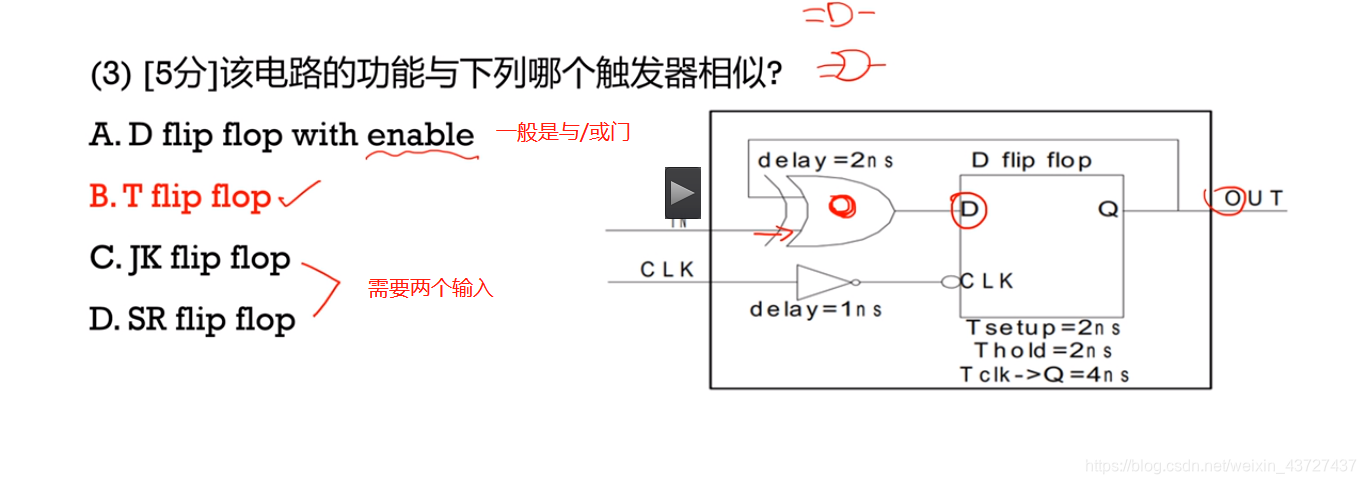

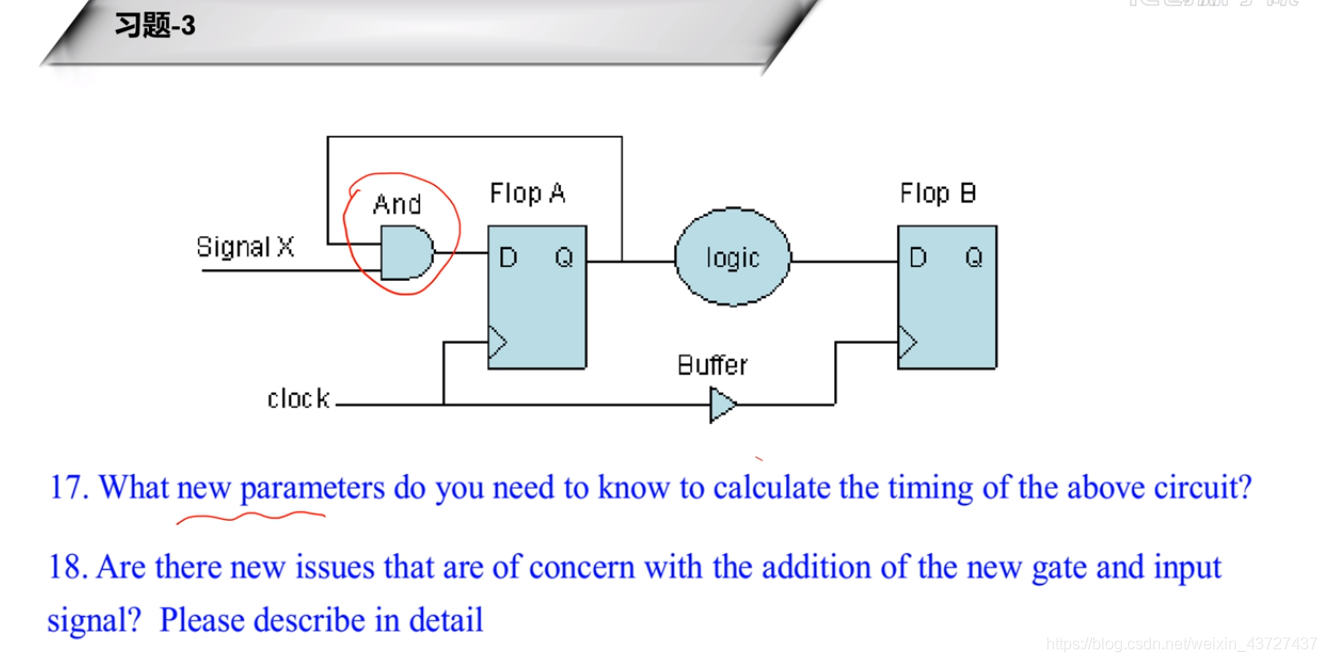

负沿的latch和一个与门。

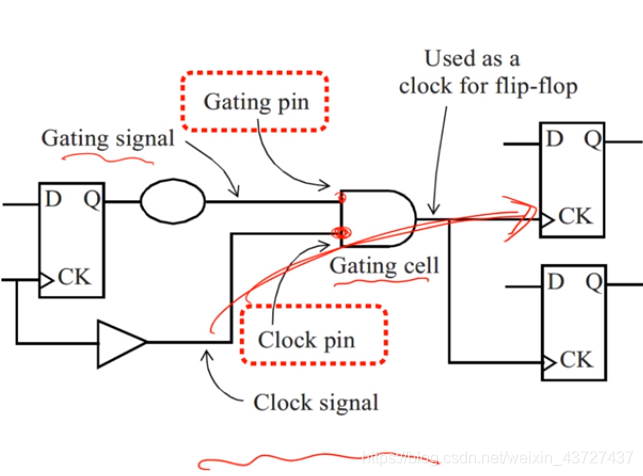

如果clock signal如果在下一级触发的D,那就不会被认为时钟信号。

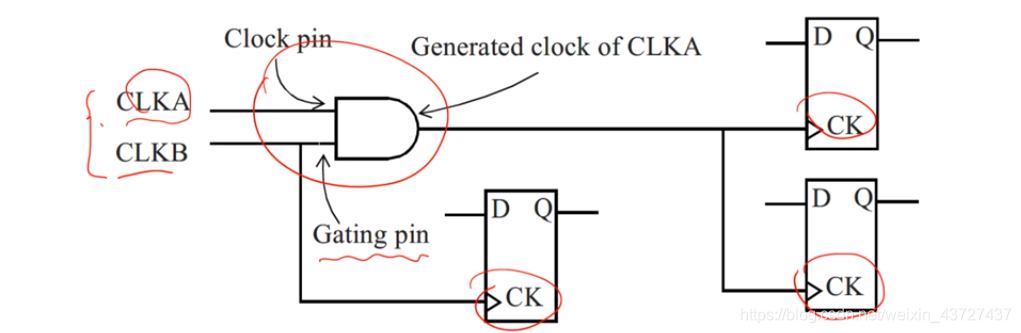

CLKA是要传输的时钟,CLKB是使能信号。

set_clock_gating_check

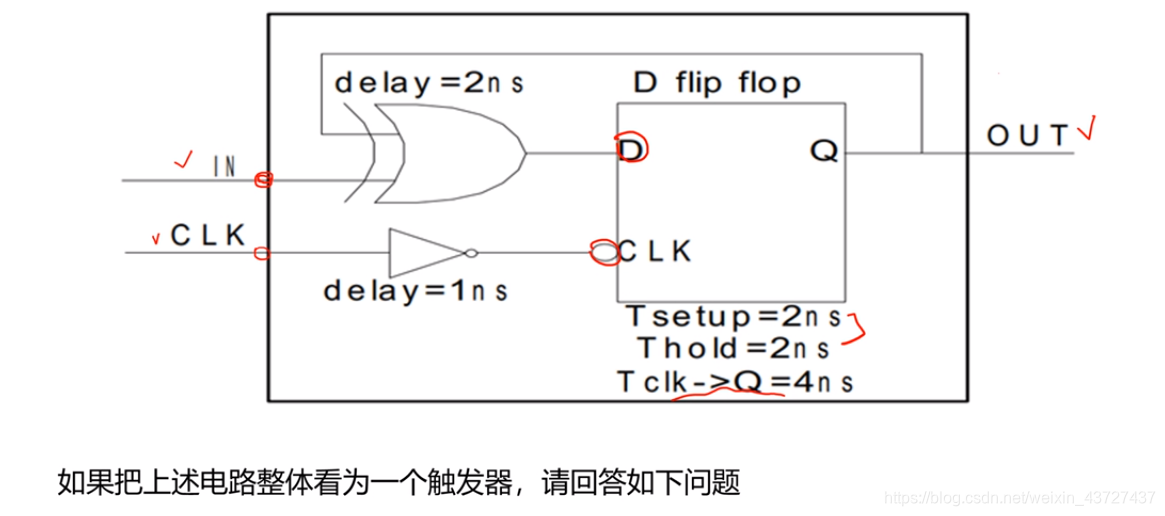

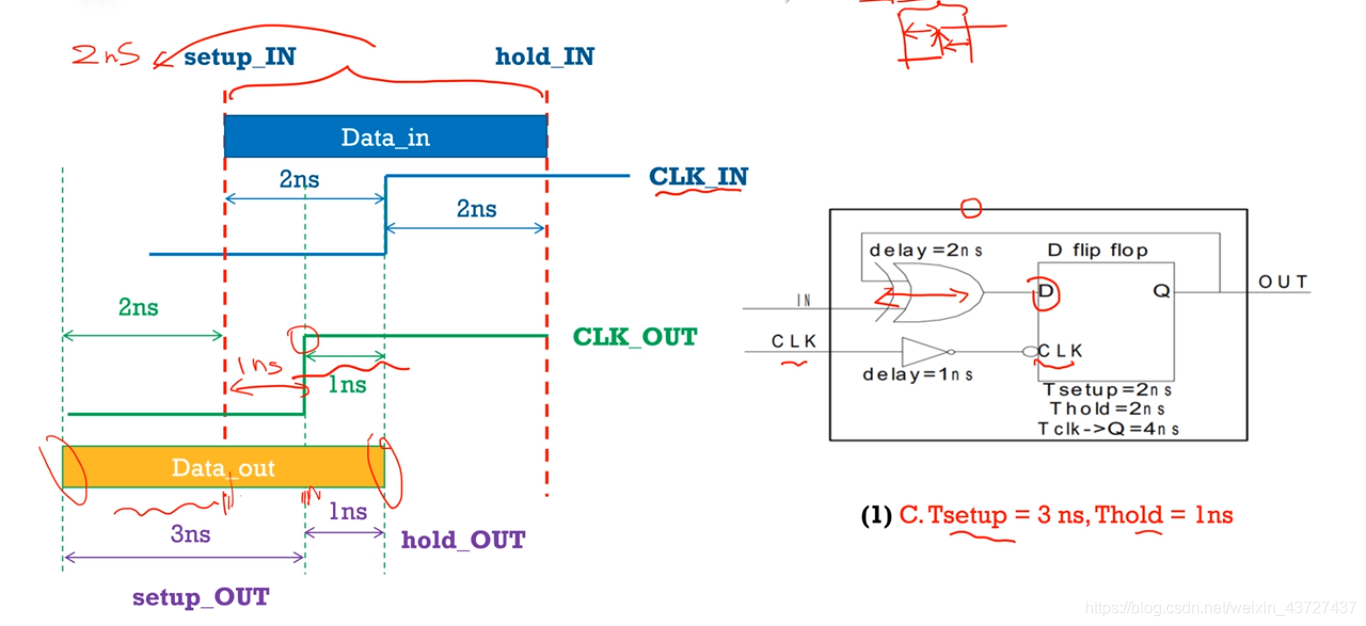

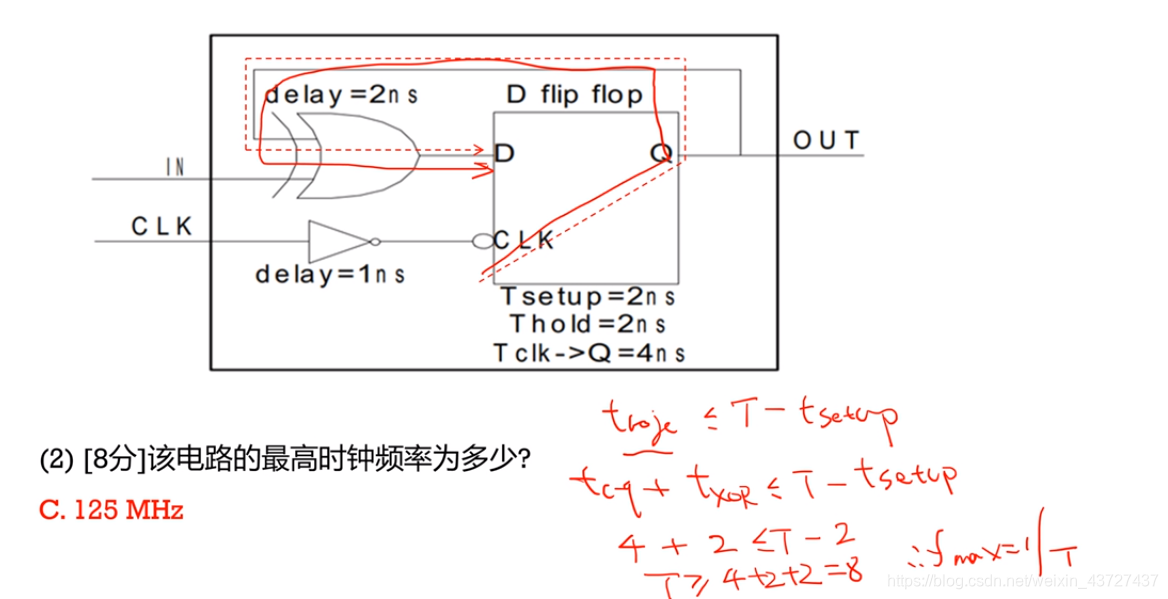

CLK_OUT指的是外面的那个CLK

Data_out指的是IN,因为数据也是经过2个ns的延迟才到D

478

478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?