ps. 写本文的目的仅为了整理笔记,好记性不如烂笔头~

参考来源:

- https://blog.csdn.net/u011729865/article/details/54138703

- https://zhuanlan.zhihu.com/p/149914903

- https://www.cnblogs.com/IClearner/p/6898463.html

- http://blog.sina.com.cn/s/blog_cdd8559a0102uycf.html

- https://mp.weixin.qq.com/s/RIlpkvitgux9AWHP5S7hKQ

- https://www.sohu.com/a/112956139_485357

- https://blog.csdn.net/mikiah/article/details/8061532

PTPX分析功耗

前言

PTPX,是基于primetime环境(简称pt),对全芯片进行power静态和动态功耗分析的工具。包括门级的平均功耗和峰值功耗。可以说PTPX就是pt工具的一个附加工具。

PT如果report_power需要额外的PTPX的licence,可以通过以下变量打开:

set_app_var power_enable_analysis true (默认是false)

PrimeTime PX支持两种功耗分析模式: averaged mode和time-based mode。

一、电路的功耗分类

功耗大致包括:total power = leakage power +internal power + switching power

(其中internal power + switch power = dynamic power)

- Leakage power,即漏电功耗和本身工艺库特性相关,由标准单元库的cell .db提供相关数据。是指cell不发生switching开关切换的时候,去计算得出。ptpx,完全使用单元库(.db文件)的漏电流功耗查找表得出结果。

(当这个模块不工作的时候,可以进行断电,从而大大降低芯片的漏电功耗。) - Internal power,内部的概念,是指cell以内。包括充放电导致的功耗和短路功耗。充放电的意思是,管子的寄生电容,导致充放电;短路功耗的意思是,栅极在切换的时候,使得P管、N管同时导通,从而引起电源到地的通路。(由标准单元库的cell .db提供相关数据,但与激励有关系。)

简单的库单元,动态功耗主要来自短路功耗。

复杂的库单元,动态功耗主要来自充放电。 - Switch power,即开关功耗,负载电容的充放电过程所导致的。具体原因:P管导通,负载电容充电;因为管子输入端口switching,N管导通,负载电容开始放电。正是由于上述充放电,导致产生了switching开关功耗。(与内部功耗的子类—充放电功耗,区别是范围不限于cell内部。)

一般情况下,需要读入SPEF文件,从而抽取每个节点上的RC参数用于计算switch power。

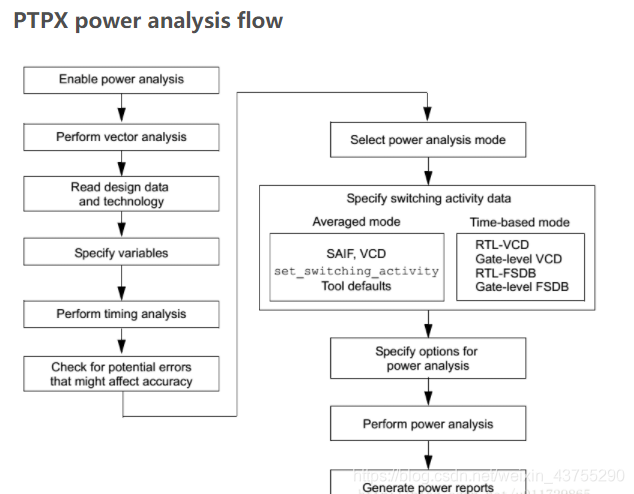

二、PTPX功耗分析模式及流程

Averaged mode: SAIF, VCD, set_switching_activity, Tool defaults

Time-based mode: RTL-VCD, Gate-Level VCD (Peak power)

1. Averaged power analysis

平均功耗,是基于翻转率toggle rate来分析的。

翻转率的标注,可以是默认翻转率、用户定义switching activity、SAIF文件或者VCD文件。功耗结果期望准确的话,首先要保证翻转率的标注要准确。这意味着需要后端布局布线、时钟树等已经完全稳定了。前期做功耗分析,可能只是一个评估作用。

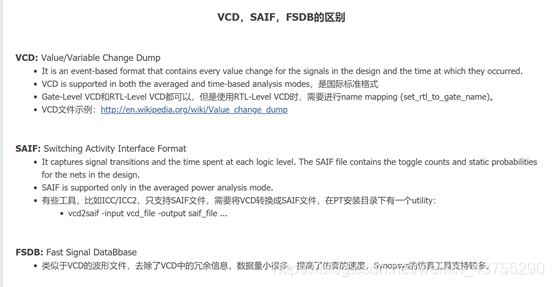

工具支持基于仿真的switching activity文件类型,包括:

- VCD

- FSDB

- VPD

- SAIF

如果没有上述文件,那可以使用user-define switching activity commands,来提供一个现实的activity去精确power结果。

所需文件:(5个)

1. logic库文件,必须是.db格式;

2. 网表文件,支持verilog、vhdl网表,db、ddc、Milkyway格式的网表也可以;

3. sdc文件,为了计算平均功耗;

4. spef文件,寄生参数信息。

5. VCD/saif文件,记录翻转率(若没有,需要人为设置翻转率)。

脚本如下(示例):

Averaged Power Analysis Mode Script:

#####################################################

# Set the Power Analysis Mode

#####################################################

set power_enable_analysis TRUE

set power_analysis_mode averaged

#####################################################

# Read and link the Gate Level Netlist

#####################################################

set search_path "../src/hdl/gate ../src/lib/snps . "

set link_library " * core_typ.db"

read_verilog mac.v

current_design mac

link

#####################################################

# Read SDC and set transition time or annotate parasitics

#####################################################

read_sdc ../src/hdl/gate/mac.sdc

set_disable_timing [get_lib_pins ssc_core_typ/*/G]

read_parasitics ../src/annotate/mac.spef

#####################################################

# check, update, or report the timing

#####################################################

check_timing

update_timing

report_timing

#####################################################

# read switching activity file

#####################################################

read_vcd ../sim/mac.vcd -strip_path tb/uut //读后仿产生的VCD/SAIF文件将真实的翻转率反标到Net上,在read_vcd或者read_saif时要注意通过-stripe_path选项指定合适的hierarchical层次,否则activity反标不上。

report_switching_activity -list_not_annotated //列出没有被反标的对象

#####################################################

# check or update or report power

#####################################################

check_power

update_power //使用update_power来将其反标

report_power -hierarchy

quit

2.Time-based power analysis

在该模式下,需要提供VCD或FSDB文件,工具会分析峰值功耗,并生成功耗波形等。SAIF格式对此不支持。

流程和Averaged类似。

脚本如下(示例):

Time-Based Power Analysis Mode Script:

#####################################################

# Set the Power Analysis Mode

#####################################################

set power_enable_analysis TRUE

set power_analysis_mode time_based

#####################################################

# link design

##############################################

set search_path "../src/hdl/gate../src/lib/snps . "

set link_library " *core_typ.db"

read_verilog mac.v

current_design mac

link

#####################################################

# set transition time /annotate parasitics

#####################################################

read_sdc ../src//hdl/gate/mac.sdc

set_disable_timing [get_lib_pins ssc_core_typ/*/G]

read_parasitics ../src/annotate/mac.spef

#####################################################

check_timing

update_timing

report_timing

#####################################################

# read switching activityfile

#####################################################

read_vcd -strip_path tb/uut ../sim/mac.vcd

#####################################################

# analyze power

#####################################################

check_power

set_power_analysis_options -waveform_format fsdb -waveform_output vcd //写出功耗分析文件,文件格式可为fsdb,out

update_power

report_power

quit

至于如何查看功耗曲线图,请待下回讲解。

二、VCS生成功耗分析文件

功耗分析文件可通过VCS仿真产生。

1. saif文件的生成

要从RTL或Netlist生成SAIF文件,需要使用toggle系统任务指定需要记录的开关活动信息(时间范围和模块)。

$set_toggle_region:指定记录模块

$toggle_start:开始记录

$toggle_stop:停止记录

$toggle_report:写SAIF文件

testbench测试平台主要是调用门级网表、SDF文件、库SAIF文件。testbench中,用$sdf_annotate(“my. sdf”, dut)命令作SDF标记,以保证时序的正确性,从而得到正确的翻转数目。

比较RTL和门级网表生成的saif文件,可以得出门级网表生成的saif文件更加具体,包含了设计中更多的开关活动信息,提高功耗分析的准确性,同时也意味着增加了Runtime。

门级网表生成的saif文件(示例):

timescale 1ns / 1ps

module MyDesign_tb;

reg clk;

MyDesign uut (

// design ports

);

initial

$sdf_annotate("MyDesign.sdf",uut)

end

always #50 clk = !clk;

initial

begin

# //read the library saif file

# //$read_lib_saif("WHATEVER_YOU_NEED.saif");

//read the design saif file

$read_rtl_saif("./MyDesign_fw.saif", "MyDesign_tb.uut");

//monitor gates=ON to record toggles

$set_gate_level_monitoring("ON");

//specify part of the design for which toggle info is collected - for entire design use UUT_DESIGN

$set_toggle_region("MyDesign_tb.uut");

//start toggle recording

$toggle_start;

clk = 0;

// Have your test bench here

........

//done toggle recording

$toggle_stop;

//write out a backward saif file

$toggle_report("MyDesign_bw.saif", 1.0e-9, "MyDesign_tb.uut");

//end simulation

$finish;

end

endmodule

(参考:

- https://mp.weixin.qq.com/s/toRkh2jSoeYHYTULQ-r2fw?st=B397D77E2F901A6470182E2907607142563FD287D2C127167DCA7562D4691409B1D86815B75C82E619BD011A6D12F096862281451DC635576AFBD5266E50929DED8B4321C296AB7B1DC801AC2AD91F380F600935C9192FCA7FEA98F7F30A6D311B417BA10BE0AE2687CB27D859BF041135D4E96D13C8033F74408760C999EB59C84F1832DDB9355969E22EC4F8DCC81C&vid=1688851264355576&cst=BDBA16244C3A60B94FADE6554CC0FD8D18E1B52B04D32BF3E18686D6C039AD6DB707E7C6063E0F146FD1B52E7560F20A&deviceid=96cb15a7-3b3f-4a05-9fe5-0b3535930007&version=3.0.36.2008&platform=win

- http://blog.sina.com.cn/s/blog_59a154290102v5tj.html)

2. VCD文件的生成

vcd文件是通过仿真得到的波形文件,里面记载着待分析模块的所有端口和内部线网的跳变信息。从而确定待分析模块的switching功耗。

门级网表生成的VCD文件(示例):

module testbench;

······

test uut(....);

initial

$sdf_annotate("test.sdf",uut)

initial begin

$dumpfile("test.vcd");

$dumpvars(0,test); //test是要记录信号的模块名,0表示抓取模块内的所有信号,1表示抓取当前层的信号

······

endmodule

总结

本文主要介绍了PTPX的两种功耗分析模式(Averaged/Timed),并给出相应的脚本,另外还介绍了如何通过VCS仿真生成saif/VCD功耗分析波形文件。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?