本代码仅供学习参考

实验要求

8位并行乘法器

主要功能要求:

-

按键1,异步复位

-

按键2,流水灯,6个数码管显示学号后六位

-

按键3,调节8位乘法器的输入X,X显示到左边前2个数码管

-

按键4,调节8位乘法器的输入Y,Y显示到中间2个数码管

-

按键5,求值,按下后,计算X乘以Y的结果,用Z表示,并显示到数码管

-

按键6,X从00开始自动递增到FF,Y从00开始自动递增到FF,计算乘法结果,输入输出均要显示,显示尽量有几秒钟的时间,能够在验收时看的清楚(不一定从0开始递增,可自行设定初值)

-

所有按键应该能够进入和退出,所有按键应消抖处理

-

数码管应采用动态扫描显示

-

其余功能可自由发挥

设计原理

分频模块

计数器记到指定值后将输出信号反转,达到分频的目的

module divided1000(clk50mhz,clk1000hz,rst);

input clk50mhz,rst;

output reg clk1000hz;

reg[31:0] count;

always@(posedge clk50mhz or negedge rst)

begin

if(~rst)

begin

count<=0;

clk1000hz<=1'b0;

end

else

if(count==32'd24999)

begin

count<=0;

clk1000hz<=~clk1000hz;

end

else

count<=count+1;

end

endmodule

module divided8ms(clk1000hz,clk8ms,rst);

input clk1000hz,rst;

output reg clk8ms;

reg[31:0] count;

always@(posedge clk1000hz or negedge rst)

begin

if(~rst)

begin

count<=0;

clk8ms<=1'b0;

end

else

if(count==32'd8)

begin

count<=0;

clk8ms<=~clk8ms;

end

else

count<=count+1;

end

endmodule

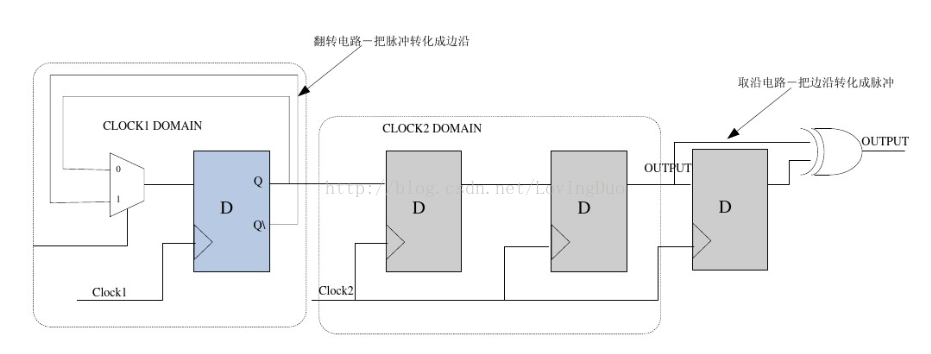

按键消抖模块

module key_handle(

input rst_n ,

input clk_8ms ,

input key , // 单个按键

input rst_sync ,

output reg key_handled

);

reg key1, key2, key_sync ; // key同步

reg key_sync_temp ;

wire key_rise ; // key_sync的上升沿

assign key_rise = !key_sync_temp && key_sync;

// 对key使用clk_8ms进行三级同步

always @(posedge clk_8ms or negedge rst_n)

begin

if(!rst_n) {key_sync, key2, key1} <= 3'b111;

else if(rst_sync) {key_sync, key2, key1} <= 3'b111;

else {key_sync, key2, key1} <= {key2, key1, key};

end

// 用于key_sync边沿检测

always @(posedge clk_8ms or negedge rst_n)

begin

if(!rst_n) key_sync_temp <= 1'b1;

else if(rst_sync) key_sync_temp <= 1'b1;

else key_sync_temp <= key_sync;

end

// 处理之后的按键

always @(posedge clk_8ms or negedge rst_n) begin

if(!rst_n) key_handled <= 1'b0;

else if(rst_sync) key_handled <= 1'b0;

else if(key_rise) key_handled <= 1'b1;

else key_handled <= 1'b0;

end

endmodule

一位全加器

module fulladder(Sum,Co,A,B,Ci);

input A,B,Ci;

output Sum,Co;

wire S1,S2,S3;

xor (Sum,A,B,Ci);//构建sum

and (S1,A,B);

xor (S2,A,B);

and (S3,Ci,S2);

or (Co,S1,S3);//构建co

endmodule

8位流水乘法器

module muli

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7931

7931

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?