Power Down Entry and Exit

首先简单介绍下LPDDR4中Power Down章节的主要内容,实际上就是介绍了两部分内容:信号要求 + 下电之前的冗余时间要求。

信号上主要是CKE(LPDDR5 Removed)为低,CS为低。

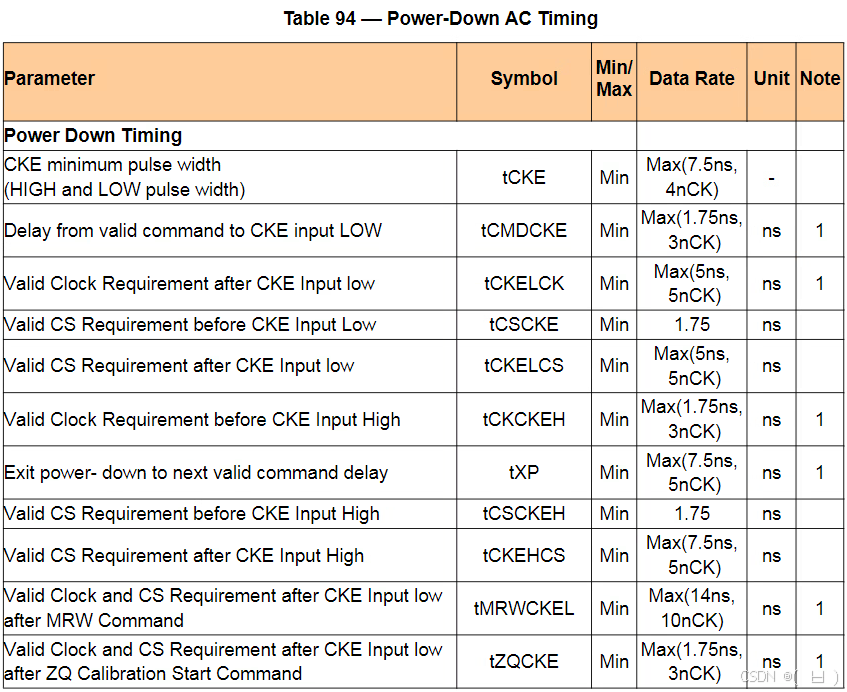

不同场景下切换到Power Down时各自需要预留给DRAM处理的时间详细信息如下:

而在LPDDR5上,因为一些信号的变化以及不同Bank Mode的配置限制,Power Down相关内容有了很多的变化。

- 通过在CLK信号的上升沿执行 CS High && CA[5:0] Low && CA6 High进入Power Down

- Power Down阶段,CS需要持续为Low保持 tCSPDmin

- Power Down阶段,CS如果Toggle会退出Power Down,可以在 tXPmin 时间内重新进入Power Down

- 如果CA/CK/CS ODT使能,则Power Down阶段会Terminate CA/CK Bus,CS ODT会强制Off(CS ODT可以通过MR11 OP[7]修改Power Down时配置)

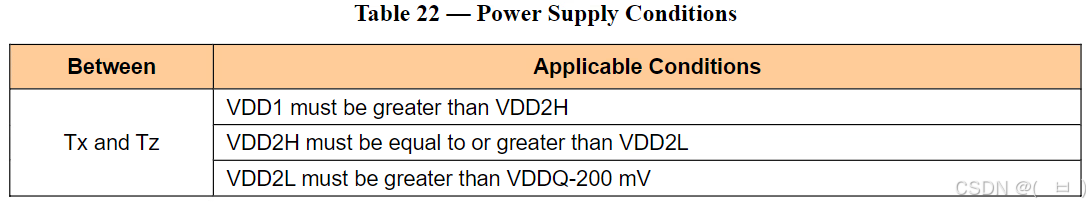

- Power Down阶段,VDDQ可以Turn Off,但是在结束Power Down阶段之前必须让VDDQ保持在工作电压,并满足下表要求

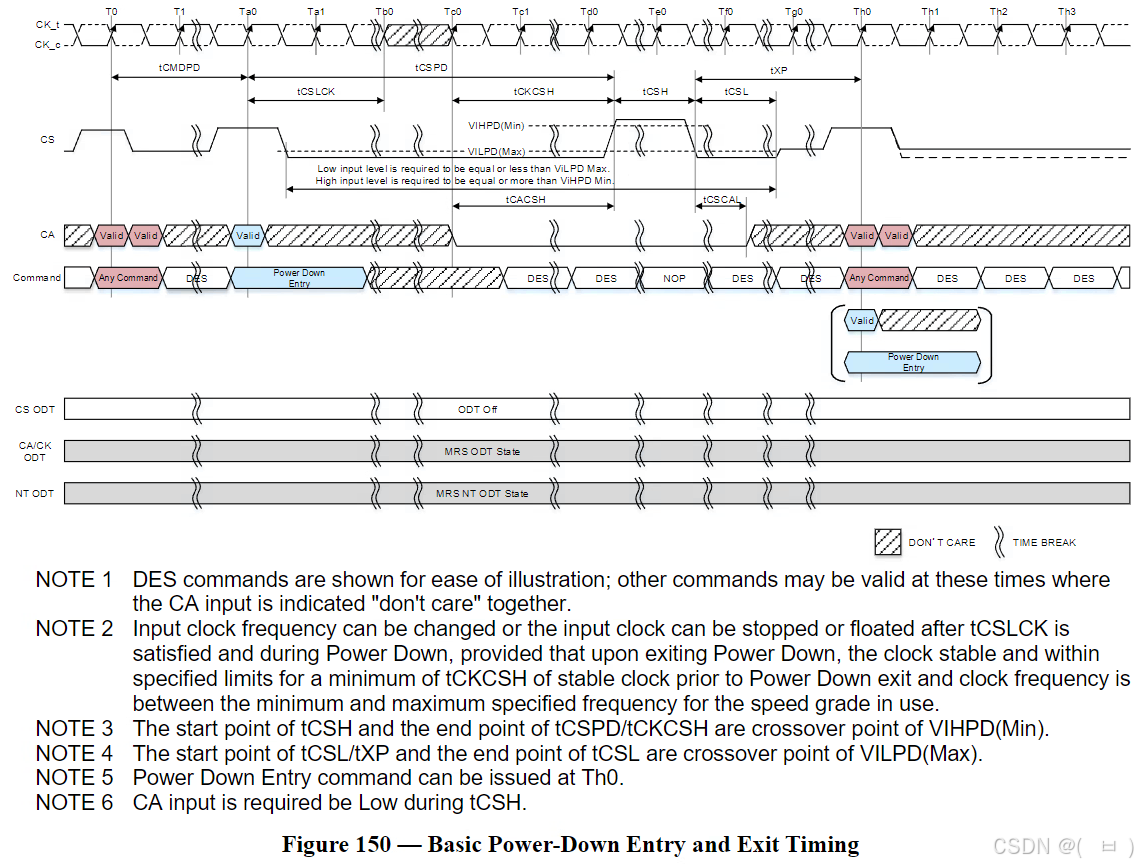

基础的Power Down时序图如下所示:

上述的相关参数信息参考如下:

- tCMDPD - 任意指令发出之后如果下一条指令是Power Down指令需要等待的时间

- tCSPD - Power Down指令发出后,CS下一次抬高之前需要的延时时间

- tCSLCK - Power Down指令发出后,CLK信号需要持续稳定Toggle的时间

- tCKCSH - CS信号重新抬高之前,CLK信号需要持续稳定Toggle的时间

- tCACSH - CS信号重新抬高之前,CA信号需要保持为Low的时间

- tCSH/L - Power Down Exit阶段CS保持为高/低的持续时间

- tXP - Power Down Exit开始,到下一条有效命令发出之前需要的延时时间

- tCSCAL - Power Down Exit阶段CA保持为低的持续时间

- VIH/LPD - Power Down阶段,CS的高/低电平数值

而不同场景下的Power Down执行之前需要等待的要求具体如下:

| Scenario | Delay Requirements |

|---|---|

| Bank Pre-Charge | tCMDPD |

| CAS(WS_FS) | tCMDPD |

| Read with NT-ODT disable | wait Read finish |

| Read with NT-ODT enable | wait ODT re-enable after Read Finish |

| Write | wait Write finish |

| ZQ Calibration | tZQPD |

| ZQ Latch | tZQPD |

| Start WCK2DQI/O Interval Oscillator | wait Internal timer end + tOSCPD |

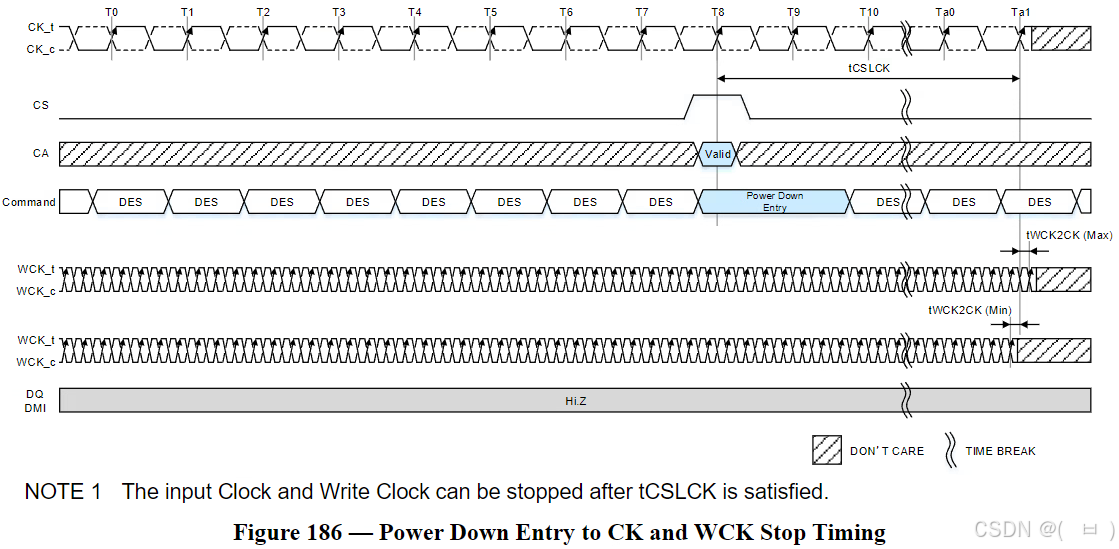

而在WCK Always-On模式下,WCK在执行Power Down/Self-Refresh/Deep Sleep之后,也有一个stop timing限制参数tCSLCK(Max(5ns, 3nCK))

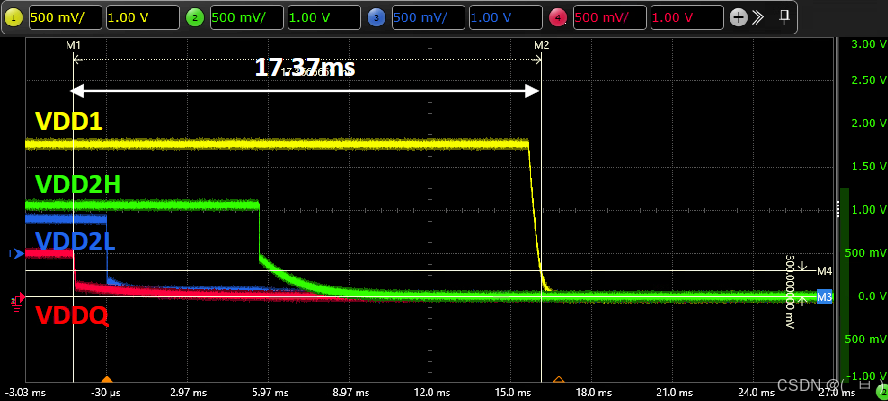

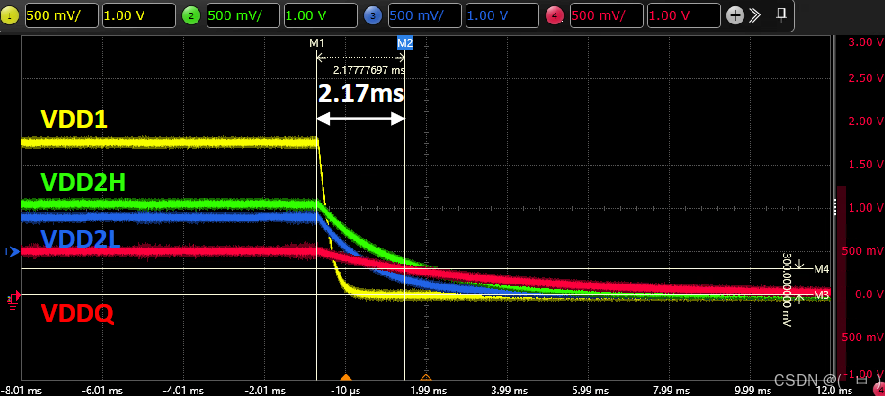

具体的Power Off SIPI测试里的掉电顺序如下:

SIPI - Controlled Power Off

DRAM收到了下电命令开始Power Off。

SIPI - Uncontrolled Power Off

拔电池这种属于Uncontrolled,类似没有收到下电Command就开始掉电。

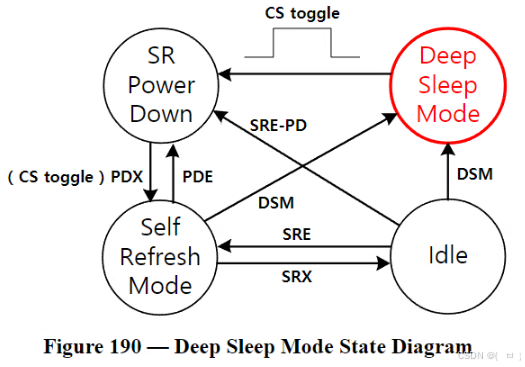

Deep Sleep

Deep Sleep Mode是一种附加的自刷新模式,具有更长的进入/退出时间,允许 SDRAM 管理内部电路以实现低电流消耗。

Deep Sleep只允许从IDLE模式,Self-Refresh模式这两个状态进入,相关状态机信息如下:

并且Deep Sleep Mode建议最小维持时间为PDN_DSM(4ms min),否则低于此时间就没有什么省电效果。

Deep Sleep模式下,DRAM会关闭除了Self-Refresh之外的大部分供电和时钟,CS ODT也需要Turn Off,并提供数据Retain的功能。

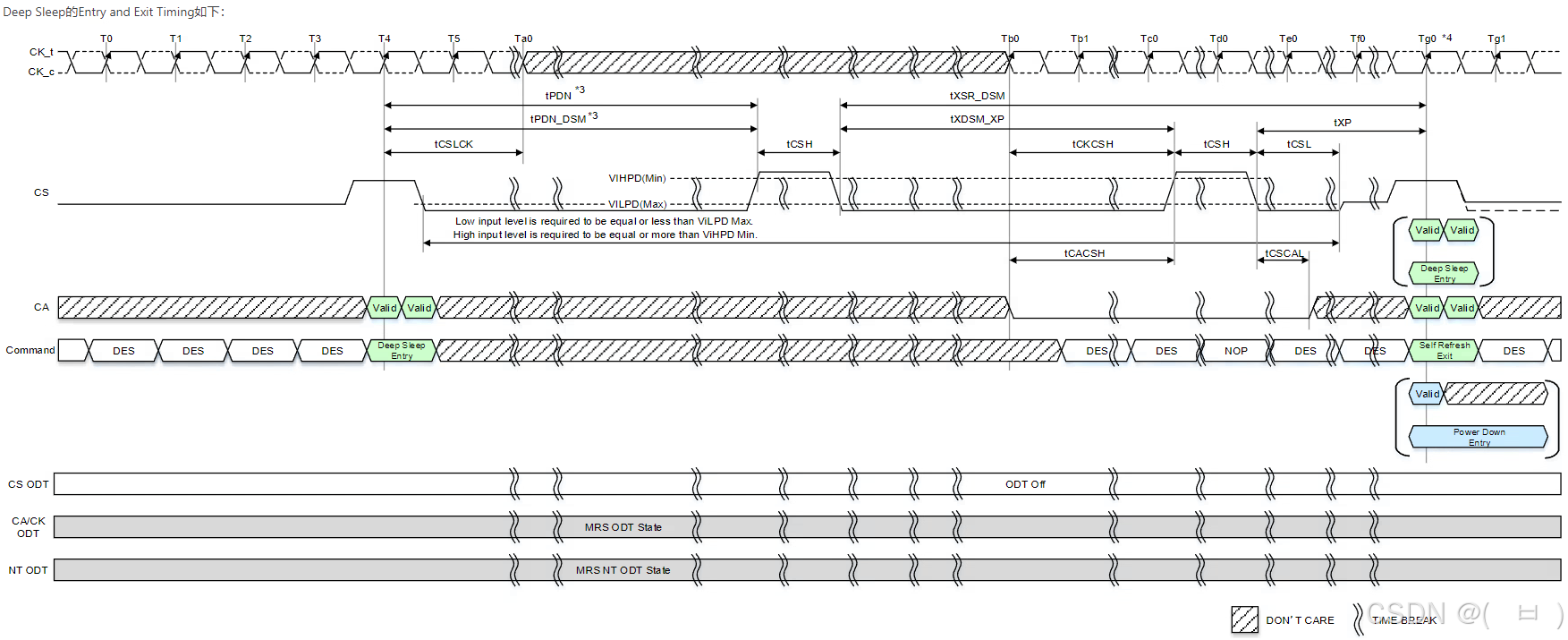

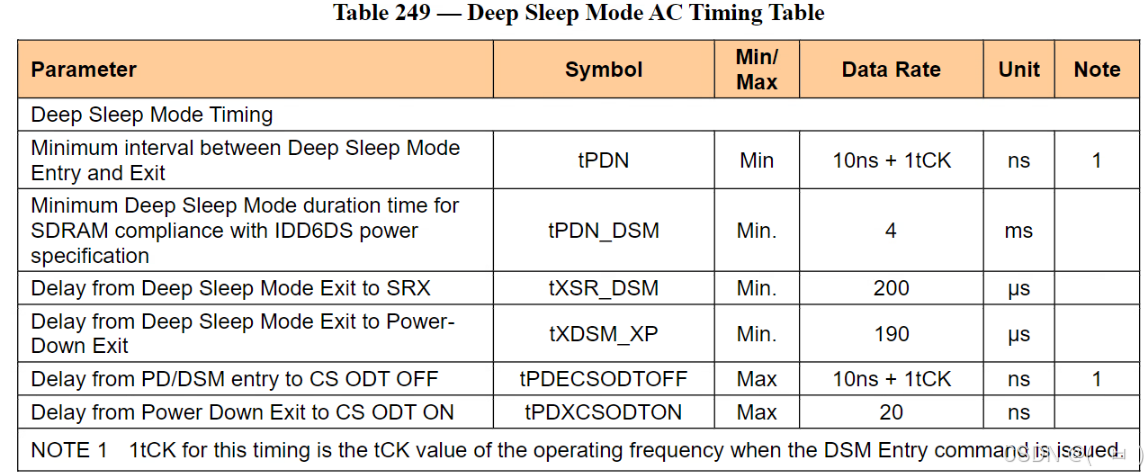

Deep Sleep的Entry and Exit Timing如下:

可以看到类似tVIHPD/VILPD/tCSH/tCSL/tCSLCK/tCKCSH/tCACSH/tCSCAL/tXP等信息都是和Power Down部分的要求是一样的,不同部分相关的参数信息如下:

159

159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?