本文主要介绍Xilinx P4的测试架构和测试结果分析。

1 测试架构

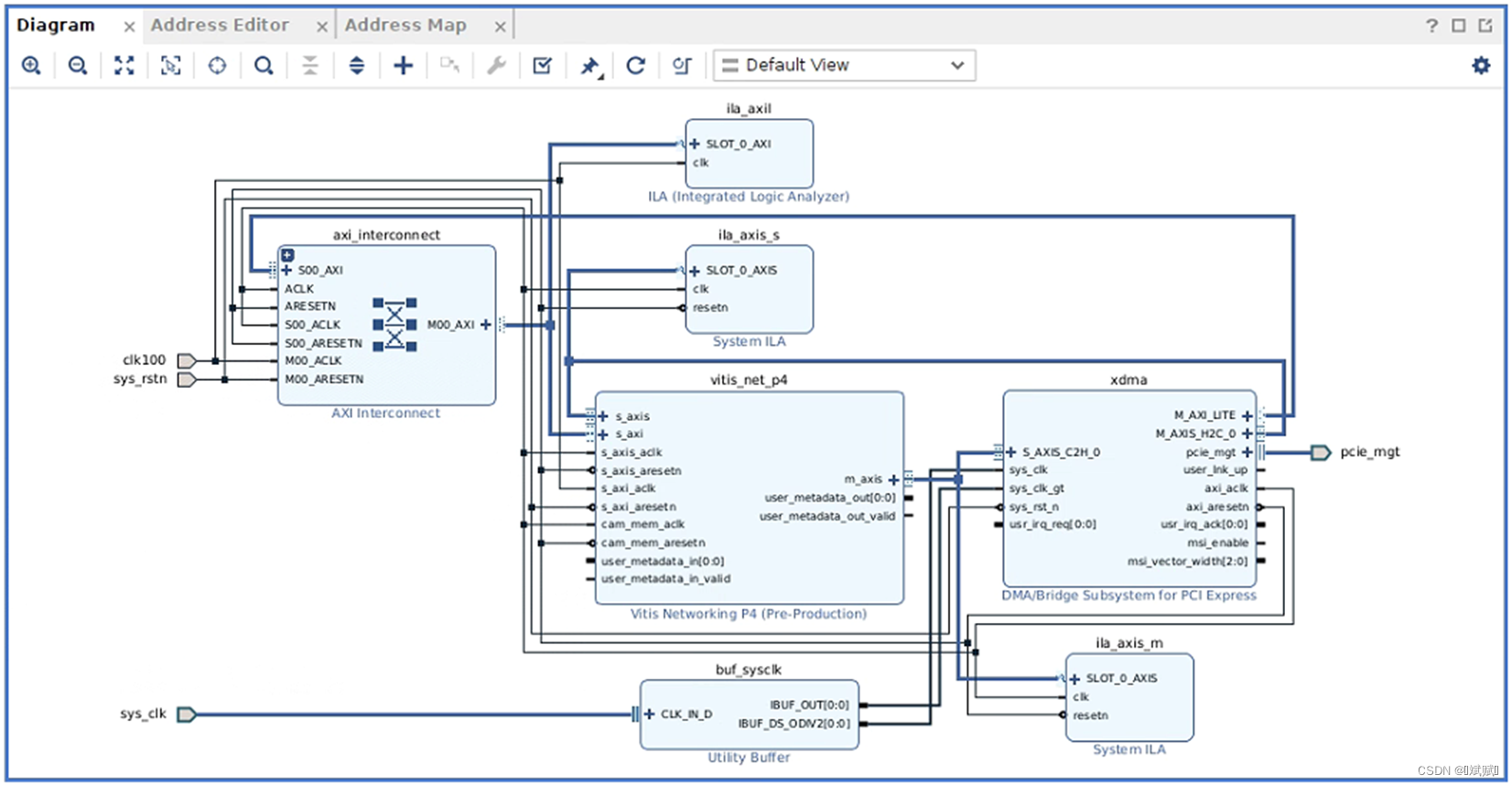

测试架构如下图所示,数据通道通过XDMA实现,通过AXI-Lite通道下载规则,通过AXI-Stream通道传输仿真数据。XDMA Stream接口的使用方法请参考Xilinx XDMA说明和测试-ST。由于P4的AXI-Lite通道的时钟频率不能超过100MHz,这儿使用一个AXI Interconnect进行时钟频率的转换,将250MHz的时钟频率转换为100MHz。驱动使用XDMA的配套驱动,使用reg_rw工具下载规则(写入地址和数据通过仿真篇的仿真得到)。使用dma_to_device工具写入原始数据流,数据流经过P4处理后使用dma_from_device读出处理后的数据流。

- 写入规则

规则的写入通过XDMA驱动工具reg_rw实现,在仿真的时候得到了从AXI-Lite总线写入P4的规则对应的地址和数据,这儿仿造这个流程,通过reg_rw工具往同样的地址写入相同的数据,如下所示,这儿写入的是两条规则。

./reg_rw /dev/xdma0_user 0x1000 w 0x0000047f

./reg_rw /dev/xdma0_user 0x1800 w 0xaa201011

./reg_rw /dev/xdma0_user 0x0200 w 0x24116cc1

./reg_rw /dev/xdma0_user 0x1800 w 0x988880fd

./reg_r

订阅专栏 解锁全文

订阅专栏 解锁全文

392

392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?