参考:UG472.Ch3

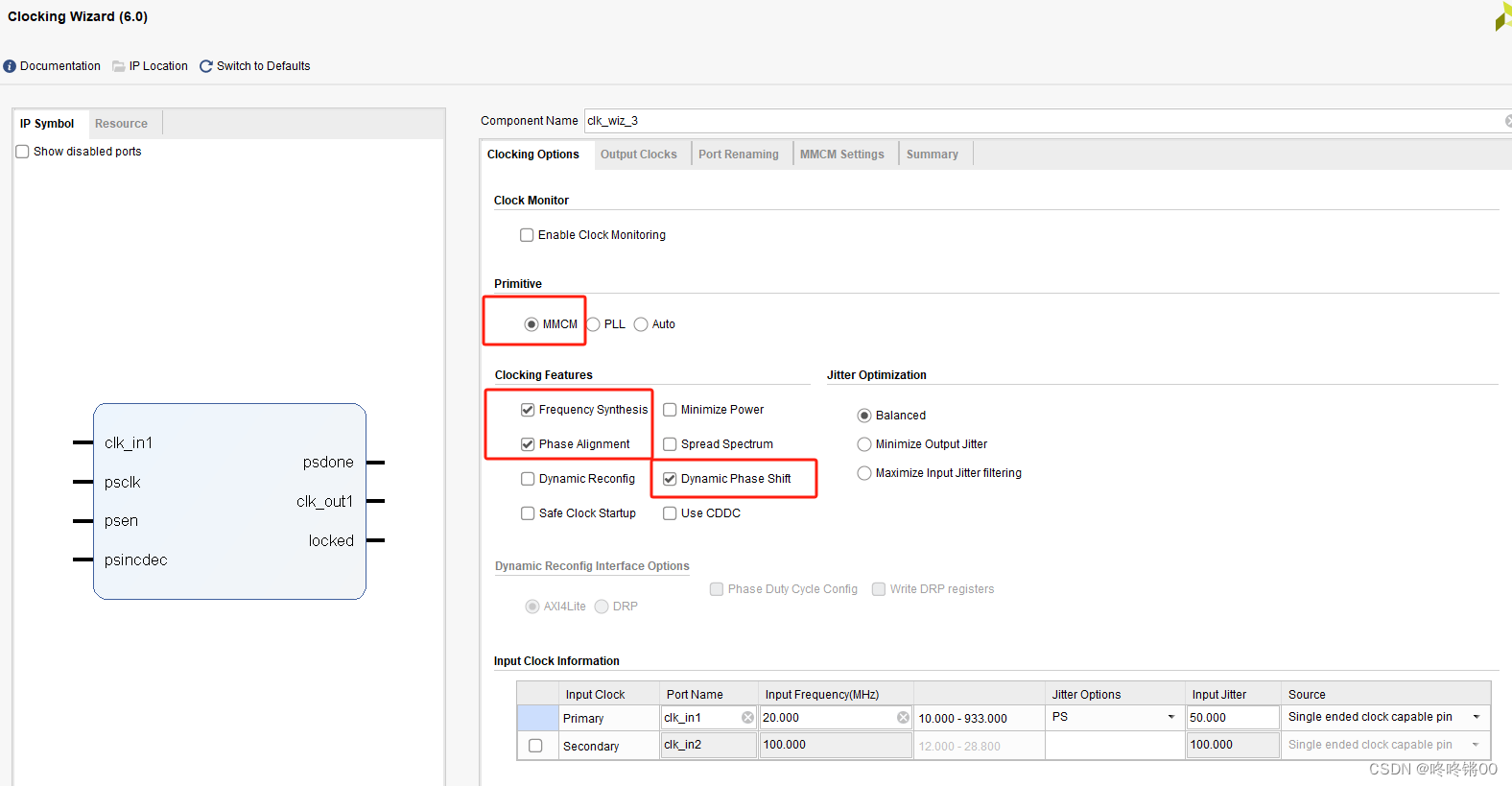

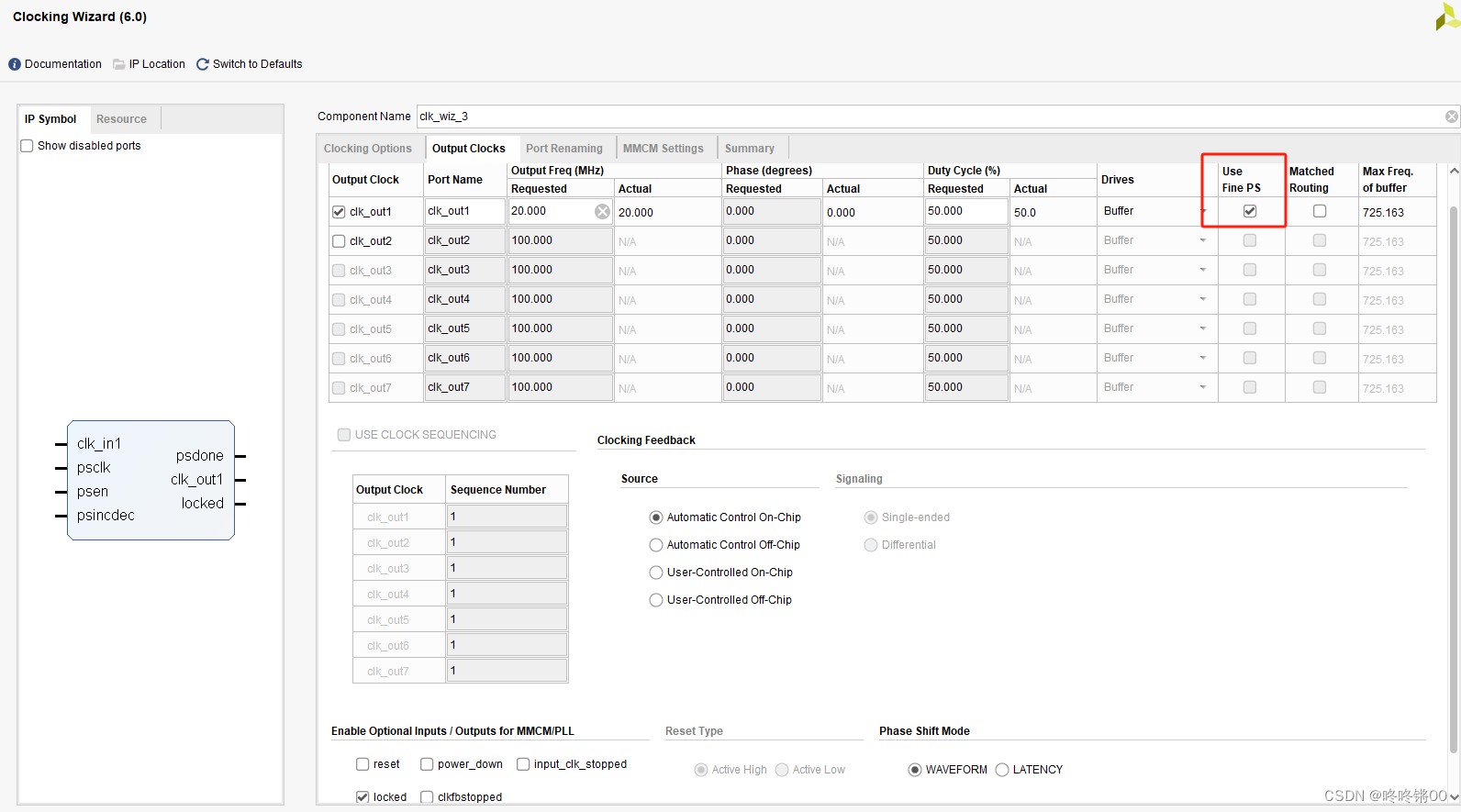

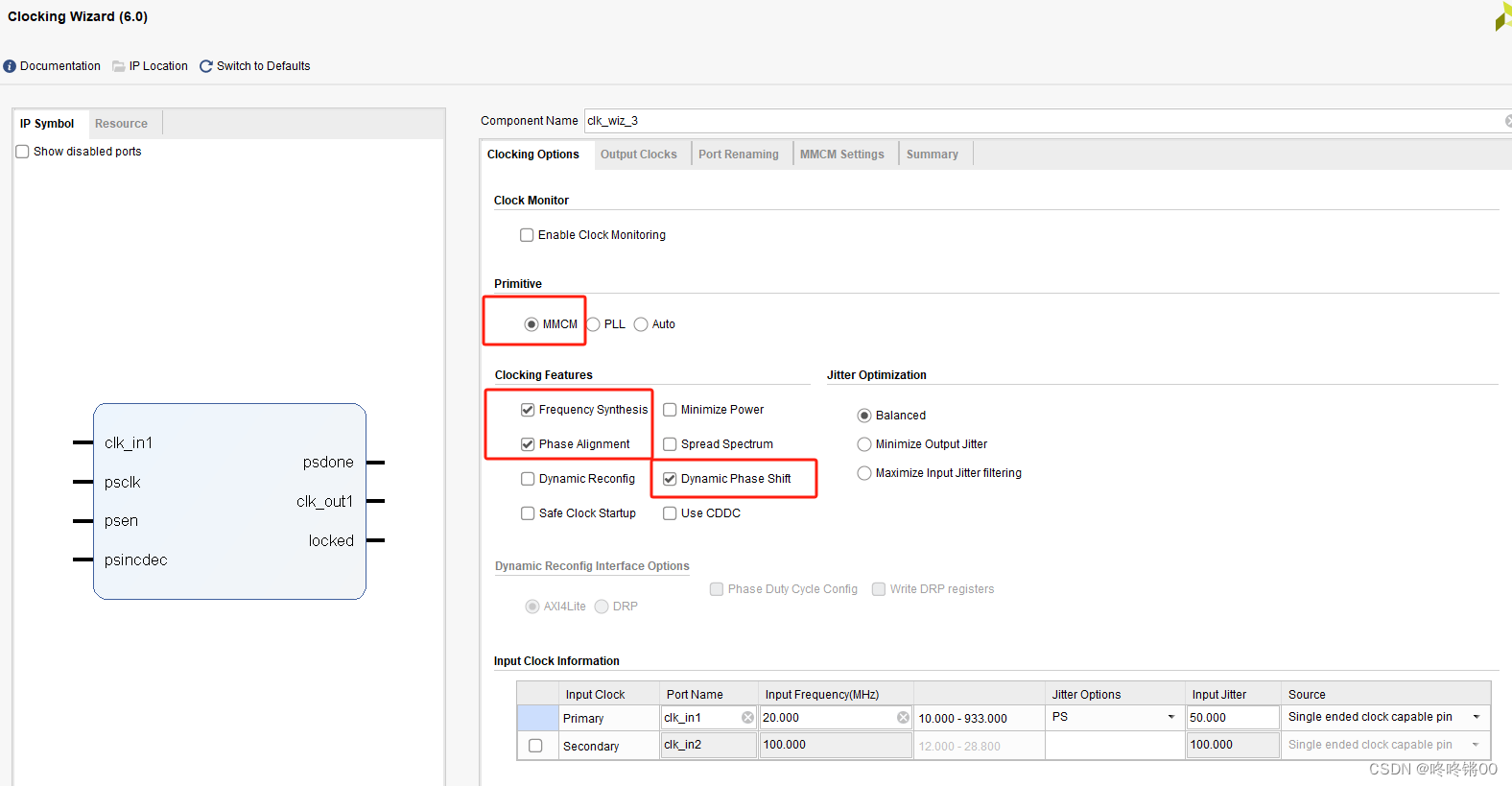

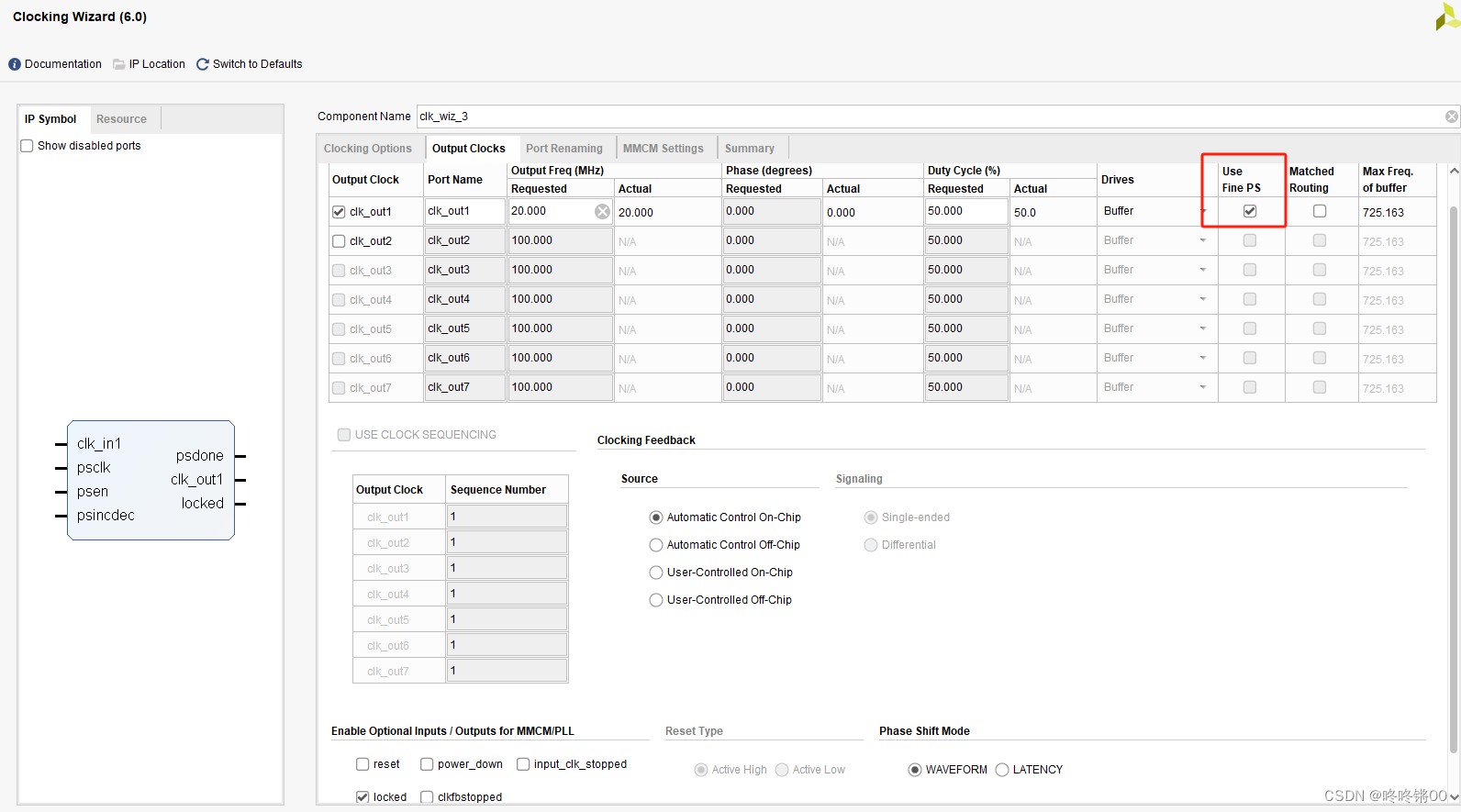

UI设置:

当PSINCDEC为 高 电平时,每来一个psen脉冲,输出时钟相位相对于输入 增加 ;

当PSINCDEC为 低 电平时,每来一个psen脉冲,输出时钟相位相对于输入 减少 ;

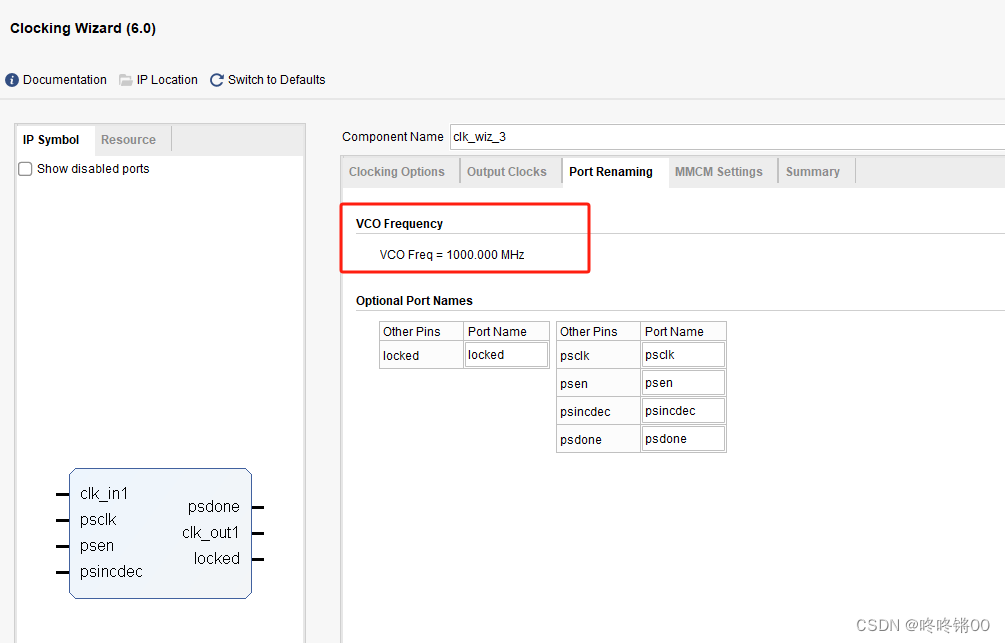

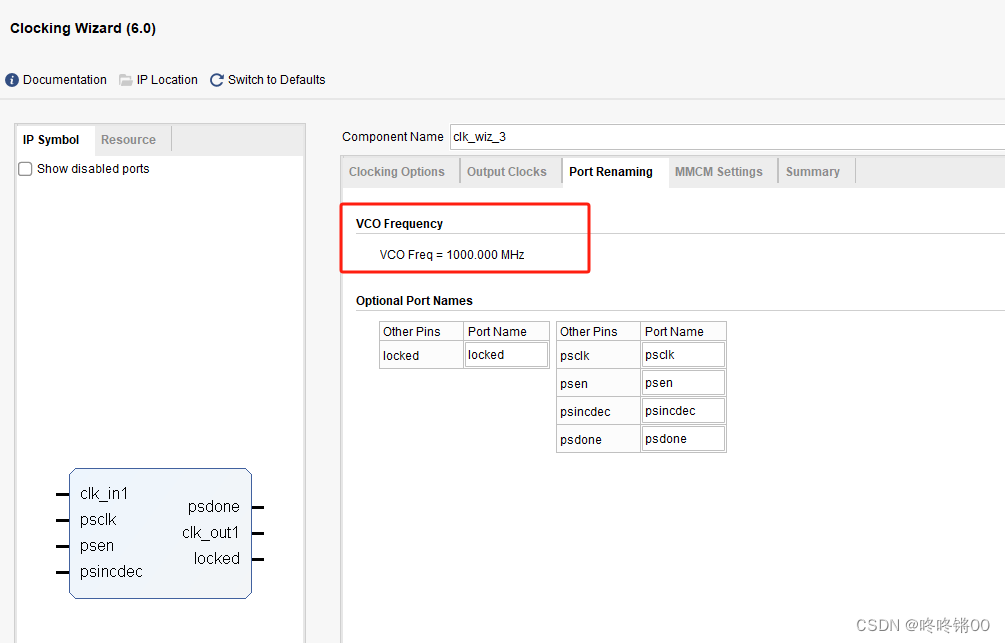

一次psen脉冲引起的时钟相位偏移量为VCO 震荡周期的

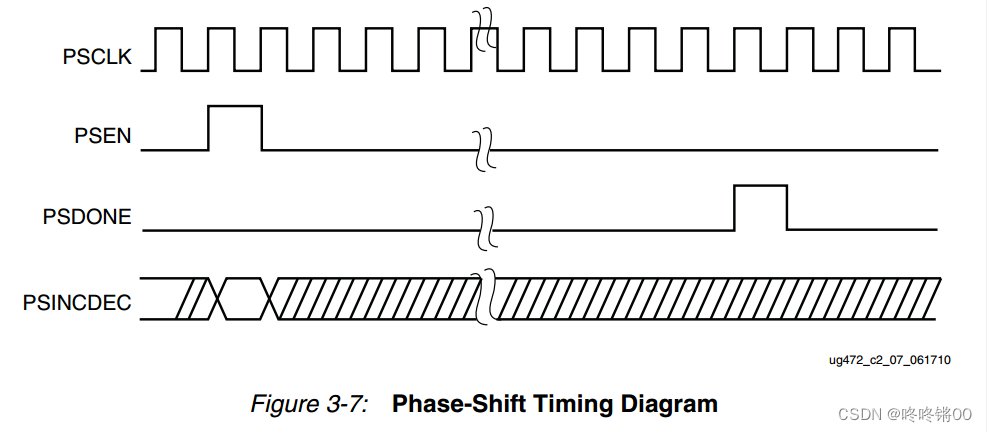

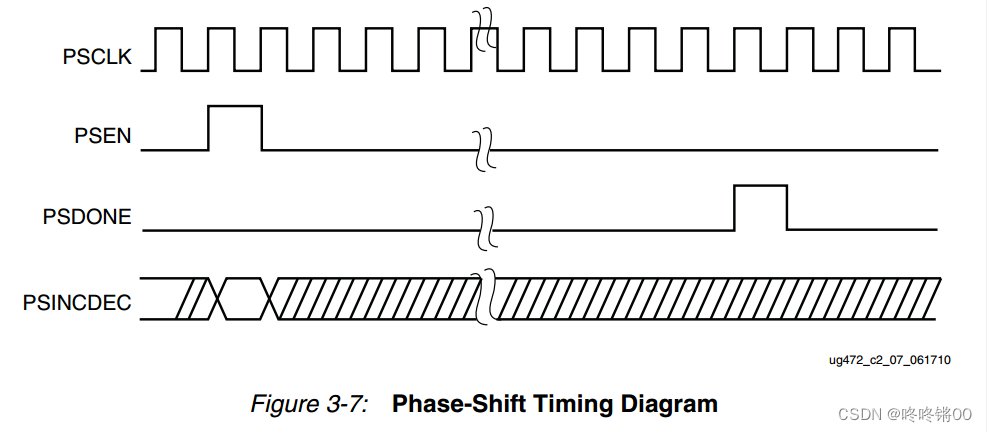

psen脉冲后的12个PSCLK周期相移完成,然后psdone拉高一个时钟周期

支持360°调相,调相满一个整周期后并不会出错或停滞,而是进入下一个周期的调相循环

参考:UG472.Ch3

UI设置:

当PSINCDEC为 高 电平时,每来一个psen脉冲,输出时钟相位相对于输入 增加 ;

当PSINCDEC为 低 电平时,每来一个psen脉冲,输出时钟相位相对于输入 减少 ;

一次psen脉冲引起的时钟相位偏移量为VCO 震荡周期的

psen脉冲后的12个PSCLK周期相移完成,然后psdone拉高一个时钟周期

支持360°调相,调相满一个整周期后并不会出错或停滞,而是进入下一个周期的调相循环

1万+

1万+

1495

1495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?