我还是不想写这个。。

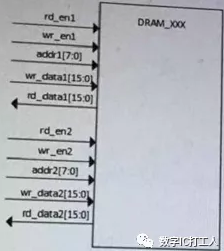

1、[简答题] 某RTL design中使用了如下256 x16 memory:

该memory有两组读写接口,每组读写接口均可独立进行write/read操作,其timing示例如下,write/read均在2个cycle后完成。

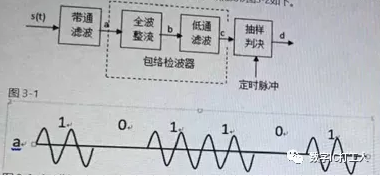

2、[简答题] s(t)为fsk调制信号s(t)=x(n)sin(w1t)+x'(n)sin(w2t), {w1>w2},x(n)={1,011,01).带通滤波的通带为w1±a,0<(w1-w2)/2图3-1给出包络检波的解调框图,请画出b,c,d各点的波形,a点波形图3-2如下。

3、[简答题]动态功耗和静态功耗分别指的是哪些?可以通过什么方法降低? (10分)

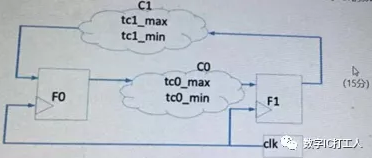

4、[简答题] (15分)

1)请解释什么是input delay,什么是output delay?可以通过作图等方式来解释。

2)有如下图所示电路示意图,已知clock-2-Q的delay为1.5ns,时钟周期T=12ns,F0与F1之间的skew为1ns,setup time为1ns,hold time为05ns,为保证电路不会出现setup time violation和hold time violation的情况,求tc0_max, tc0_min, tc1_max,tc1_min

3)什么是OCV,为什么要使用OCV,并在所示的电路示意图中指出哪些路径受到OCV的影响?

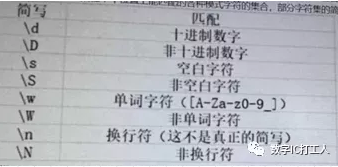

5、[简答题]正则表达式描述了一种字符串匹配的模式,可以用来检查一个串是否含有某种子串、将匹配的子串替换或者从某个串中取出符合某个条件的子串等,字符集是指在单个位置上能匹配的各种模式字符的集合,部分字符集的简写形式如下图所示。

请问:“\W*\s*input\s*wire\s*(\[\d+\:\d+\)*\s*(\w+)\s*”可以匹配到下边哪个或哪些选项? (5分)

A. input wire [3:0] num1

B. // input wire num2

C. // input wire [WIDTH-1:0] num3

D. Input wire [10:0] num4

E. input wire [BIT:0] num5

6、[简答题]针对近年来参与的一个项目进行说明

a.说明项目整体情况,及你所负责的内容。(可附框图) (2分)

b.开发过程中的最大挑战是什么? (3分)

c.当时是怎么处理这个挑战?如果重新来过,你可能会怎么处理? (5分) (10分)

7、[简答题] Verilog开发。

当A、B两组的信号请求访问某个模块时,为了保证正确的访问,需要对这些信号进行仲裁。请用Verilog实现一个仲裁器,对两组请求信号进行仲后,要求:

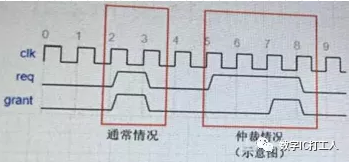

协议如图所示,请求方发送req(request)信号1表示有请求给仲裁器,仲裁器响应grant信号为1表示请求成功:

通过参数定义在冲突情形下,响应A/B的比例

(举例,一段时间内,有若干次A请求和若干次B请求,其中A&B发生冲突的有N次,这N次中先响应A 3次,后响应B 1次,循环反复。举例中的3和1可配置。);

添加必要的注释,增加代码可读性。(15分)

8、[简答题]用C语言统计100~1000里面共有多少个素数,并且把所有素数打印出来。素数又称质数。所谓素数是指除了1和它本身以外,不能被任意整数整除的数. (15分)

2400

2400

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?