文章目录

**

一般芯片旁边为什么都会放一个小电容,而且大部分情况下都是100nF

**

1、为什么要放这个电容

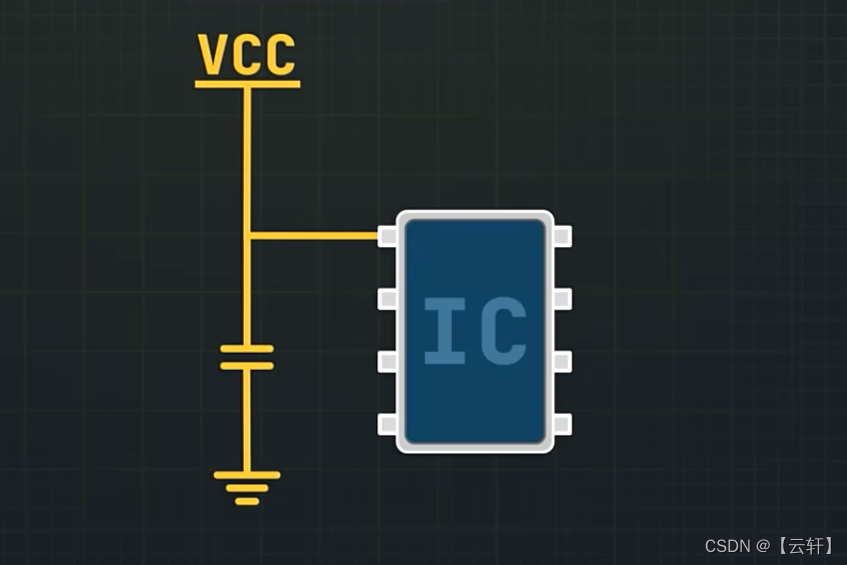

首先我们知道这个电容是接在芯片的电源引脚,芯片的供电来自电源模块【DCDC或LDO】,而这些电源模块的输出正常来说已经加了电容进行滤波,所以就没必要在芯片引脚加电容了啊。

再稍加分析我们发现:

1、芯片一直在工作的,而且每个时间段内的耗电流不一致;

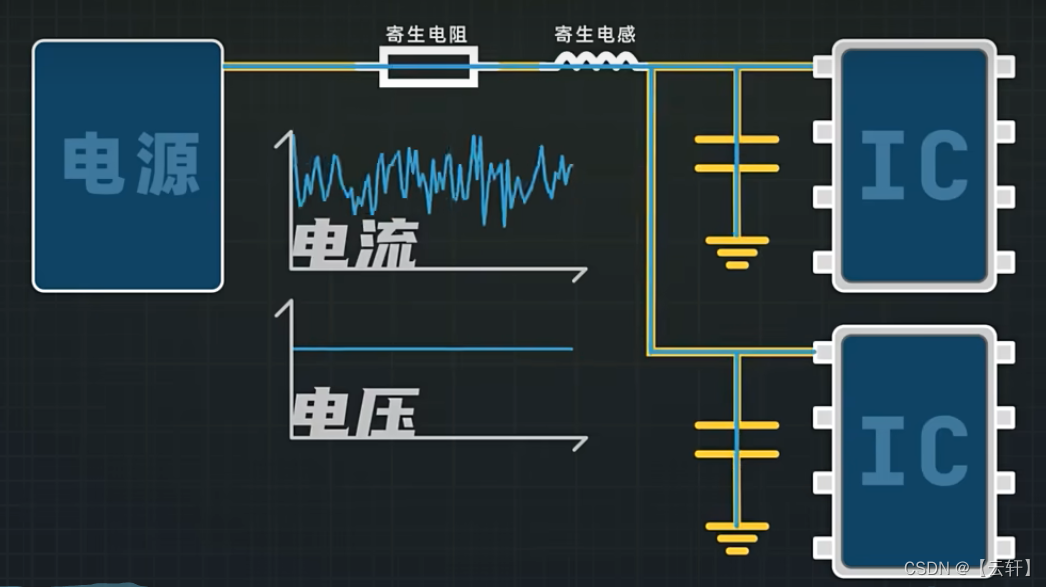

2、电源模块到芯片是有走线的,有走线就会有阻抗【寄生电阻和寄生电感】;

当芯片工作时,耗电流大,在加上电感电阻的影响,芯片供电引脚的电压会被拉低;当芯片待机,耗电流小,电压又恢复正常,如此一会工作一会待机【比如操作eeprom】,电压就被污染了。

此时如果有一个水库【电容】,就可以避免此操作。

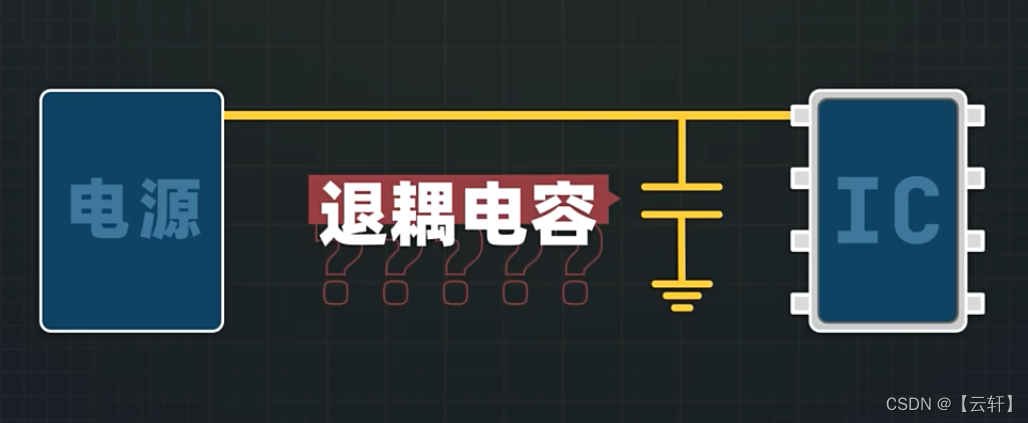

2、退耦电容是什么意思

退耦电容中的耦,指的是两个元器件间的相互影响。

如果两个芯片离得很近离电源模块有一段距离,那么上面所说得污染的电压就会在这两个芯片间来回被持续污染,本来好好得芯片也给整坏了。

如果此时,加了在电源引脚加了一个水库【电容】,不管芯片干【需要得电流多】还是涝【需要得电流小】都能自给自足,那不就解决了芯片间得影响,实现了退耦得效果。

所以要放这个电容。

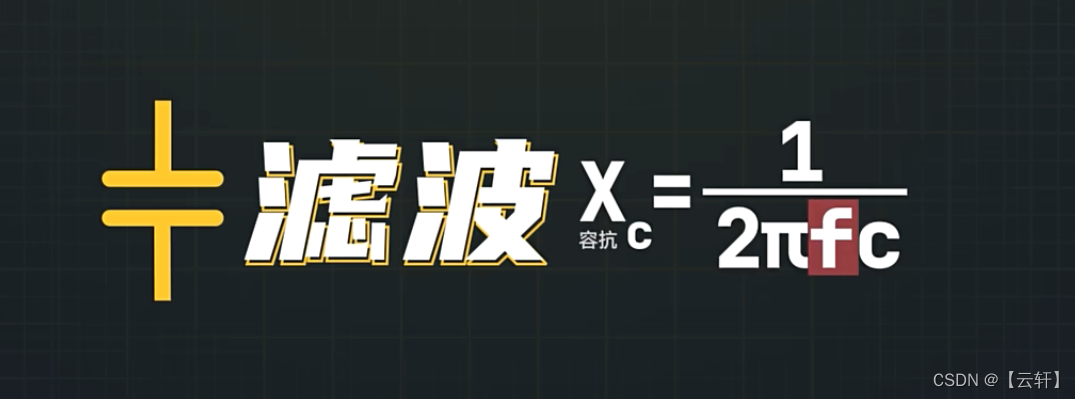

3、为什么是100nF

这个没用硬性规定,严谨的来讲,应该根据当前芯片电源引脚上的噪声频率,去选择合适的电容。

只是说100nF的电容基本满足设计要求,可以滤除绝大部分的高频噪声,再加上使用的人多,量大,成本价格自然就下来了,所以性价比较高,使用广泛。

4、为什么要大电容并小电容

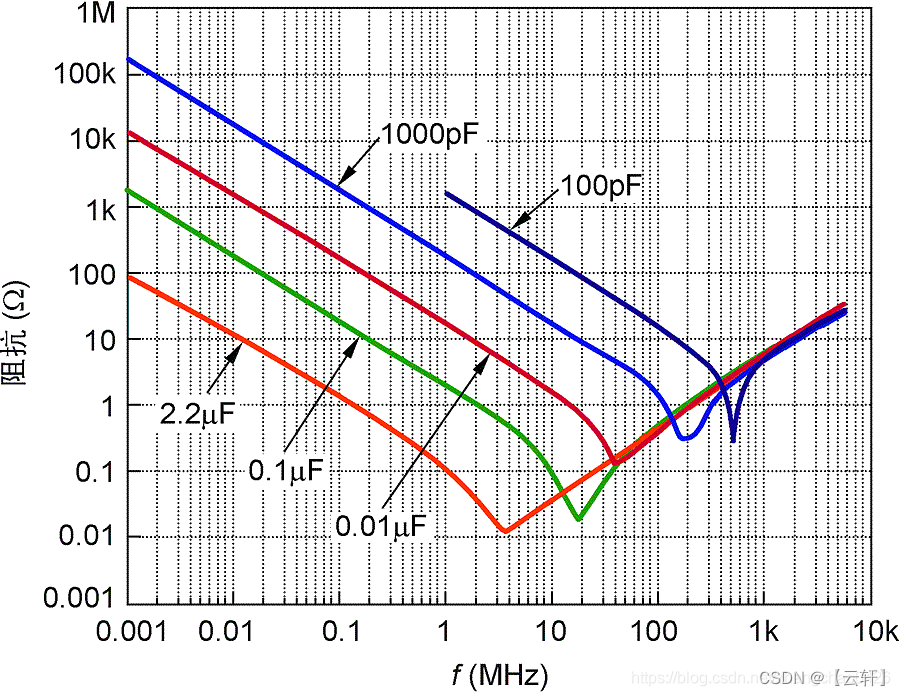

由电容得容抗公式可得,在同样频率下,电容值越大,阻抗越低,电容值越小,阻抗越高。

由电容ESR和频率关系图可知,

5、电路板上退耦电容的布局布线

先看一个很形象的动图,直观体会一下一个电容放置位置不同起到的作用有多大的差异。看不懂这张图的同学在家面壁三天。

这张动图其实传递了如下的信息:

在电源管脚上放置一个104(0.1μF)的电容能够有效抑制电源上的噪声,也就是能够对电源噪声去耦;

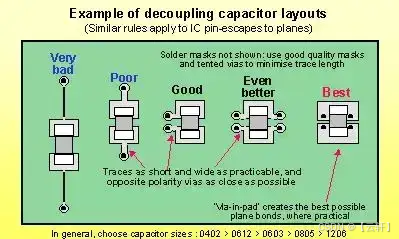

“电源 – 去耦电容 – 地”三点一线的距离越近,则去耦的效果越好;

相同材料的电容,即便电容容量减少为1/10,去耦的效果并不会有什么明显变化,我们对于高频去耦用同样封装的器件,容值为0.01μF、0.1μF、1μF效果相差不大;

同样容值,贴片(SMD)封装的电容比穿孔的电容效果更好,原因就是穿孔电容的管脚等效的电感要大很多,影响了去耦的效果;

电源平面和地平面的使用,一方面可以让三点一线的路径更短,而且两个平面相当于一个大电容,也起到了去耦的作用。

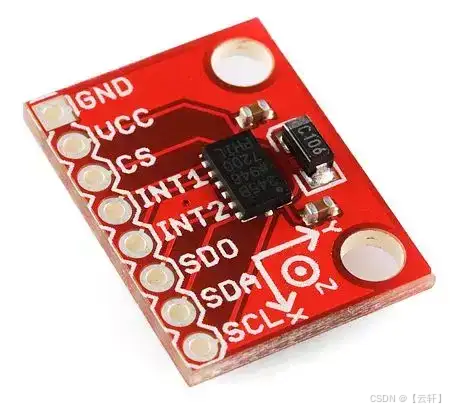

我们再来看一个实际的典型电路 - ADXL345是一颗加速度计传感器芯片,有两个分得比较开的电源管脚(Pin 1和Pin 6),在原理图中使用三个去耦电容来帮助降低传感器电压上的噪声 - 两个0.1μF的陶瓷电容和一个10μF的钽电解共同完成去耦功能。

再看一下最终的PCB板 - 这个板子密度不高,速度也不快,只需要2层板就可以了,没有专门的地平面,在无布线的区域采用了大面积铺地的方式来降低公共地(GND)的阻抗,三颗去耦电容的接地端直接用焊盘跟GND相连,跟电源管脚连接的另一端则尽可能接近电源管脚。

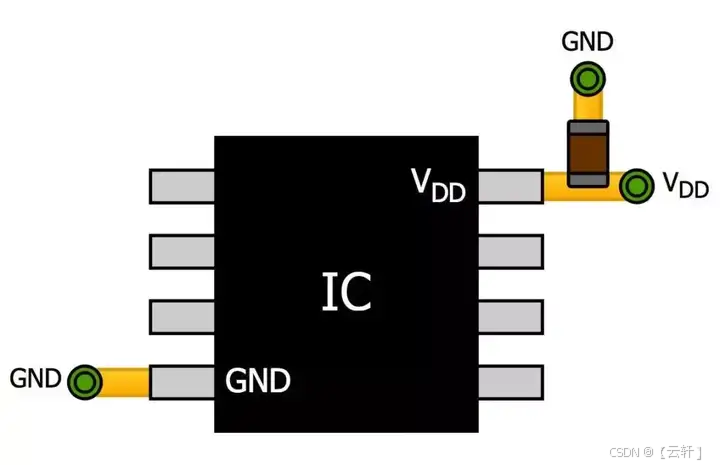

其实放置去耦电容的规则非常简单:最小化电阻,最小化电感。 这是通过将电容尽可能靠近电源引脚并使用尽可能短的走线实现所有连接来实现的。 理想情况下,如果采用4层以上的板子,有专门的地平面、电源平面,可以通过过孔(via)将器件上的地和电源连接到相应的地平面和电源平面:

简单总结一下使用去耦电容的要点:

除非特别说明,一般可为每个电源引脚提供0.1μF陶瓷电容,最好为0805或更小(我比较喜欢0603的,占空间小,性能还好),与10μF的钽电容或陶瓷电容并联;

如果只关心高频噪声,10μF的电容也可以省去,或者用较小的电容替换它;

将高频陶瓷电容尽可能靠近电源引脚放置,并使用短走线和过孔来最大限度地减少寄生电感和电阻。用于低频旁路的较大电容器的位置并不十分关键,但这些电容器也应该尽可能接近IC的电源引脚,容值与封装越大,去偶半径越大,可以对较大的区域的电源进行有效去偶,大封装和大容值的去偶电容可以同时管控多个电源引脚的去偶;

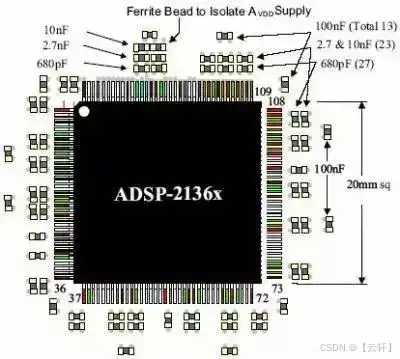

电源的去耦电容均匀分布在四周,靠近相应的电源管脚,容值小的电容最靠近管脚,容值大的距离相对较远

如果需要补偿电源的长期偏差,需要大量存储电荷,需要为每个IC增加一个更大的电容,例如47μF;

如果设计包含非常高的频率或特别敏感的电路,可以使用仿真工具分析旁路网络的AC响应(可能很难找到ESR和ESL的数据参数,特别是考虑到电容的ESR随频率变化也很大 - 尽可能做到最好),还要考虑到多个电容并联以及计入电源平面、地平面等的综合效应。

对于电源和地平面的去耦是通过电源和地平面之间形成电容来对高频噪声进行去耦的。应尽可能减小电源和地平面之间的距离,对于高速电路,一般内层会有完整的电源及地平面,这时去耦电容及IC的电源、地引脚直接过孔via打到电源、地平面即可,不需用导线连接起来。

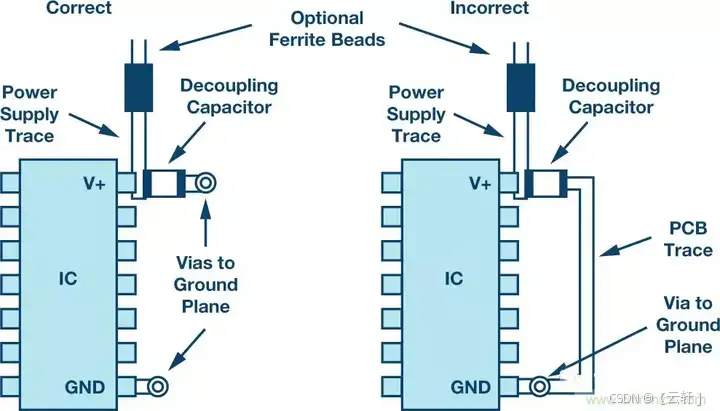

上图左侧,电源引脚和接地连接都比较短(直接通过过孔连接到内部地平面)是最有效的配置;上图右侧,PCB走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

下面的图是去耦电容通过过孔与地进行连通的方法比较,从最左侧的效果最差依次编号,直到最右侧效果最佳,当然具体采用那种方式还要取决于其它一些因素,综合考虑后做一个折衷。

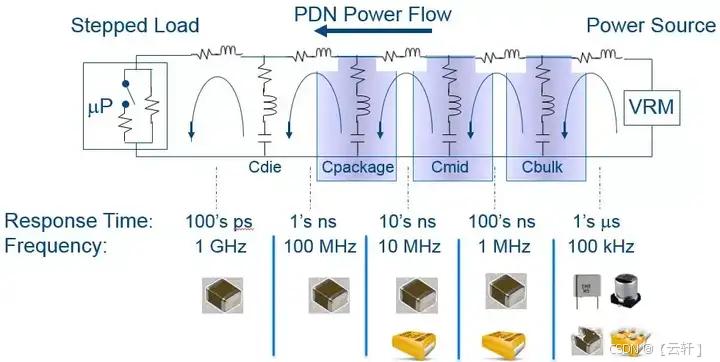

最后再回顾一下上一篇文章中我们的最后一个图,它是一个实际电子产品系统的供电分布网络(PDN - Power Distrubution Network)图,为了强调噪声的起源(最左侧),把电源模块(VRM)放到了最右侧。PCB上的走线、过孔、相关的器件引脚等都会产生寄生电阻、电感等,在图中以R+L的方式等效表达出来。在这个图中可以看出针对IC器件内部(Die)、针对整个IC器件(Package)、针对某一个功能模块中的电路单元都有相应的去耦电容,最左侧(靠近内核)采用频率响应很高的小容值、小封装的陶瓷电容,到右侧则是低频率、容量比较大的电解电容。

芯片电源旁通常放置100nF电容以退耦,防止电源波动影响芯片工作。退耦电容能滤除高频噪声,100nF兼顾性价比和滤波效果。大电容与小电容并联可覆盖更宽频率范围,降低阻抗。

芯片电源旁通常放置100nF电容以退耦,防止电源波动影响芯片工作。退耦电容能滤除高频噪声,100nF兼顾性价比和滤波效果。大电容与小电容并联可覆盖更宽频率范围,降低阻抗。

1420

1420

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?