硬件设计-PCIE转千兆网

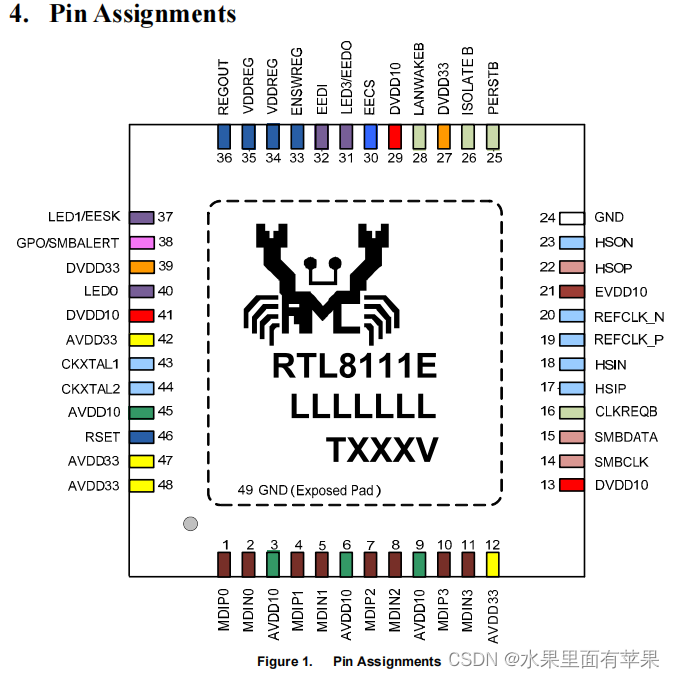

1.引脚说明

以RTL8111E为例

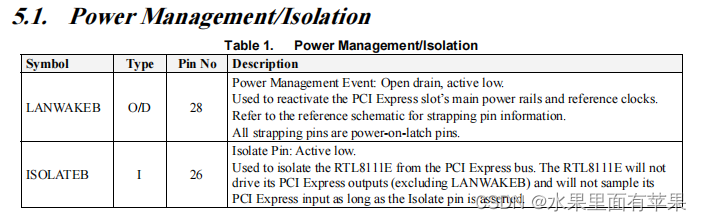

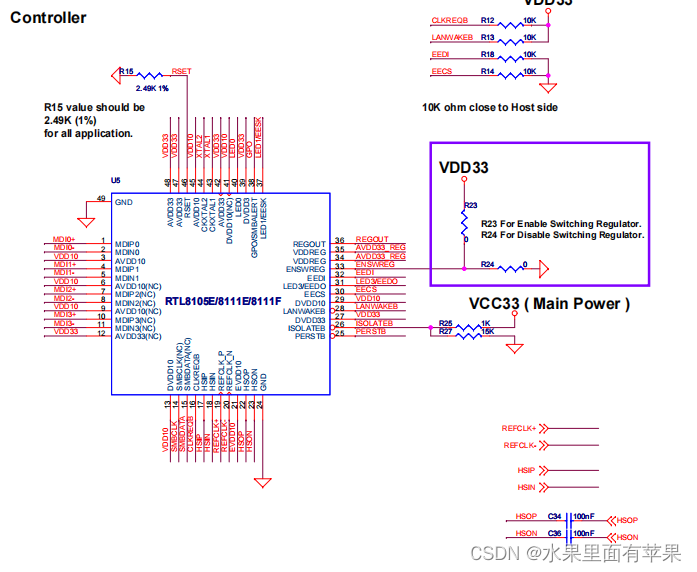

28脚10K上拉3.3V,链接检测

26脚1K15K分压3.3V,pcie输出使能

PCIE总线的引脚

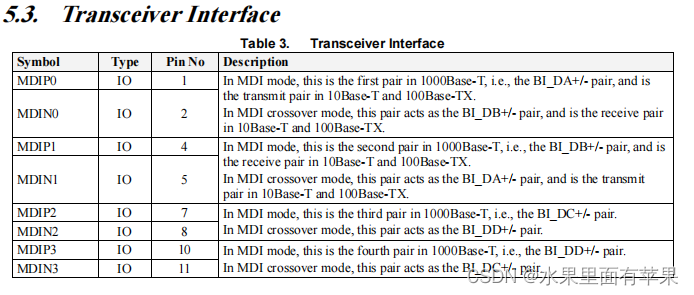

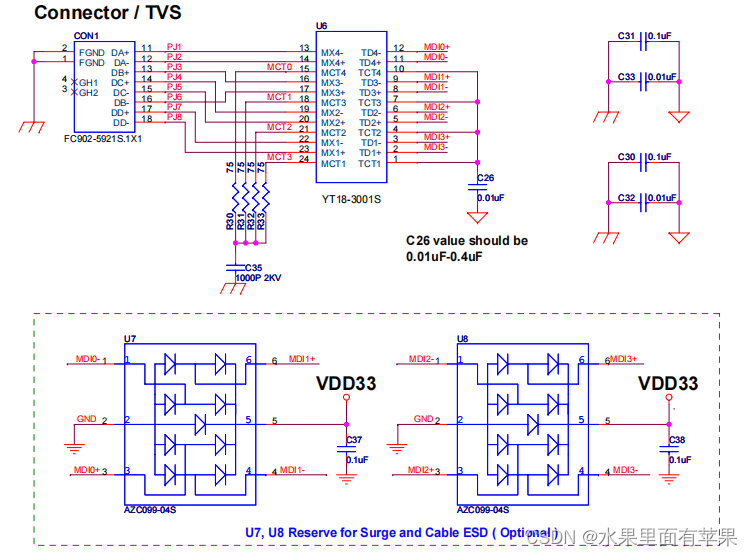

千兆网的MDI引脚,连接网络变压器

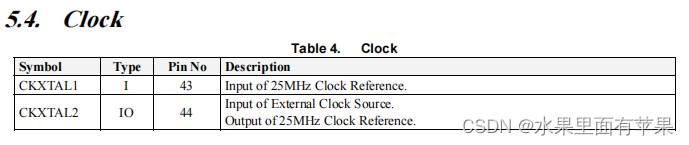

25M晶振引脚

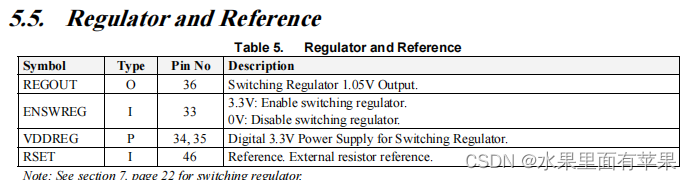

36脚1.05V开关电源输出引脚

33脚,使能开关电源

34/35脚,3.3V供电

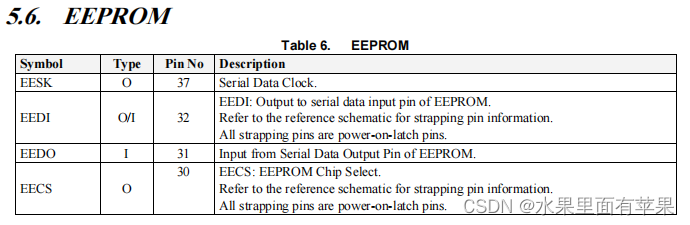

FLASH连接引脚

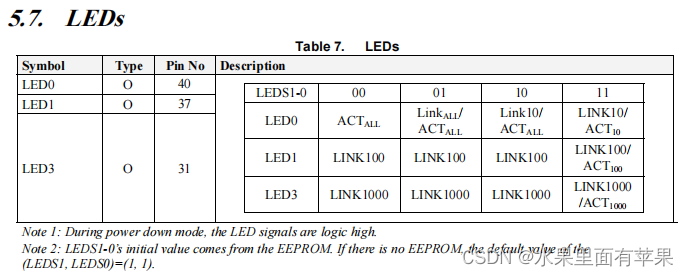

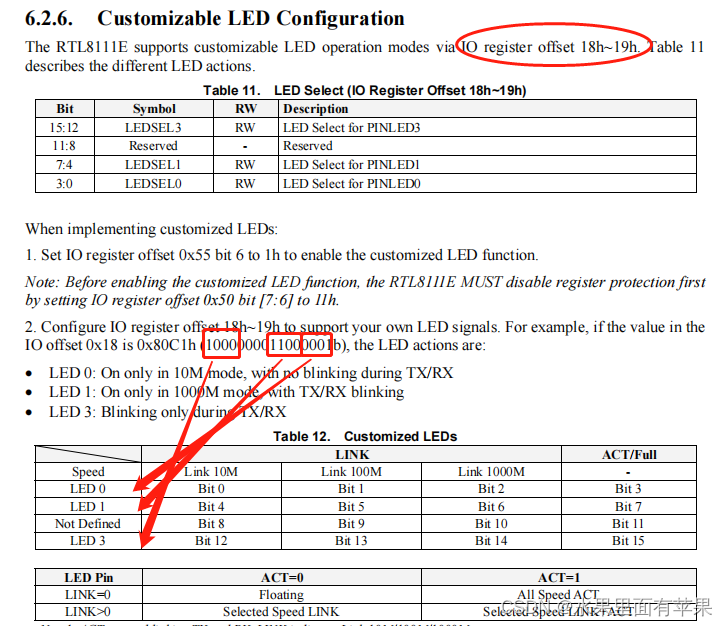

LED指示,Link/ACT指示灯表示线路是否连接或者活动的状态,一般情况下如果线路畅通的话,指示灯长亮;如果有数据传送时,则指示灯闪烁。第31、37脚是复用信号引脚。如果需要同时启用双色指示灯和EEPROM,则芯片的第31脚和第37脚为共享引脚。无论何时建立连接状态,指定的连接指示灯引脚都被驱动为低电平。一旦网络电缆断开连接,连接指示灯引脚就会变高,表示不存在网络连接。

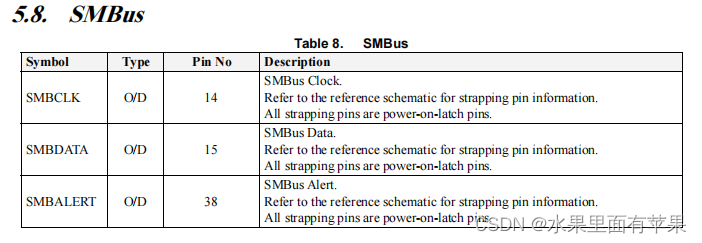

SMBUS引脚

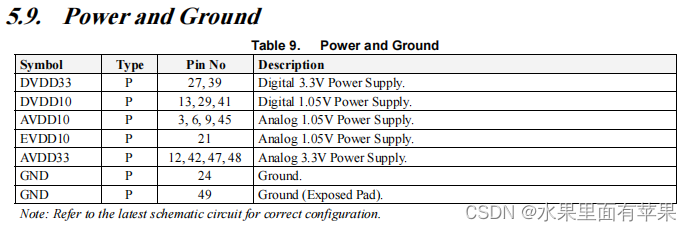

电源引脚

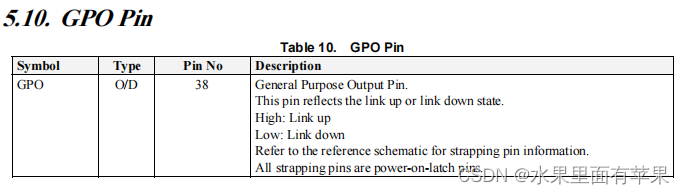

通用输出引脚

2.硬件设计要点

硬件设计要点:

- 注意电源的功率需求以及纹波要求

- PCIE侧01.uF电容靠近金手指放置,差分线等长3MIL,差分线3W设计,过孔尽量不超2个,TX与RX分别走不同的层,要有完整的参考。

走线尽量短。 - 千兆网差分等长100R布线,方式ESD芯片,有参考层,注意模拟地与数字地单点接地。单个差分对应尽可能紧密地布在一起。通常开始阻抗计算时, 选择最小的走线空间 (4–5mil)。然后再调整跟踪宽度, 以达到必要的阻抗。

- 一般情况下, 当将千兆以太网的4个差分对路由到 rj45 连接器时, 至少有一对将并在通过到相反的外部层。在这种情况下, 必须确保电路板另一侧 (通常为第4层) 的路由通过对接地的低阻抗的连续参考平面

- 网络变压器下方挖铜

- 数据走线尽可能短

4433

4433

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?