硬件设计-PCIE转网络设计

PCIE2.0X4转4-port千兆口

WX1820自学整理

- 预留外部NC上拉3.3V

- 预留外部NC上拉3.3V

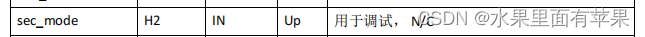

- mng_det信号预留外部NC下拉3,sec_disable信号预留外部NC上拉3.3V,ext_phy信号预留外部NC上拉3.3v。

- 25M晶振输入信号

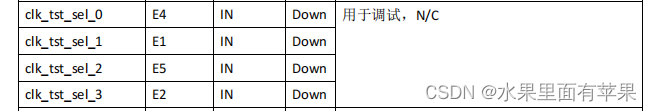

- 预留NC下拉

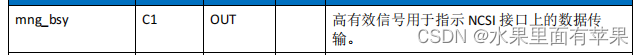

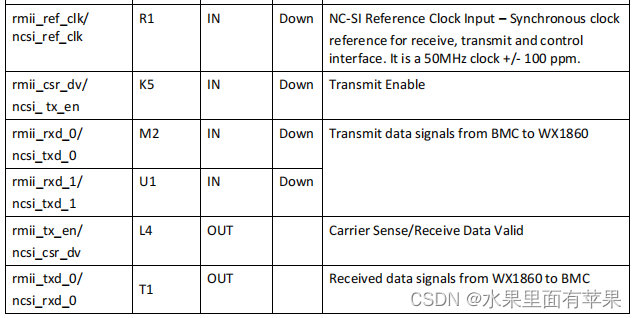

- 高有效信号用于指示 NCSI 接口上的数据传输。

- 号预留外部NC上拉3.3v

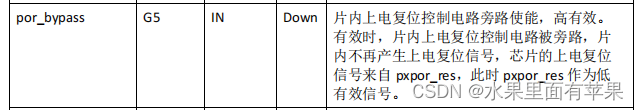

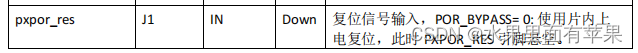

- G5:1K上拉3.3V,J1复位信号输入,低有效。

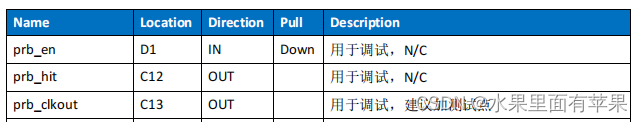

- D1.C12两个引脚NC。C13引脚预留测试点。

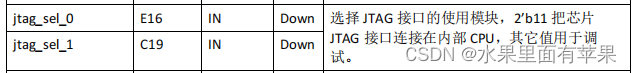

- 预留1KNC上拉3.3V

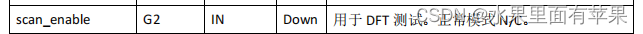

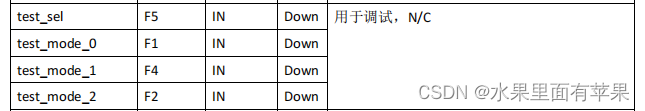

- 预留测试点

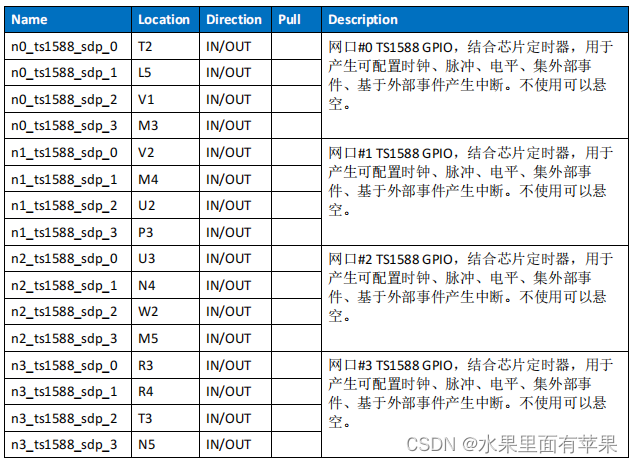

- 引脚悬空即可

- 引脚悬空即可

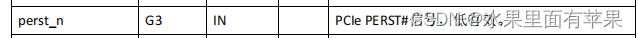

- PCIE复位信号,接到CPLD

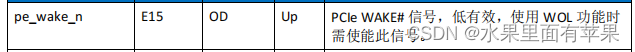

- pcie的wake信号,上拉4.7K到3.3V

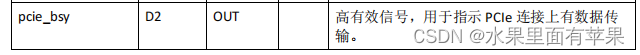

- PCIE有数据传输时高。可接LED灯。

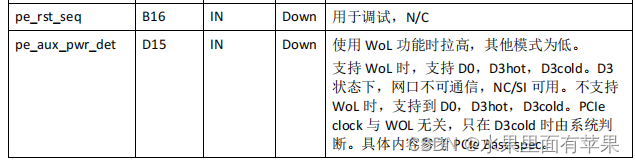

- 引脚预留上拉NC电阻到3.3V

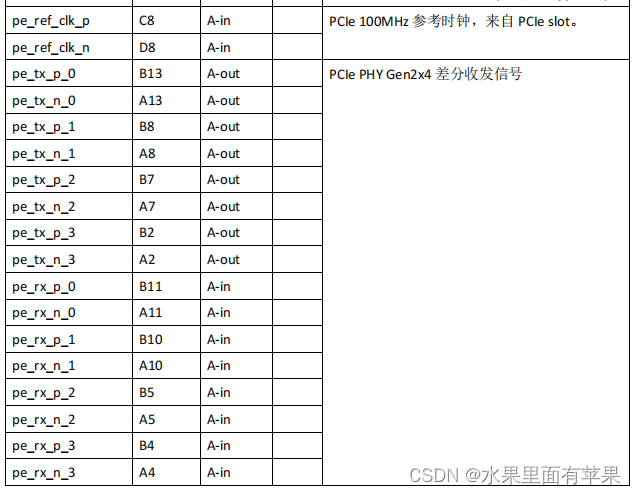

- PCIE总线信号

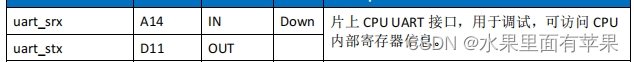

- UART接口

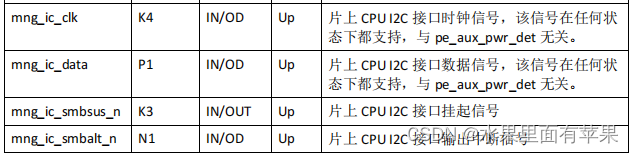

- iIC信号上拉10K到3.3V,K3预留NC上拉3.3V,N1信号上拉10K到3.3V

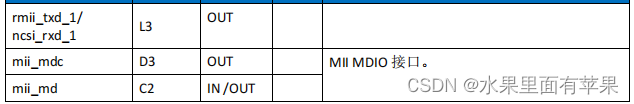

- NCSI信号

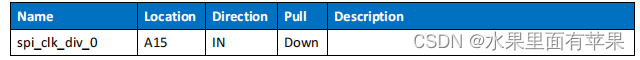

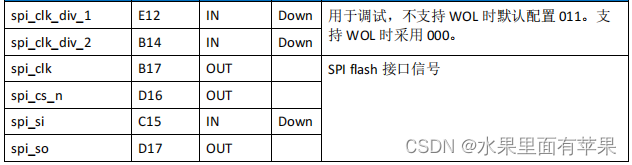

- SPI接口,外接flash芯片。spi_clk_div[2:0]:011

- 预留NC上拉电阻3.3V

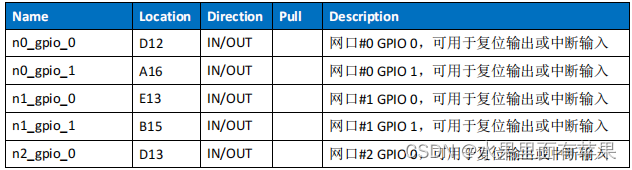

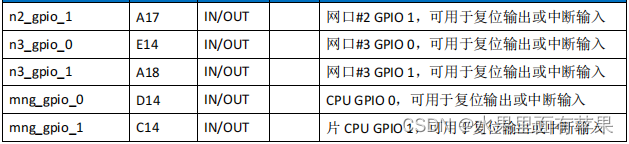

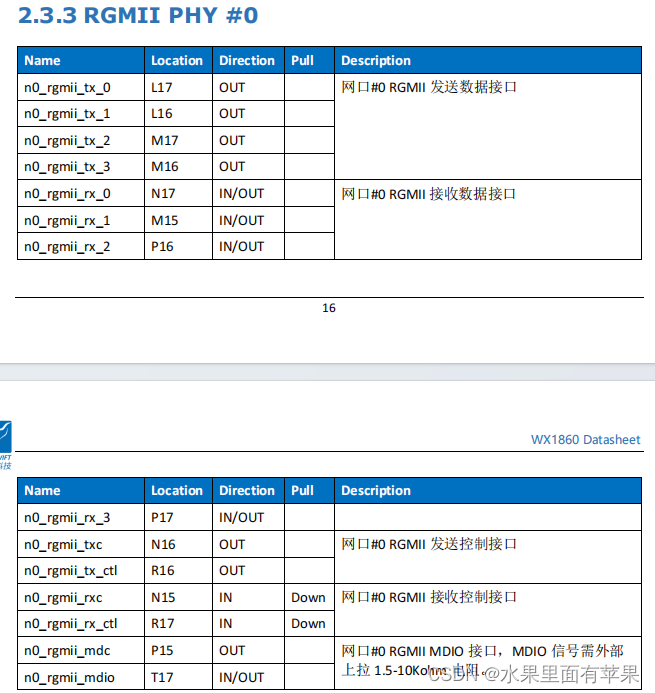

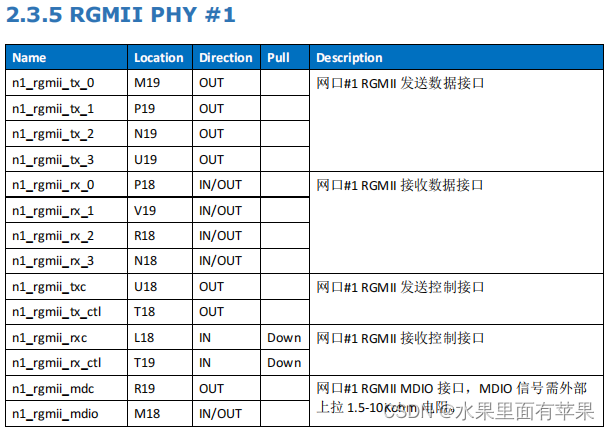

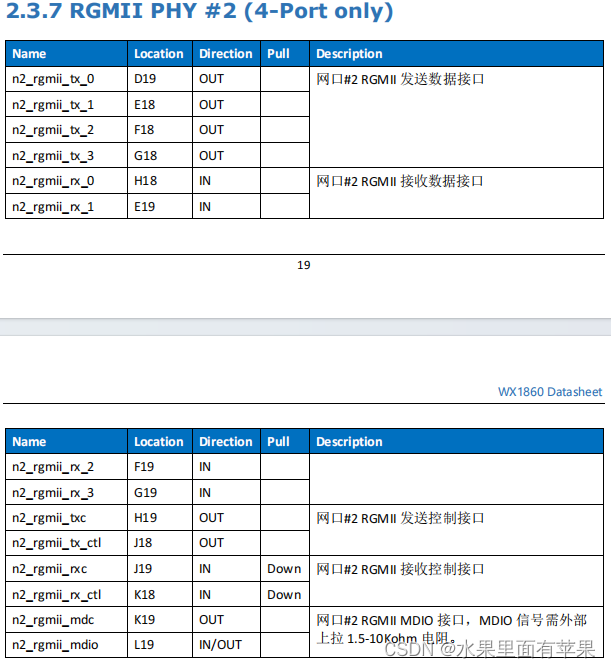

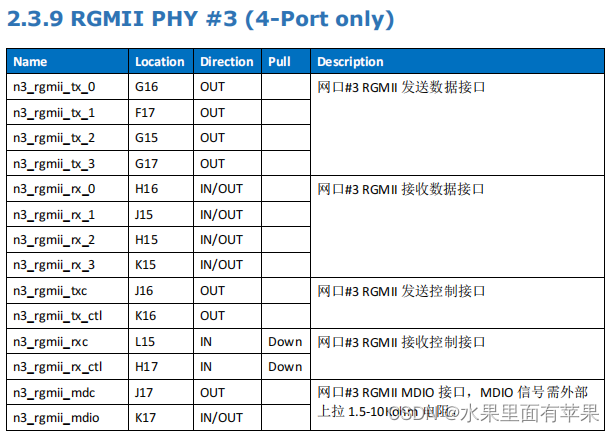

- 4个端口的RGMII接口

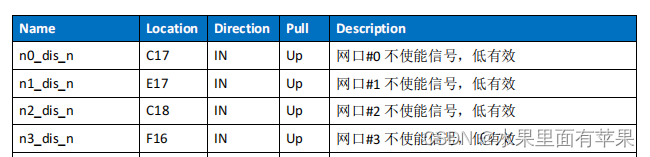

- 网口不使能信号,低有效。

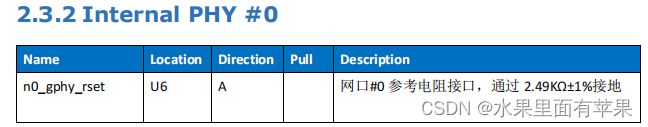

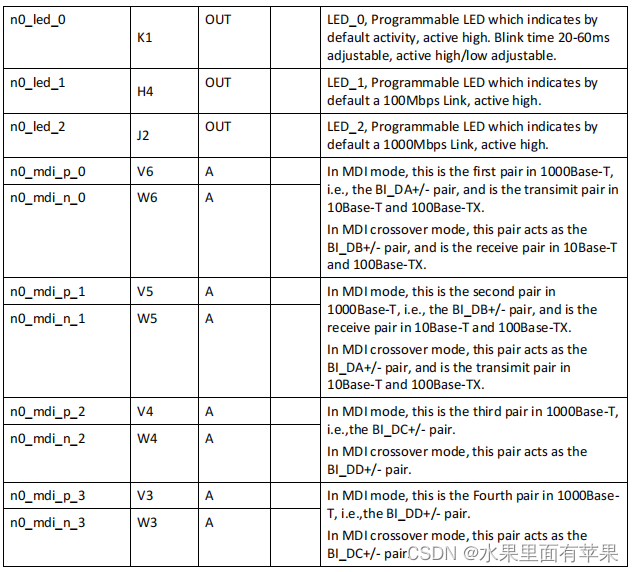

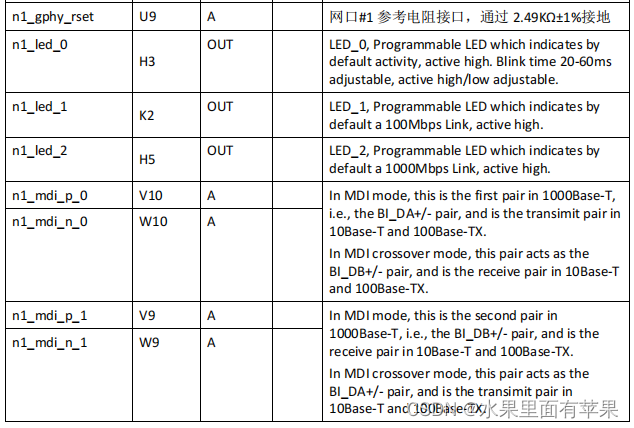

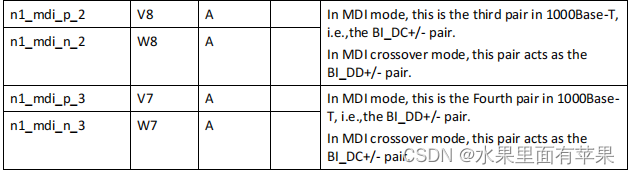

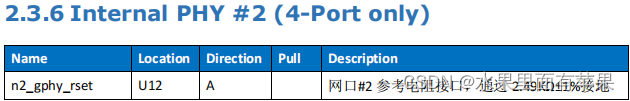

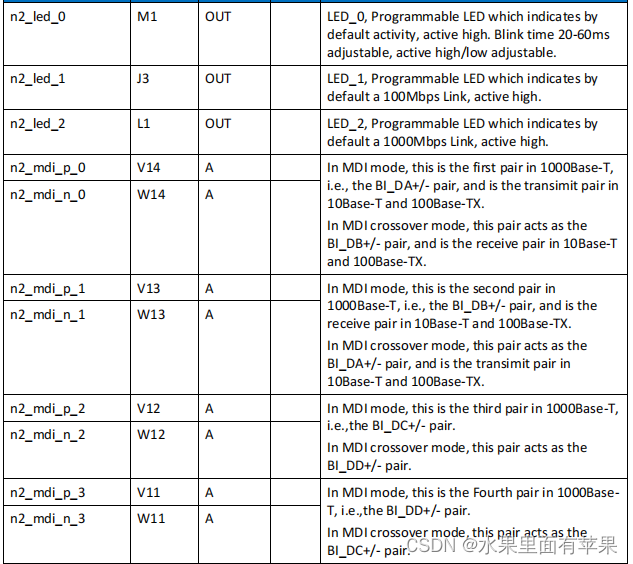

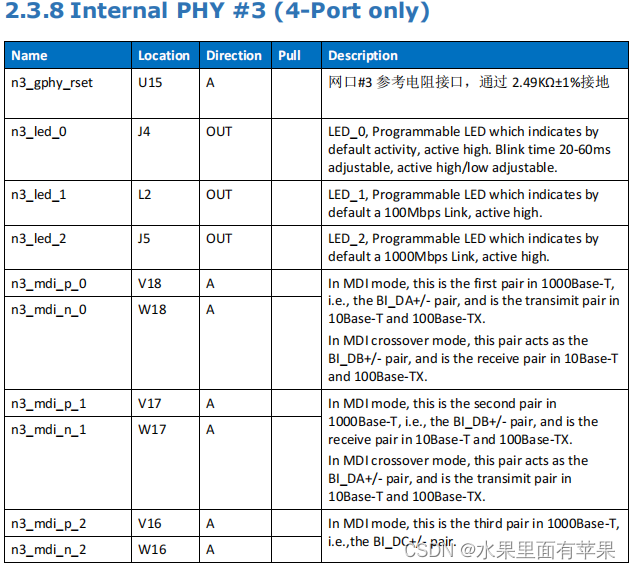

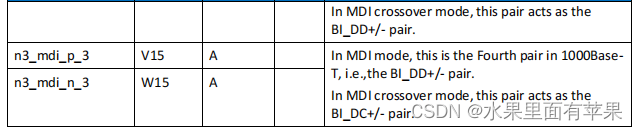

- 四个网口的MDI信号,LED0表示link/act,LED1表示100M,LED2表示1000M。都是高有效。

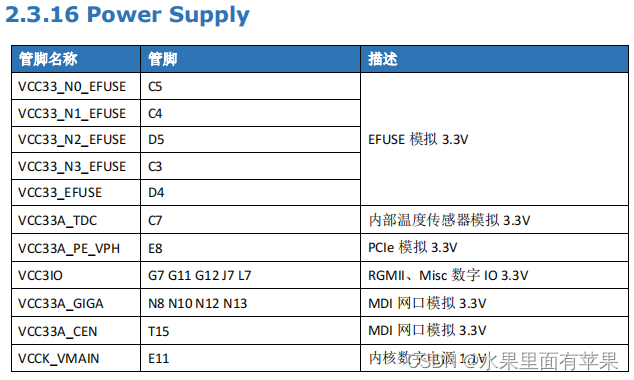

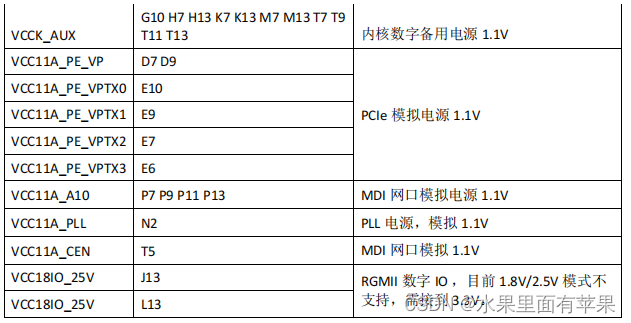

- 电源与地接口

- 上电要求

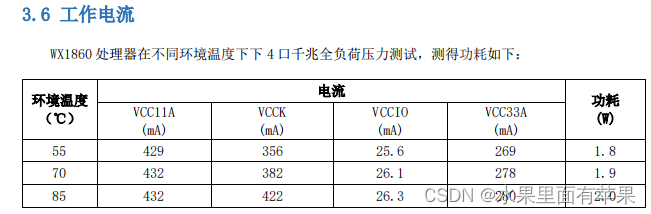

- 功耗

517

517

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?