前言

TD 支持用户使用第三方工具(如 Synopsys VCS、 Mentor Graphics Modelsim 等) 来进行功能验证和时序验证。仿真包括功能仿真和时序仿真,功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证;而时序仿真是在布局布线后进行,它与特定的器件有关,又包含了器件和布线的延时信息,主要验证程序在目标器件中的时序关系。这里主要介绍使用Modelsim进行功能仿真。一、前期准备

生成安路IP核在Modelsim里的库。

1.打开安路TD安装位置,找到sim_release,复制文件内容。

2.打开modelsim安装位置,新建文件夹Anlogic,在Anlogic内新建文件夹src,将第一步复制内容粘贴进去。

3.打开modelsim,点击file-change directory

4.修改路径为modelsim安装路径下新建的Anlogic,点击确定.

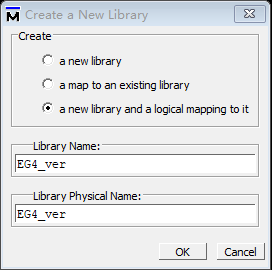

5. 点击file – new – library,新建库.该库为安路的仿真库。该库命名为EG4_ver,点击OK。

6、向新建的EG4_ver内添加安路的ip,选中EG4_ver,点击compile-compile。

Library选择刚刚建立的EG4_ver,文件选择modelsim – Anlogic – src – eg,选中eg内所有的文件,点击Compile,点击Done即完成IP的添加。

二、仿真步骤

1.打开在已经建立的工程wave_produce,点击process – properties,修改simulation里lib位置为modelsim路径下Anlogic – EG4_ver,点击save。

在这里插入图片描述

2. 点击左下角optimize RTL

3.点击tool – simulation – post-RTL simulation,点击Yes。

4.新建测试文件,或导入已有测试文件,点击OK。将测试文件放在wave_produce/simulation/路径下。在这里插入代码片

测试文件代码如下:

// Verilog testbench created by TD v5.0.27252

// 2021-06-30 18:22:52

`timescale 1ns / 1ps

module DDS_tb();

reg clk;

reg rst_n;

wire [11:0] Data;

//Clock process

parameter PERIOD = 10;

always #(PERIOD/2) clk = ~clk;

//glbl Instantiate

glbl glbl();

//Unit Instantiate

DDS uut(

.clk(clk),

.rst_n(rst_n),

.Data(Data));

//Stimulus process

initial begin

//To be inserted

clk = 1;

rst_n = 1;

#1000

rst_n = 0;

#100000

$stop;

end

endmodule

此测试文件只仿真正弦波,其他波形同。

5.打开Modelsim新建工程。

将工程位置放在第一步建立的TD工程wave_produce下的simulation。

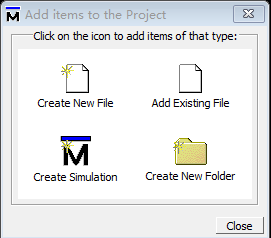

6.点击添加文件。

分别添加文件工程wave_produce下al_ip下的DDS.v文件、sine_wave_sim.v和simulation里的测试文件DDS.tb.v。

由于此仿真只仿真正弦波,而DDS.v文件包括所有波形。此时导入的.v文件如下:

module DDS(

input clk,

input rst_n,

output DA_clk,

output reg [11:0] Data

);

reg [31:0] cnt;

wire [11:0] rom_addr;

always@(posedge clk or posedge rst_n)

if(rst_n)

cnt <= 32'd0;

else

cnt <= cnt +8590;

assign rom_addr = cnt[31:20];

assign DA_clk=clk;

//例化ä¸åŒçš„波形IPæ ¸

wire [11:0]Data_sin;

sine_wave sine_DDS(

.clka(clk), // input wire clka

.addra(rom_addr), // input wire [11 : 0] addra

.doa(Data_sin) // output wire [11 : 0] doa

);//æ£å¼¦

//波形的显示

always@(*)

Data=Data_sin;//æ£å¼¦æ³¢

endmodule

7.编译文件

8.仿真

9.选择测试文件,取消 Enable optmization。

添加库文件,选择modelsim路径下Anlogic – EG4_ver. 点击OK即可仿真。

10.调整波形显示。

选择Data信号,右击—>Radix—>Unsigned进制改为无符号。

选择Data信号,右击—>Format—>Analog(automatic)设置数据以模拟波形显示。

即可得到仿真波形。

总结

以上就是正弦波发生器使用Modelsim与联合仿真的操作步骤,本文仅仅介绍了正弦波发生器的仿真。锯齿波、三角波、方波同理。

2115

2115

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?