文章目录

前言

TangDynasty(TD)软件是安路科技自主开发的FPGA集成开发环境,支持工业界标准的设计输入,包含完整的电路优化流程以及丰富的分析与调试工具,并提供良好的第三方设计验证工具接口,为所有基于安路科技FPGA产品的应用设计提供有力支持。

本文介绍在安路TD软件上实现基于FPGA的DDS信号发生器。

本设计使用大科电子工作室的FA301开发板,核心芯片为安路科技EG4A20BG256

一、初始配置

(软件下载安装见主页)

1、打开TD软件,建立新工程

2、选择使用器件,设置工程的存放位置和名字

这里我们使用的是安路开发的EG4系列芯片EG4A20BG256。

3、新建工程完成

4、新建IP核

选择Primitive IP——Memory——ROM

给IP器件配置参数,导入.mif文件,.mif文件的生成方法见下文(见第五步)

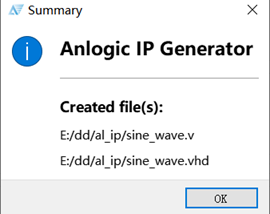

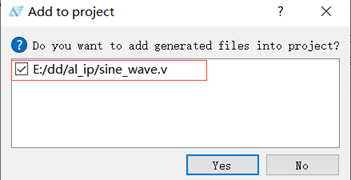

这里选择.v文件,点击Yes,IP核就建立好了

根据上述步骤添加分别正弦波、方波、三角波、锯齿波的IP核,添加完成后如下图

5、生成.mif文件

这里推荐使用mif生成器Mif_Maker2010

下载地址与使用说明

下载完成后打开Mif_Maker2010

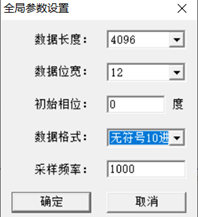

设置全局参数

设置无符号10进制数据,数据位宽12位,长度4096

以生成正弦波的.mif文件为例

保存.mif文件(这里不要选用另存为,会无法保存数据)

选择保存显示的就是另存为,放在刚才建立的工程文件下al_ip文件里

按照以上步骤分别生成正弦波、方波、三角波、锯齿波.mif文件,生成完成后如下图

6、新建.v文件,编写程序

设置程序文件为顶层文件

程序DDS.v代码如下

module DDS(

input clk,

input rst_n,

input [1:0] Mode_Sel,

input [1:0] fword_sel,

output DA_clk,

output reg [11:0] Data

);

reg [31:0] r_fword;

reg [11:0] r_pword;

reg [31:0] cnt;

wire [11:0] rom_addr;

wire[11:0] rom_addr1;

wire[11:0] rom_addr2;

wire[11:0] rom_addr3;

wire[11:0] rom_addr4;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

r_pword <= 0;

end

else begin

r_pword <= 2048; //这里时相位控制,单通道设计可以忽略

end

end

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 32'd0;

else

cnt <= cnt +r_fword;

assign rom_addr = cnt[31:20] + r_pword;

assign rom_addr1 = cnt[31:20] + r_pword;

assign rom_addr2 = cnt[31:20] + r_pword;

assign rom_addr3 = cnt[31:20] + r_pword;

assign rom_addr4 = cnt[31:20] + r_pword;

assign DA_clk=clk;

//例化不同的波形IP核

wire [11:0]Data_sin,Data_sin1,Data_square,Data_triangular,Data_sawtooth_wave;

sine_wave sine_DDS(

.clka(clk), // input wire clka

.addra(rom_addr), // input wire [11 : 0] addra

.doa(Data_sin) // output wire [11 : 0] douta

);//正弦

triangular_wave triangular_DDS(

.clka(clk), // input wire clka

.addra(rom_addr1), // input wire [11 : 0] addra

.doa(Data_triangular) // output wire [11 : 0] douta

);//三角

square_wave square_DDS(

.clka(clk), // input wire clka

.addra(rom_addr2), // input wire [11 : 0] addra

.doa(Data_square) // output wire [11 : 0] douta

);//方波

sawtooth_wave sawtooth_wave_DDS(

.clka(clk), // input wire clka

.addra(rom_addr3), // input wire [11 : 0] addra

.doa(Data_sawtooth_wave) // output wire [11 : 0] douta

);//锯齿

//频率的切换

always@(*)

case(fword_sel)

0:r_fword=8590;//100HZ 00

1:r_fword=85899;//1000HZ 01

2:r_fword=858993;//10KHZ 10

3:r_fword=8589935;//100KHZ 11

endcase

//波形的切换

always@(*)

case(Mode_Sel)

0:Data=Data_sin;//正弦波00

1:Data=Data_square;//方波01

2:Data=Data_triangular;//三角波10

3:Data=Data_sawtooth_wave;//锯齿波11

endcase

endmodule

代码中频率变换参考这篇博文 DDS频率变换 ,本设计时钟位为50MHz。

程序中例化IP核名字与之前新建IP核设置的要保持一致。

7、管脚配置

管脚配置有两种方法,一种是编写添加.adc约束文件,另一种是通过图形界面进行配置,这里用第一种方法。

管脚配置约束文件wave_produce.adc内程序如下

set_pin_assignment { Mode_Sel[0] } { LOCATION = M15; }

set_pin_assignment { Mode_Sel[1] } { LOCATION = N13; }

set_pin_assignment { clk } { LOCATION = E1; }

set_pin_assignment { fword_sel[0] } { LOCATION = E16; }

set_pin_assignment { fword_sel[1] } { LOCATION = M16; }

set_pin_assignment { rst_n } { LOCATION = virtualIO; }

set_pin_assignment { DA_clk } { LOCATION = M9; }

set_pin_assignment { Data[0] } { LOCATION = B7; }

set_pin_assignment { Data[10] } { LOCATION = L9; }

set_pin_assignment { Data[11] } { LOCATION = L10; }

set_pin_assignment { Data[1] } { LOCATION = A6; }

set_pin_assignment { Data[2] } { LOCATION = B6; }

set_pin_assignment { Data[3] } { LOCATION = A5; }

set_pin_assignment { Data[4] } { LOCATION = N2; }

set_pin_assignment { Data[5] } { LOCATION = P6; }

set_pin_assignment { Data[6] } { LOCATION = M8; }

set_pin_assignment { Data[7] } { LOCATION = N8; }

set_pin_assignment { Data[8] } { LOCATION = P8; }

set_pin_assignment { Data[9] } { LOCATION = K9; }第二种方法 通过图形界面进行配置方法如下:

只需要需要改界面中的Location即可

二、运行和烧录上板实现

(与modelsim的联合仿真见主页)

1、运行程序

运行完成

2、连接硬件

开发板FA301

DAC和转接线

开发板扩展口原理图如下,可对照管脚配置进行连线

因为使用DAC是8位,我们程序数据设置为12位,所以舍弃低四位,即D0—D3不必连线。

连接图如下

3、烧录程序

下载程序模式可以选择JTAG和Program Flash,JTAG模式断电不保存程序,Program Flash模式断电后仍保存程序

添加bit流程序

烧录成功

4、示波器看结果

设计实现通过按键切换锯齿波、方波、三角波、正弦波四种100kHz的波形,按键控制波形频率的变换,下面展示部分波形图

频率变换

1KHz

10KHz

100Hz

至此,本设计全部结束。如有问题,欢迎提出。

2345

2345

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?