一、时钟资源简介

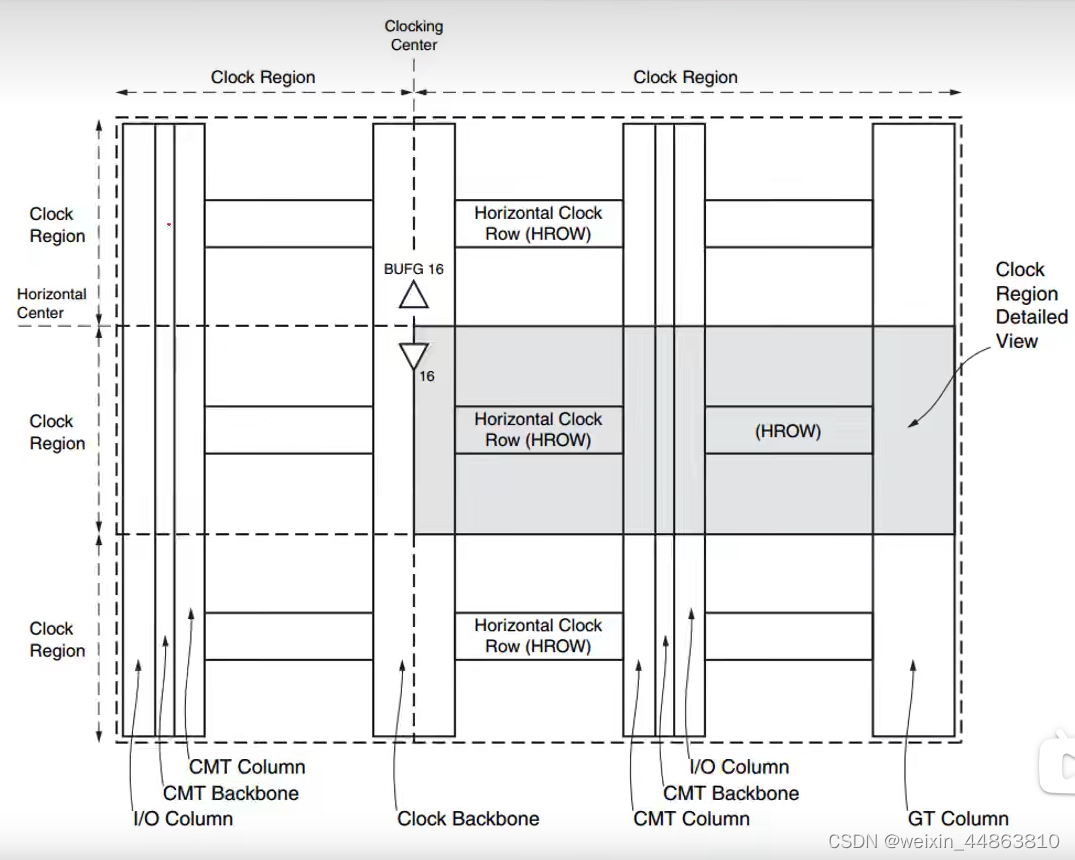

7系FPGA使用了专用的全局(Global)时钟和区域(Regional)时钟资源来管理和设计不同的时钟需求.

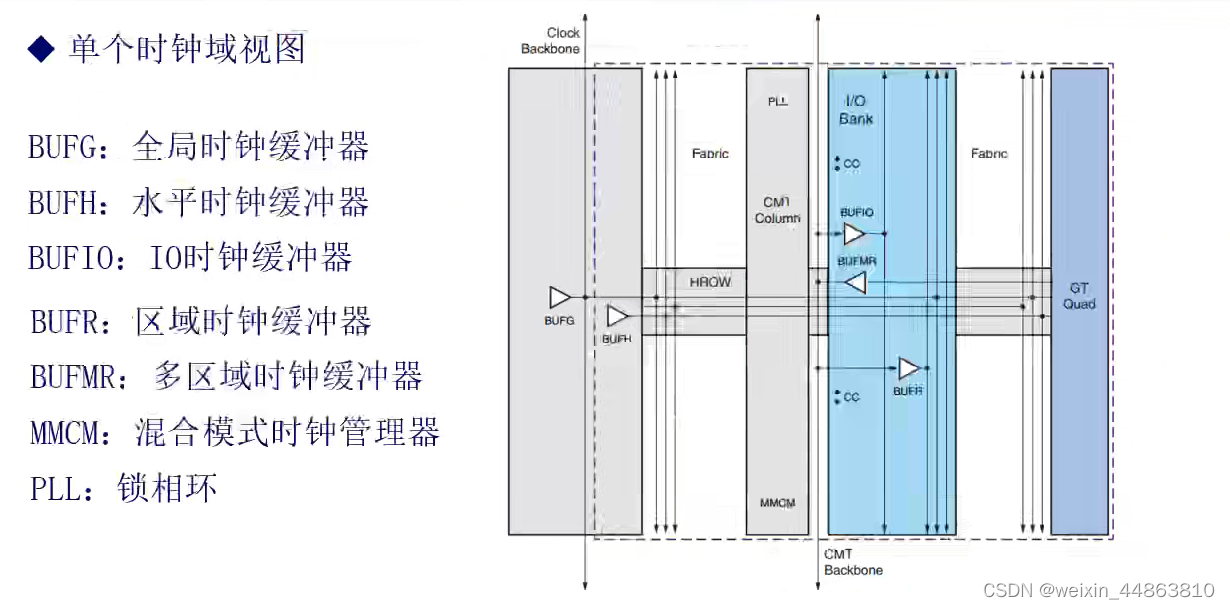

Clock Management Tiles(CMT)提供了时钟合成(Clock Frequency synthesis),倾斜校正(deskew),过滤抖动(jitter flitering)功能。

Clock Backbone 是全局时钟线贯穿整个FPGA并使能BUFG(全局时钟缓存器),且在控制区域模块充当时钟时与BUFH共享Horizontal Clock Row时钟通道。

Clock Region是区域时钟,来给区域内的单元提供时钟驱动,并且使能BUFR(区域时钟缓冲器)。

Horizontal Clock Row(HROW) 是区域时钟内的水平时钟通道。

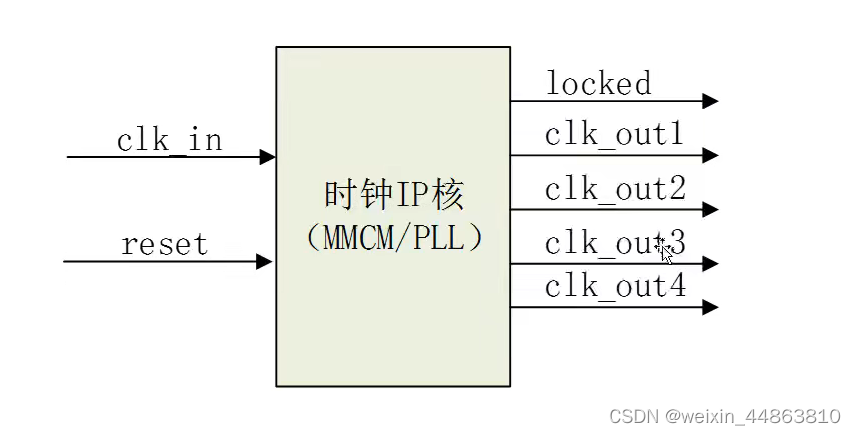

Clock Management Tiles(CMT)时钟管理资源,包含PLL和MMCM,可以对时钟信号实现分频倍频等等。可以让外接时钟通过PLL或MMCM来稳定时钟。MMCM可以动态调整而PLL则不行

GT column 是高速接收器

(这四个是Xilinx 7系列FPGA全系所支持的GT,GT的意思是Gigabyte Transceiver,G比特收发器。通常称呼为Serdes、高速收发器,GT,或者用具体型号(例如GTX)来称呼。

7系列中,按支持的最高线速率排序,GTP是最低的,GTZ是最高的。GTP被用于A7系列,GTZ被用于少数V7系列。从K7到V7,最常见的是GTX和GTH。GTH的最高线速率比GTX稍微高一点点。

GTX和GTH的文档都是UG476。从这里就能看出来,这两个GT的基本结构大同小异。所以掌握一个,另一个基本也就熟悉了。

UG476文档链接:http://link.zhihu.com/?target=https%3A//www.xilinx.com/support/documenta...)

BUFIO只能控制区域内的IO资源,而BUFR不仅可以控制IO资源还可以控制除IO资源以外的逻辑单元。

BUFMR可以使能多个区域通道的BUFIO和BUFR。

CC可以外接晶振引入时钟信号。

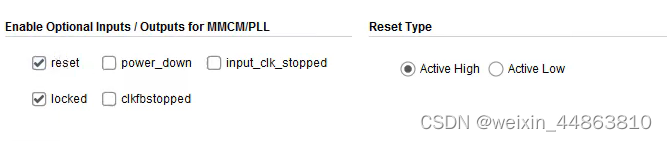

当locked拉高时,认为时钟输出稳定,输出有效,可以认为是时钟IP的有效位

二、Clock IP核配置

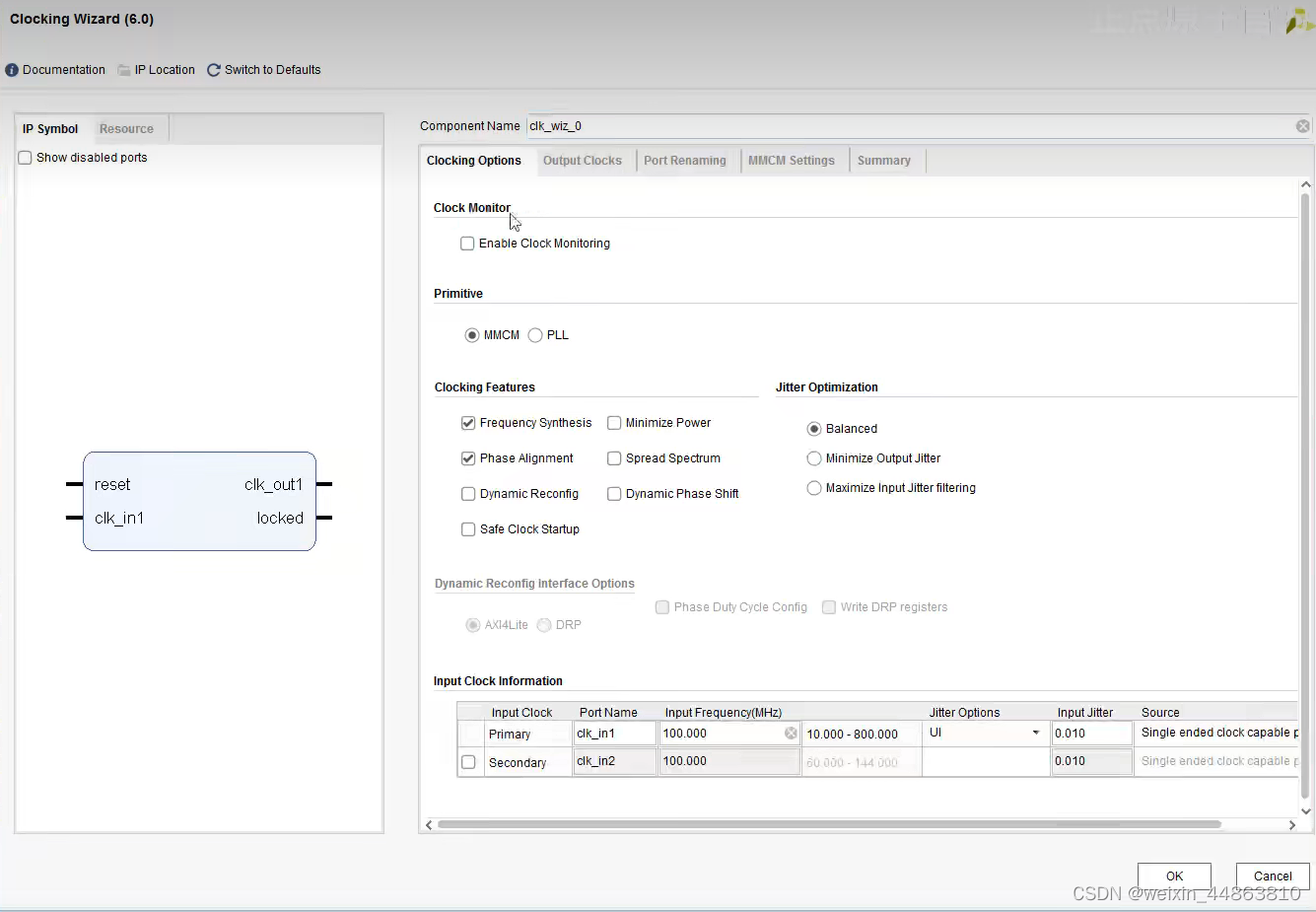

1、clock monitor

检测时钟的异常状态,以及相位频率的改变。

2、primitive

选择是CMT中的MMCM还是PLL。

3、frequency synthesis

选择时钟频率是否可改变,可以输出不同的频率的时钟。

4、phase alignment

知道输入时钟的相位关系。

5、dynamic reconfig

输出时钟频率的动态调整,可以改变正在输出时钟的频率,可以不用重新配置IP核。

6、safe clock startup

通过一个建立时钟时间来保证输出时钟的稳定性,然后将locked拉高,可以是时钟更加稳定,但是在高速时钟中可能会影响性能。

7、Dynamic phase shift

t输出时钟相位的动态调整

8、jitter optimization

抖动优化的选择,有追求性能和资源的平衡模式、最小输出抖动、最大输入抖动滤波模式。对资源的占用不同,选择合适设计的优化。

最下方是更改输入时钟的信息 频率之类的。

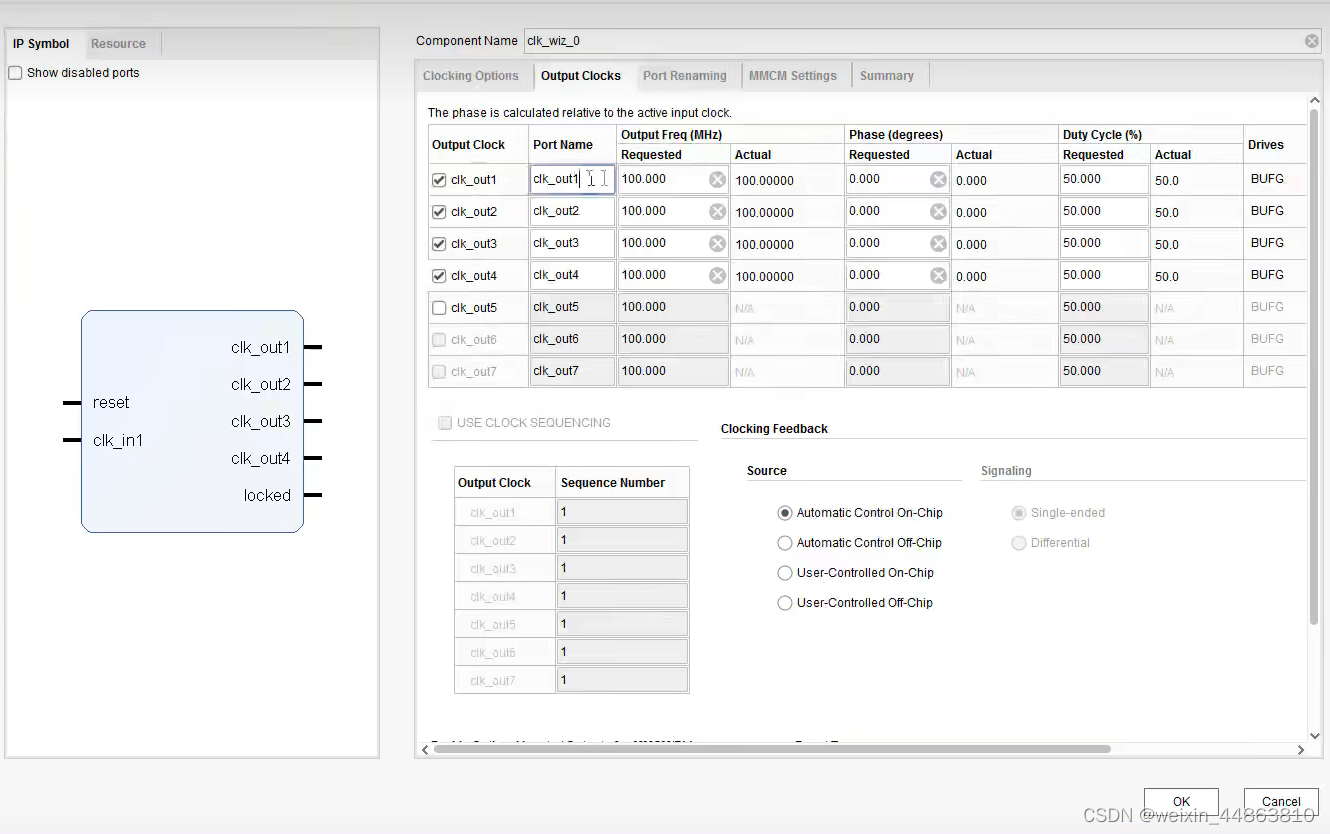

输出时钟的配置,可以配置多个输出时钟,以及配置这些时钟的频率、相位、占空比.

一些可选的配置信号。

reset type:是指复位信号高地电平敏感

4783

4783

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?