反相器的Verilog实现及仿真验证

inv.v

// inv design

module inv(A,Y);

input A;

output Y;

assign Y=~A;

endmodule

inv_tb.v

`timescale 1ns/100ps

// ---- testbench of inv ----

module inv_tb;

reg aa;

wire yy;

inv inv(

.A(aa),

.Y(yy)

);

//输出vcd格式的波形文件,使VCS软件能够查看

initial

begin

$dumpfile("inv_tb.vcd"); //波形文件名

$dumpvars(0,inv);

end

initial begin

aa<=0;

#10 aa<=1;

#10 aa<=0;

#10 aa<=1;

#10 aa<=0;

#10 $stop;

end

endmodule

VCS+DVE

运行VCS生成验证波形时:

vcs inv_tb.v inv.v -R -timescale=1ns/10ps +v2k +define+RTL_SAIF

通用如下:

vcs *.v -R -timescale=1ns/10ps +v2k +define+RTL_SAIF

报错如下:

error: gnu/stubs-32.h: No such file or directory

发现为64位机器缺少编译32位文件的包,添加以下包后解决

sudo yum install -y glibc-static-2.17-325.el7_9.i686

sudo yum install -y glibc-devel-2.17-325.el7_9.i686

再次输入命令vcs inv_tb.v inv.v -R -timescale=1ns/10ps +v2k +define+RTL_SAIF,成功编译、仿真,输入run进行仿真(ucli% run)

再用vde查看波形,输入命令:($等同于Ctrl + Z)

vde& # 加上&可以把软件挂后台,也可以Control+Z实现

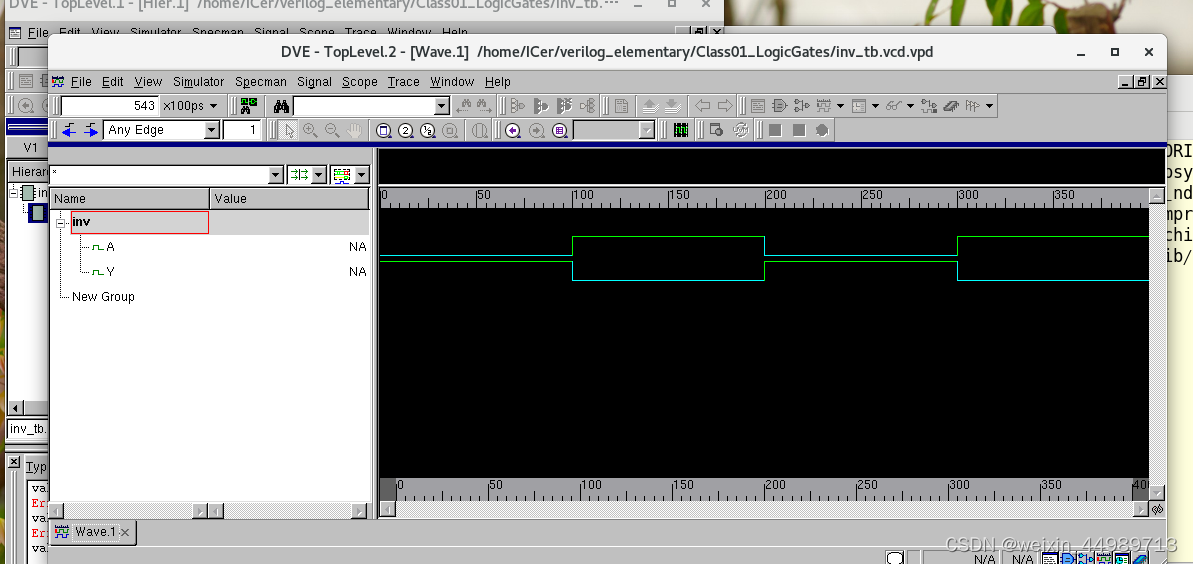

在打开的vde软件中File->Open Database找到刚刚生成的*.vcd文件,再用找到查看的器件->右键->Add To Waves -> New Wave View,即可看到以下的波形

VCS+Verdi

待补充

3340

3340

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?