GT Transceiver的配置-QPLL的工作原理

每个QUAD都包含一个QPLL,QPLL可以被同一个Quad内的transceiver共享,但是不能被其他Quad内的transceiver共享。

当以高于CPLL操作范围的线速率操作通道时,需要使用 QPLL。

GTXE2_COMMON 原语封装了 GTX QPLL,并且必须在使用 GTX QPLL时实例化。

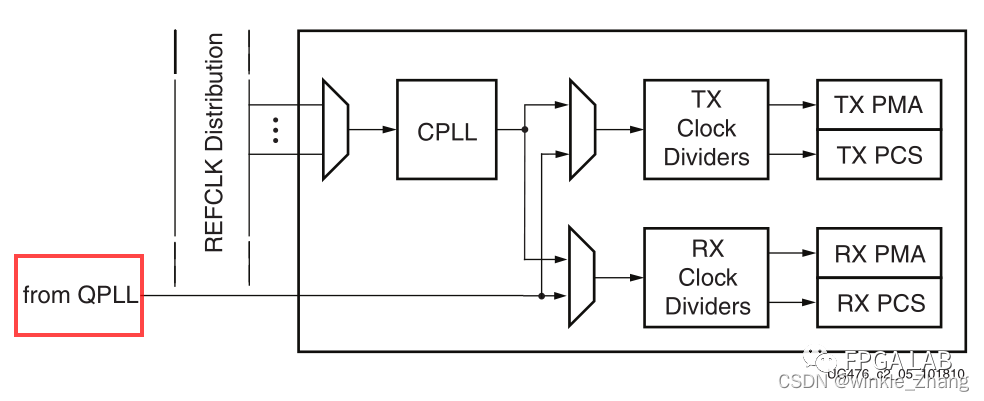

QPLL输出为同一Quad内的每个transceiver的TX和RX时钟分频器块提供信号,该块控制PMA和PCS块使用的串行和并行时钟的生成。

QPLL

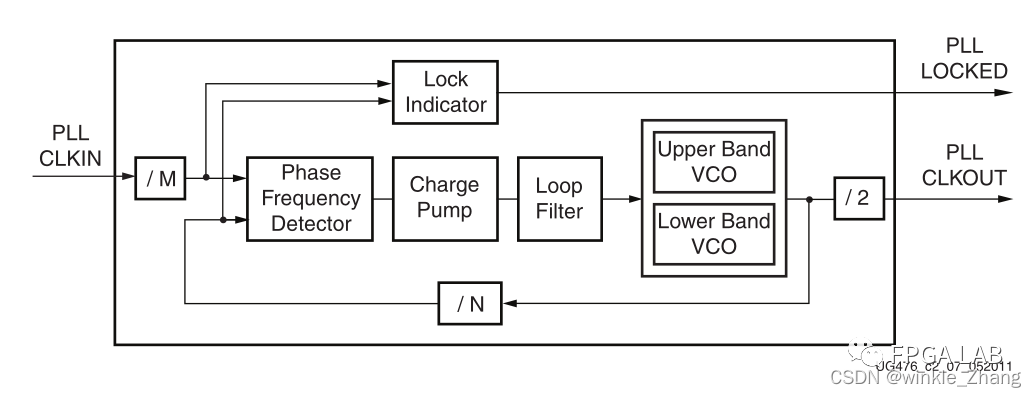

下图为QPLL架构的概念视图:

QPLL架构概念视图

关于,其架构概念框图的描述,和CPLL几乎一致:

输入的时钟在进入相位频率检测器之前可以被除以一个系数M。反馈分频器N决定了VCO的乘法比率。QPLL的输出频率是VCO频率的一半。锁定指示块比较参考时钟和VCO反馈时钟的频率,以确定是否已经实现了频率锁定。

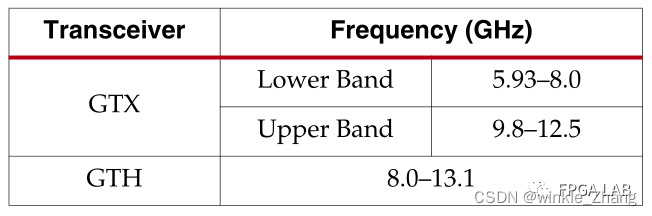

QPLL VCO在两个不同的频段内工作。下表描述了这些Band的标称工作范围。

当选择低频段VCO时,高频段VCO会自动断电,反之亦然。7系列FPGA Transceiver向导根据应用要求选择适当的频段和QPLL设置。

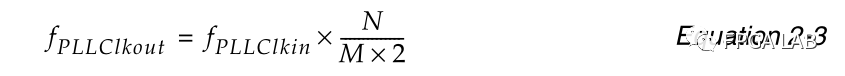

下面两个公式分别决定了QPLL的输出频率GHz以及transceiver线速率:

为什么乘以2,是因为QPLL输出的上升沿以及下降沿都用来产生要求的线速率。

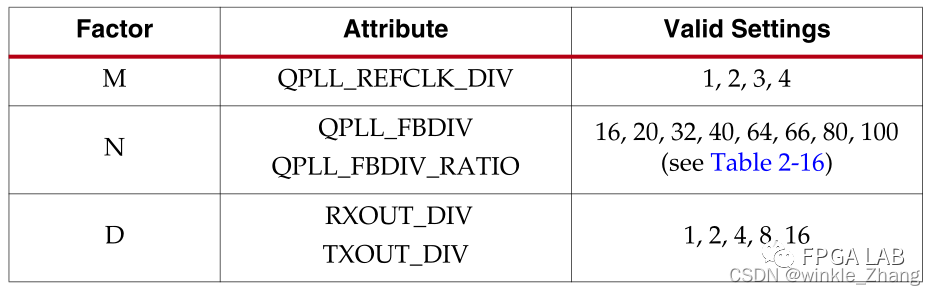

其中,N,M以及D表示QPLL分频器的属性,如下表:

QPLL的分频属性

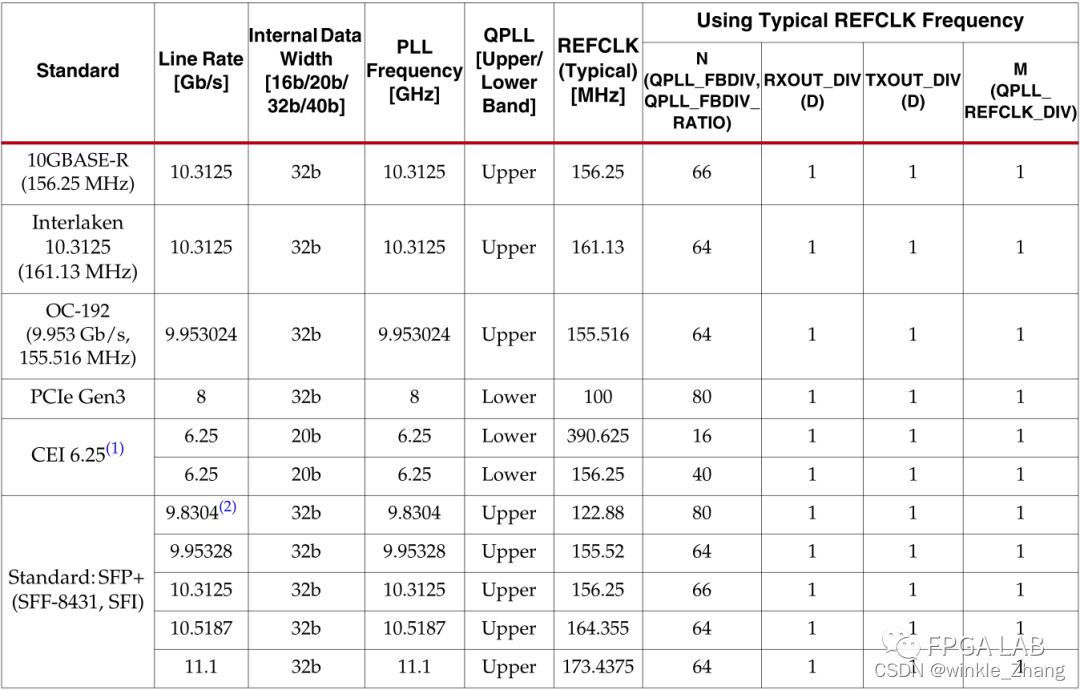

下面是几个通用协议的QPLL分频器属性设置值,可以自行验证:

8969

8969

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?