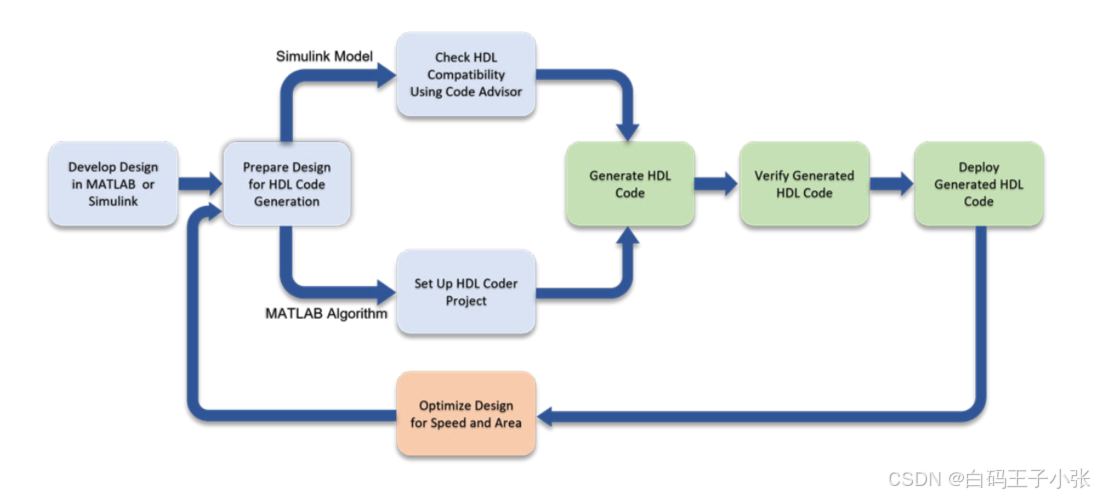

Simulink HDL Coder开发基本流程

您可以使用HDL Coder从Simulink模型或MATLAB算法生成可合成的VHDL, Verilog和SystemVerilog代码。可以使用生成的HDL代码进行FPGA编程、ASIC原型设计和生产设计。使用HDL Workflow Advisor,您可以将生成的HDL代码部署到Xilinx、Intel和Microchip板上。您可以针对速度和面积优化您的设计,突出显示关键路径,并在综合成之前生成资源使用预估报告。

一、Matlab 或者Simulink设计开发

您可以在MATLAB和Simulink中开发HDL代码生成的设计。您可以使用HDL Coder从您的Simulink模型或MATLAB算法生成代码。编写与HDL代码生成兼容的语法和函数的MATLAB算法。使用HDL兼容的Simulink块创建您的设计与Simulink。

二、建立HDL Coder工程

要从MATLAB算法生成HDL代码,请为MATLAB设计创建并设置HDL Coder项目。将MATLAB文件添加到要为其生成HDL代码的HDL Coder项目中。

三、使用HDL Code Advisor检查HDL兼容性

您可以使用HDL Code Advisor检查您的Simulink模型的HDL兼容性。HDL Code Advisor工具验证和更新您的Simulink模型或子系统与HDL代码生成的兼容性。Model Checker工具检查模型配置设置、端口和子系统设置、块设置、对本机浮点数的支持以及对行业标准规则的遵从性。

参考文章:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1334

1334

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?