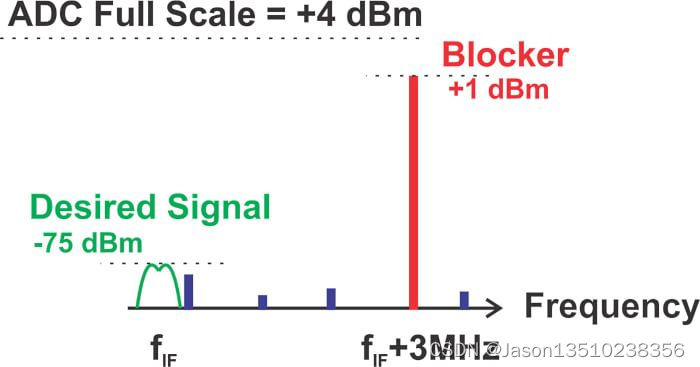

有多种不同的规格可用于表征电路线性度。SFDR 指标是一种常用的规范。该指标定义为所需信号幅度与感兴趣带宽内杂散的比率(图 1)。

图 1. 显示 SFDR 指标的图表。

对于 ADC,SFDR 展示了 ADC 如何在存在大信号的情况下同时处理小信号。作为一个例子,考虑一个接收器应用程序。假设 ADC 输入由 +1 dBm 阻塞信号和 -75 dBm 所需信号组成。在这种情况下,由于ADC 非线性,大阻塞器可能会在 ADC 输出处产生不需要的杂散。这些不需要的杂散由图 2 中的紫色组件显示。

图 2. 该图以紫色显示不需要的杂散。

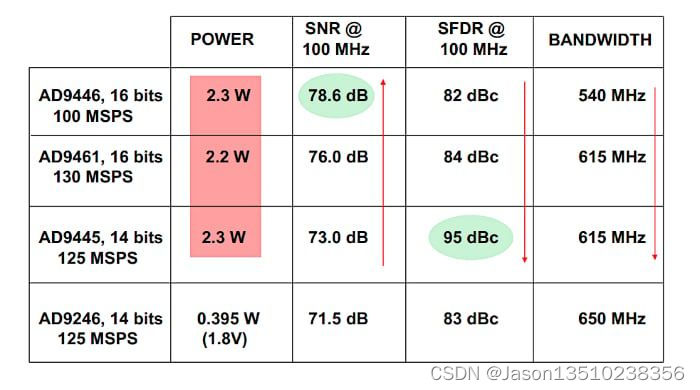

如果杂散足够接近所需信号并且足够大,则可能会将 SNR 降低到不可接受的水平。当今通信系统的严格要求可能需要 95 dB 范围内的高 SFDR 值。然而,普通 ADC 无法提供这种水平的线性度。下面的表 1 比较了 Analog Devices 的四种高性能 ADC 的一些关键参数,应该可以帮助您了解高性能 ADC 的 SFDR 范围。

表 1. 四种高性能 ADC 的关键参数。使用的数据由Analog Devices提供

此外,该表还强调了 SNR 和 SFDR 指标之间的权衡。对于该表中的前三个 ADC,它们使用相同的 IC 技术并具有相同的功耗,因此 SFDR 和 SNR 之间存在反比关系。我们将在本文稍后讨论这种权衡的起源。在此之前,我们先回答一个重要问题:在高速 ADC 中提高 SFDR 的主要限制是什么?

ADC 中的静态和动态线性

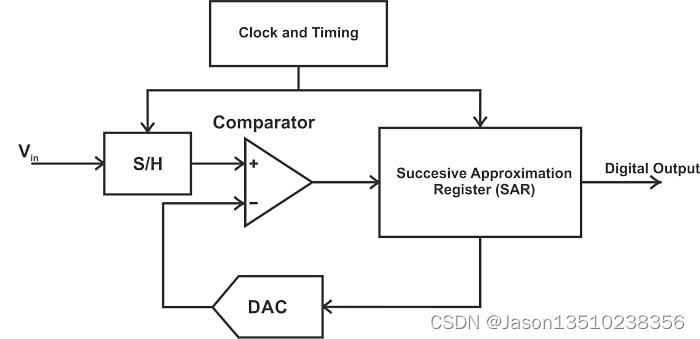

ADC 是基于多种不同电路架构设计的复杂系统,例如闪存、SAR、Delta-Sigma (ΔΣ)和流水线结构。根据架构和特定电路实现,不同的电路元件可能是非线性的主要来源。尽管有多种设计,但我们仍然可以认识到在高速 ADC 中增加 SFDR 的两个主要限制,即 S/H 电路和 ADC 的编码器部分。为了更好地理解这一点,请考虑图 3 中所示的 SAR ADC 框图。

图 3. SAR ADC 框图。

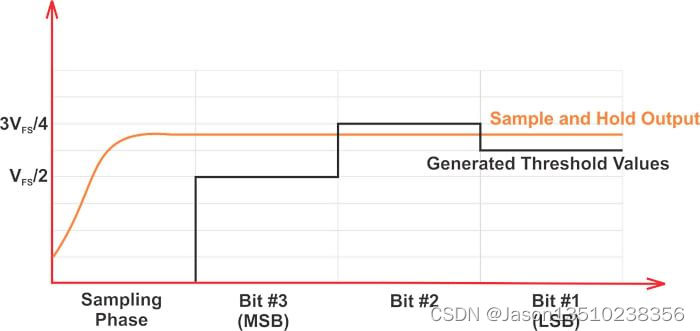

SAR数字化算法的步是采样阶段,在此期间S/H获取输入值。该样本将在整个转换阶段保留。在转换阶段,所采集的样本会连续与适当的阈值电平进行比较,以找到输入的数字等效值。为了确定输出的每一位,需要一个时钟周期。假设采样阶段也需要 1 个时钟周期,则 N 位 SAR ADC 需要 N + 1 个时钟周期。图 4 显示了 3 位 SAR ADC 的 S/H 输出和阈值波形。

图 4. 3 位 SAR ADC 的 S/H 输出和阈值波形。

这里重要的一点是,对于给定的转换阶段,无论输入频率是多少,S/H 之后的电路组件都可以理想地使用直流信号。因此,SAR ADC 的比较器或内部DAC(数模转换器)内的任何非线性 都不会随输入频率而变化。我们可以说 ADC 编码器部分的非线性影响了系统的静态(或直流)非线性。静态非线性的特征是ADC 传递函数中的DNL(微分非线性)和INL(积分非线性)误差。

S/H 非线性怎么样?与有效处理直流信号的编码器部分不同,S/H“看到”交流信号。我们将在下一节中讨论 S/H 非线性的很大一部分如何随输入频率而变化。因此,S/H 决定了 ADC 的动态(或交流)线性度。

3043

3043

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?