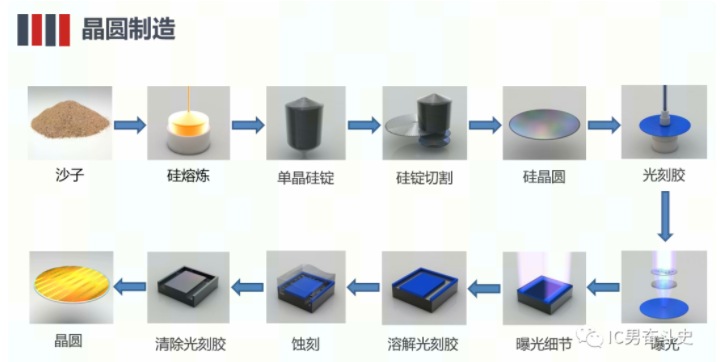

晶圆制造

高大上的芯片最初的原材料其实是沙子,这也是科学技术神奇的地方。沙子的主要成分是二氧化硅(SiO2),而脱氧后的沙子最多包含25%的硅元素,硅是地壳内第二丰富的元素,这也是半导体制造产业的基础。

沙子经过熔炼和多步净化与提纯就可以得到用于半导体制造的高纯度多晶硅,学名电子级硅,平均每一百万个硅原子中最多只有一个杂质原子。24K金大家都知道吧,黄金纯度高达99.998%,但是还是没有这个电子级硅的纯度高。

把高纯度多晶硅放在单晶炉内拉制,就可以得到接近圆柱形的单晶硅锭,重量大约100千克,硅纯度高达99.9999%以上。再将单晶硅锭横向切割成圆形的单个硅片,就得到了单晶硅片,这也就是我们常说的用来制造芯片的晶圆(Wafer)。

单晶硅在电学性质和力学性质等方面的表现都要比多晶硅更好一些,所以半导体制造都是以单晶硅为基本材料。

举个生活中的例子,可以帮大家理解多晶硅与单晶硅。冰糖大家应该都见过,小时候经常吃的像方形小冰块一样的冰糖,其实就是单晶冰糖。相应的也有多晶冰糖,形状通常不规则,用来做中药或者熬汤用,有润肺止咳的功效。

同一种物质晶体排列结构不同,其性能和用处也会不尽相同,甚至差异明显。

半导体制造企业,例如英特尔、台积电和中芯国际等工厂通常不生产晶圆,只是晶圆的搬运工,都是从Wafer供应商那里直接购买。

晶圆制造就是要把设计好的电路(专业术语叫掩膜,英文名为Mask)在晶圆上实现出来。

首先我们需要把光刻胶(Photo Resist)均匀铺在晶圆表面,在这个过程中需要保持晶圆旋转,这样可以让光刻胶铺的非常薄、非常平。然后光刻胶层透过掩模(Mask)被曝光在紫外线(UV)之下,变得可溶。

掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上,就会形成电路的每一层图案。一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。

接下来是溶解光刻胶,曝光在紫外线下的光刻胶被化学试剂溶解掉,清除后留下的图案和掩模上的一致。然后是蚀刻,使用化学物质溶解掉暴露出来的晶圆部分,剩下的光刻胶保护着不应该蚀刻的部分。蚀刻完成后,光刻胶的使命宣告完成,全部清除后就可以看到设计好的电路图案。这一系列过程我们称之为光刻。

光刻的过程其实类似于我们生活中用傻瓜照相机拍照的过程。铺上光刻胶的晶圆就是相机的胶片,我们要拍摄的实物就是掩膜,拍照的过程就是半导体曝光的过程,冲洗胶片的过程就类似于后面的蚀刻以及溶解光刻胶。

最后的结果也有些类似,光刻将设计好的电路在晶圆上实现了出来,得到了芯片,如同拍照将实物的样子在胶片上实现了出来,得到了照片。

光刻是芯片制造过程中最主要的工艺之一。通过光刻,我们就实现了把设计好的电路铺在晶圆上,重复进行就可以在晶圆上实现多个相同的电路,每一个电路都是一个单独的芯片,英文称为die。实际的芯片制造流程比这个复杂得多,通常需要经过成百上千道工序。所以说半导体是制造业的皇冠。

了解芯片制造流程对于从事半导体生产制造相关的岗位比较重要,尤其是FAB厂如台积电、中芯国际等工厂的技术人员,或者芯片研发团队的量产相关岗位如产品工程师、测试工程师等,都属于必备的基础知识。

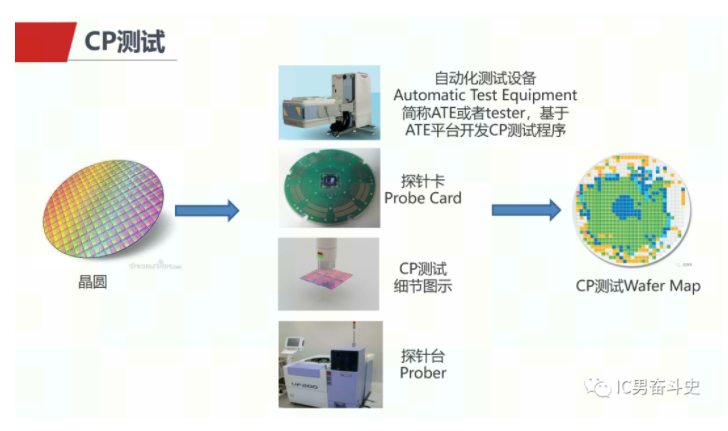

CP测试

CP是Chip Probing的缩写,CP测试属于晶圆级测试,是通过探针卡(Probe Card)和探针台(Prober)使自动化测试设备(ATE,Automatic Test Equipment)到晶圆上的单颗芯片(die)之间建立电气连接。CP测试的目的是确保每颗die都能满足芯片的设计规格(Specification),筛除其中有问题的die,然后再去做芯片封装。这样就可以减少芯片封装的成本,同时保证芯片的质量。

CP测试需要的硬件设备包括探针卡、探针台、ATE测试机台以及测试机与探针卡之间的接口(Mechanical Interface)。

测试工程师需要基于ATE测试平台开发CP测试程序,内容通常包括电气连接性测试、功能测试和参数测试等。CP测试程序会根据测试结果Pass或者Fail进行分Bin并生成Inkless Map,标记出测试Fail die的wafer map图。

CP测试结果通常以良率的形式进行统计,良率就是指pass die占测试die总数的百分比。相应的,良率损失是指fail die占测试die总数的百分比。CP测试也称为中测,是半导体后道封装测试的第一站,也是芯片制造完成后第一道验证芯片设计规格的测试。

从节省芯片生产成本的角度考虑,我们应该把尽可能多的测试项目都放到CP测试中,提高CP测试覆盖率,尽可能早地把有问题的芯片筛出去。但是相应地,CP测试硬件的成本(主要是探针卡和测试机台)也会上升,归根到底其实就是一个需要折中考虑的问题。

如果芯片市场需求量相对较大,测试硬件成本与销售利润来比微不足道,那就应该尽量提高CP测试覆盖率。反之,就需要考虑节省硬件成本。

了解CP测试对于从事半导体封装测试相关的岗位比较重要,尤其是封测厂如日月光、安靠、长电等CP测试相关的技术人员,或者芯片研发团队的量产相关岗位如产品工程师、测试工程师等,都属于必备的基础知识。

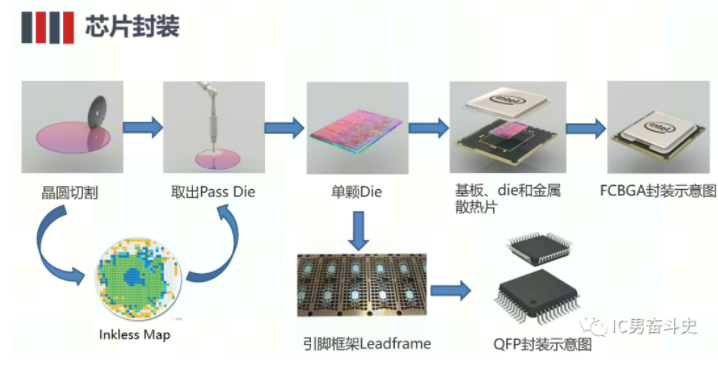

芯片封装

芯片封装的流程也很复杂,通常也需要经历几十甚至上百道工序,这里我主要给大家介绍下其中的一些关键环节。

封装的第一道核心工序是晶圆切割,切割之前通常会按要求对晶圆背部进行打磨(backgrind),使其达到封装需要的厚度。

然后再把晶圆按照die的大小进行切割,切割过程中会用纯水一边清洗一边降温,切割完成后晶圆上的每一颗die就会独立出来。

最后再根据CP测试输出的Inkless Map把晶圆上CP测试pass的die取出来去做封装。

对于不同的封装形式,接下来的流程都不尽相同。这里我们以FCBGA和QFP为例,给大家做简单叙述。

对于FCBGA封装,接下来我们会把基板、die和金属散热片堆叠在一起,就形成了通常我们看到的FCBGA芯片的样子。基板相当于一个底座,为die提供电气与机械界面。金属散热片主要负责die的散热,同时也和基板一起对内部的die起保护作用。

对于传统的QFP封装,接下来我们会把die放到引脚框架(leadframe)里边,leadframe通常是矩形结构,可以同时放置多个die。

然后再对每一个die进行打线(wire bonding),将die内部的pad引出到leadframe的引脚上,使内部的die到外部的引脚建立电气连接。接下来再给leadframe中每一个放die的位置灌入塑封材料,使die密封在内部。

最后再把leadframe按照每一个die位置切开,并把引脚压弯,这样QFP封装的芯片就成型了。

芯片封装是沟通芯片内部世界与外部电路的桥梁,同时还可以起到安放、固定、密封、保护芯片和增强电热性能的作用,是半导体制造业的核心技术。芯片封装就好比给芯片穿上外套,不同形式的封装代表不同样式的外套,使用环境各不相同,价格也各不相同。

而且随着摩尔定律逐渐接近极限,未来半导体集成度提高的方向很可能会往封装方面发展,2.5D/3D封装技术也是目前半导体行业最前沿最热门的研究领域之一。

了解芯片封装流程对于从事芯片封装相关的岗位来说是很有必要的,尤其是封测厂技术人员,或者芯片研发团队的封装相关岗位如产品工程师、封装设计工程师、封装NPI工程师等,都属于必备技能。

FT测试

FT是Final Test的缩写,通常是芯片出货前的最后一道测试。FT测试属于芯片级测试,是通过测试板(Loadboard)和测试插座(Socket)使自动化测试设备(ATE)到封装后的芯片之间建立电气连接。FT测试的目的是筛选出满足设计规格的产品卖给客户。

FT测试需要的硬件设备包括测试板、测试插座、ATE测试机台、Handler以及Change Kit。其中Handler也称为自动化分类机,是用来实现FT测试自动化的设备,Change Kit属于Handler的配套治具。

测试工程师需要基于ATE测试平台开发FT测试程序,内容通常包括电气连接性测试、功能测试和参数测试等。程序会根据测试结果Pass或者Fail进行物理分Bin,也就是说把pass和fail芯片物理上分到不同的容器中。

这里我们也会把不同类型的Fail芯片分到不同的物理容器中,方便对特定类型的fail芯片进行分析或者重测。

FT测试结果也是以良率的形式进行统计,FT良率就是指pass芯片占测试芯片总数的百分比。FT测试是保证芯片质量的最后一道关卡,也是芯片测试阶段最重要的环节。

理想的FT测试程序是100%覆盖率,也就是说所有的测试项目全部放在FT测试阶段。但是这样做的成本是非常高的。

首先,FT测试Fail损失的是封装后的芯片,包含了封装的成本。其次,较高的测试覆盖率需要更多的ATE测试资源,也就意味着FT测试并行度会降低,这样会增加测试成本。两个site并行测试比一个site单独测试肯定要划算。所以,需要将FT测试与CP测试综合考虑才能找到相对优化的测试方案。

例如,有一些对封装不敏感的测试项,我们就放在CP测,FT不测;有一些跟封装关系特别密切的测试项,我们就可以放在FT测,CP不测。总之,芯片测试(CP和FT)是一个整体,需要综合考量,找到较好的测试方案。

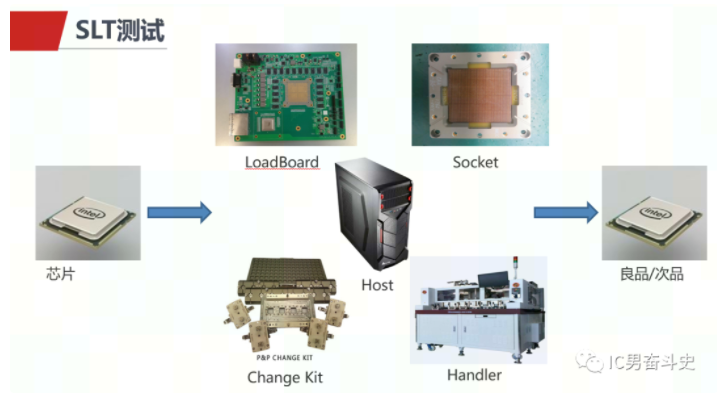

SLT测试

SLT是System Level Test的缩写,SLT测试属于板级或系统级测试,也是通过测试板和测试插座使测试主机到封装后的芯片之间建立电气连接。SLT测试的目的是提高产品板生产良率,减少产品板生产成本。

通常,半导体公司如果直接出售芯片一般不需要做SLT测试,FT测试完成后就可以直接出货给客户。但是有很多半导体企业都是出售搭载芯片的产品板给客户,或者像Intel处理器这样功能相对固定的芯片,需要在FT测试之后再加一道SLT测试。

SLT测试需要的硬件设备包括测试板、测试插座、Handler、Change Kit以及测试主机与连接线等。

SLT测试属于定制化测试,软件部分灵活度比较高,不需要基于自动化测试平台开发,完全由测试工程师自主开发。

SLT测试内容通常包括芯片功能测试、高速接口测试以及DDR内存相关的测试等。与FT测试相同,程序会根据测试结果Pass或者Fail对芯片进行物理分Bin。

SLT测试结果也是以良率的形式进行统计,SLT良率就是指pass芯片占测试芯片总数的百分比。

从目前半导体发展的趋势看,在5G、物联网和人工智能的大力发展与推动下,专用型芯片已经逐渐成为未来的主流形式。相应的,SLT测试在芯片测试领域的受重视程度也越来越高。在不久的将来,SLT测试很可能将会成为芯片测试中最重要的环节。

了解FT测试和SLT测试对于从事半导体封装测试相关的岗位比较重要,尤其是封测厂如日月光、安靠、长电等测试相关的技术人员,或者芯片研发团队的量产相关岗位如产品工程师、测试工程师等,都属于必备的基础知识。

花了这么多时间,终于把芯片生产测试流程给大家讲清楚了。希望我讲的内容能让大家对芯片的生产测试流程有一些了解,知道芯片是怎么来的。如果你正在或者将来从事半导体行业,希望这些内容能够帮助到你。

本文详细介绍了芯片从晶圆制造、CP测试、芯片封装、FT测试到SLT测试的全过程。晶圆制造通过光刻技术将电路设计在硅片上,CP测试筛选合格芯片,芯片封装将芯片与外部电路连接,FT测试是出货前的最终质量把关,SLT测试则关注于板级或系统级的功能验证。了解这些流程对半导体行业相关人员至关重要。

本文详细介绍了芯片从晶圆制造、CP测试、芯片封装、FT测试到SLT测试的全过程。晶圆制造通过光刻技术将电路设计在硅片上,CP测试筛选合格芯片,芯片封装将芯片与外部电路连接,FT测试是出货前的最终质量把关,SLT测试则关注于板级或系统级的功能验证。了解这些流程对半导体行业相关人员至关重要。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?