一、GPIO简介

在ZYNQ中,PS端的引脚资源ZYNQ PS 中的外设可以通过 MIO( 54pin,Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚上,也可以通过 EMIO 连接到 PL 端。

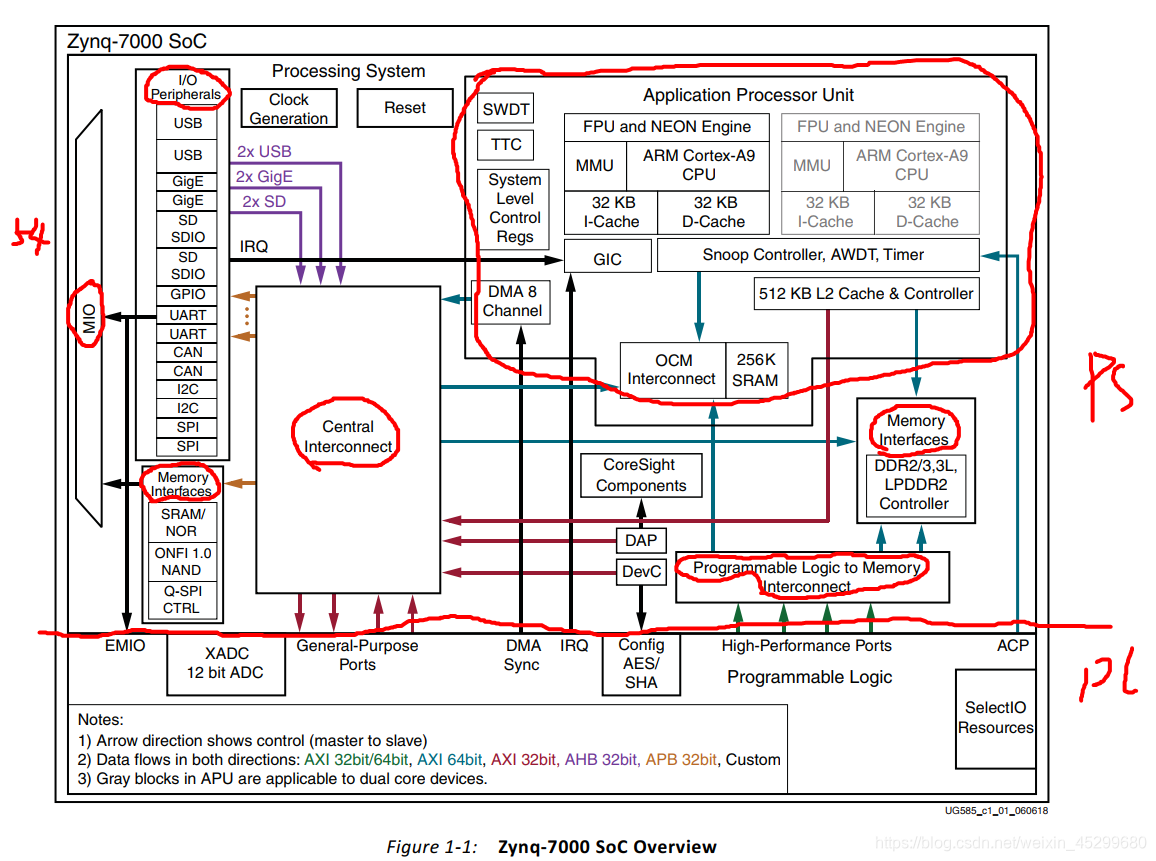

zynq7000 SOC 结构见下图:

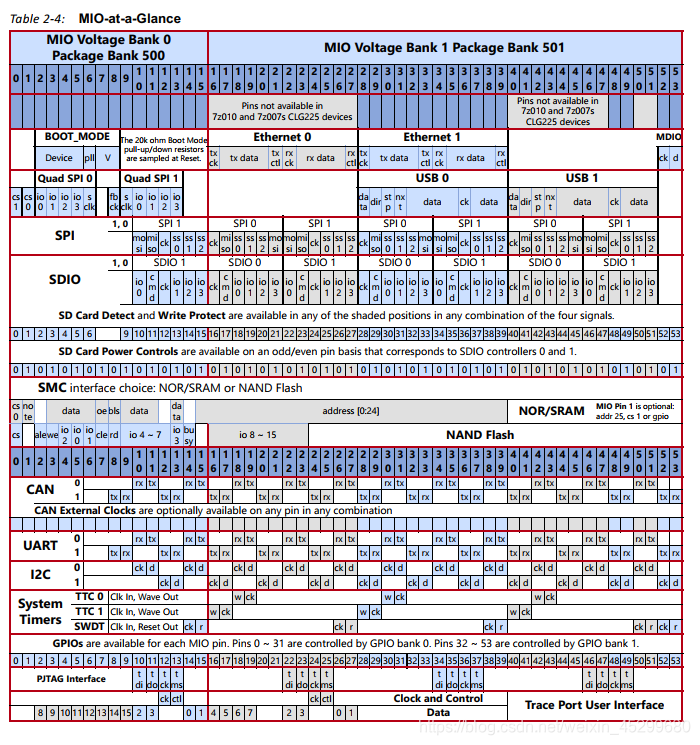

PS 所有的外设都可以通过 MIO 访问,这些外设也是与 MIO 进行连接,每个 MIO 虽然可以独立控制,以及独立驱动单个引脚的外设,但对于 QSPI、 USB、以太网等这些外设,其于 MIO 的连接有着特殊的要求,而MIO 一但选定,引脚位置就已经确定下来了,不需要添加引脚约束。

MIO引脚表:

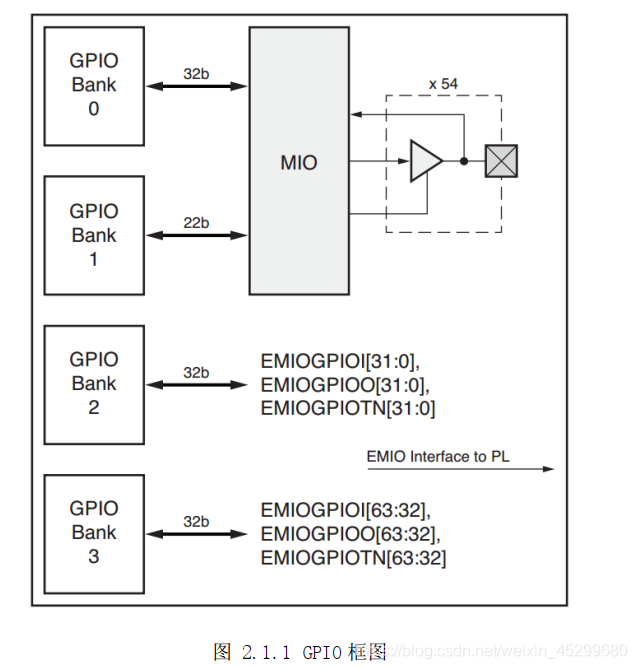

GPIO 是英文“ general purpose I/O”的缩写,即通用的输入/输出。它是PS端的一个外设,用于观测和控制引脚,共分为4个bank,其中前两个bank与MIO相连(由于MIO只有54个pin,故bank0为32位,bank1为22位),后两个bank与EMIO相连(均为32位),对PL进行数据交互。GPIO结构如下:

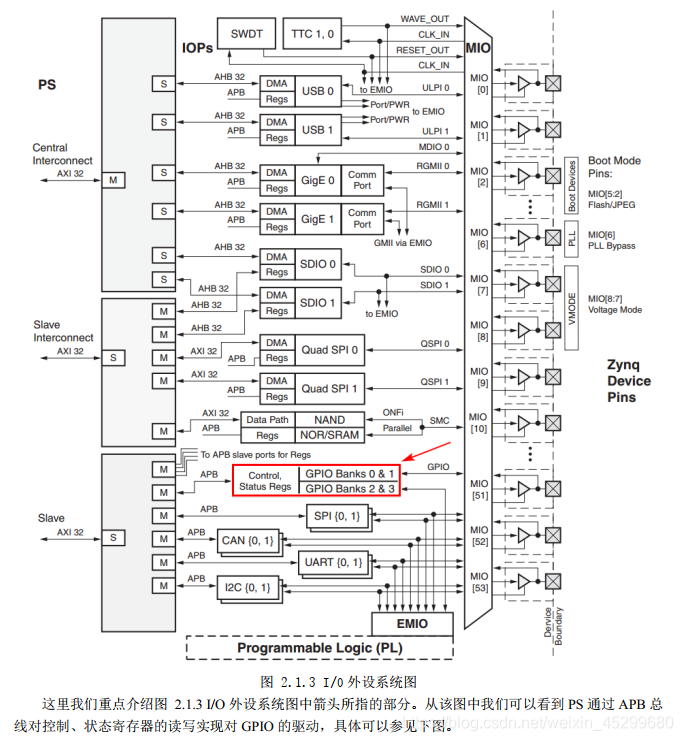

PS端是通过AXI总线与APB总线对GPIO进行控制:

需要控制GPIO通道,来决定数据是输入还是输出,见下图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1872

1872

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?