1、码元

了解调制技术需要引出“码元”的概念。

一个码元就是一个脉冲信号,即一个最小信号周期内的信号。以高电平代表“1”,低电平代表“0”。一个代表“1“或“0“的信号,就是一个码元。所以,有没有可能让一个码元/脉冲信号携带的信息量是2或是4bit呢?

答案是肯定的。一个码元可以包含多个bit数据,包含的bit数称为码元的宽度。比特率是指一秒钟可以发送多少bit的数据,波特率是指一秒钟可以发送多少码元。当一码元携带2bit数据,那么比特率=波特率的2倍。

一个二进制信号,比如0或1,就是1bit。现在有8bit数据,如果用二进制码元(一次只运送一个比特),需要在信道上传输八次脉冲信号,如果用四进制码元(一次能运送2个比特),需要在信道上传四次脉冲信号……因此码元携带比特越多,传输的脉冲信号次数越少,传输速度就越快。

2、二进制调制技术(NRZ)

高速信号: 在传输速率小于 28Gb/s 或超短距离传输的情况下,一 般采用 NRZ 码进行传输。

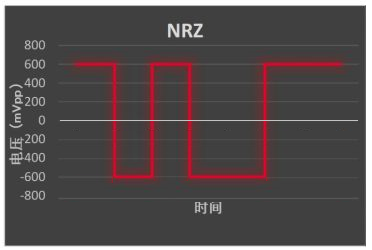

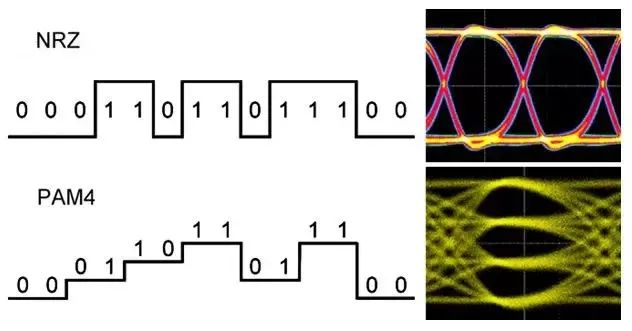

NRZ:是“ Non-Return-to-Zero ”的缩写,字面意思叫“不归零”,也就是不归零编码。非归零码用高低两种电平{1,0}传递信息,也称为 PAM2 码。其中“1”通常用高电压表示,而 “0”通常用低电平表示。

NRZ 码每一个符号周期可以传输一位信息,0 或者 1。此外,所谓“不归零”,不是说没有“0”,而是说每传输完一位数据,信号无需返回到零电平。(显然,相比RZ,NRZ节约了带宽。)

NRZ有单极性不归零码和双极性不归零码。归零码每个数据表示完毕后,都会回归到零电平状态,而非归零码,没有回归到零电平的过程。

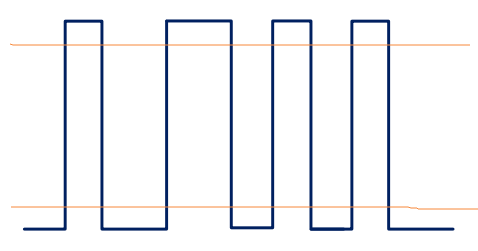

单极性不归零码:用恒定的正电压来表示“1”,无电压用来表示“0”。每个码元时间的中间点是“采样时间”,判决门限为半幅度电平(即 0.5)。即接收信号值在 0.5 与 1.0 之间,就判为“1”码,如果在 0 与 0.5 之间就判为“0”码。

单极性不归零码

双极性不归零码:“1”码和“0”码都有电压,但是“1”码是正电平,“0”码是负电平,正和负的幅度相等,故称为双极性码。

此时的判决门限为零电平,接收机使用零判决器或正负判决器,接收信号的值若在零电平以上为正,判为“1”码;若在零电平以下为负,判为“0”码。

双极性不归零码

以上两种编码都是在一个码元的全部时间内为某一个电平(高电平或低电平),每一位编码占用了全部码元的宽度。故这两种编码都属于全宽码,也称作 NRZ 码。

在光模块调制里面,我们是用激光器的功率来控制0和1的。

简单来说,就是发光,实际发射光功率大于某门限值,就是1。小于某门限值,就是0。

NRZ调制

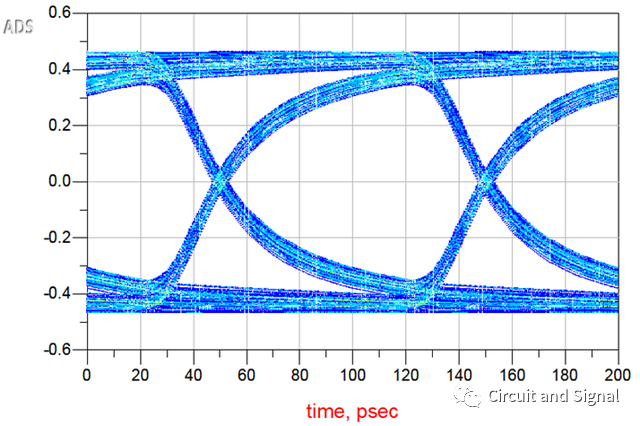

眼图仿真

NRZ的优缺点

优点:简单易实现,直接传递二进制信息,信噪比高,对于信道的要求也不高,非常适合短距离传输应用,可以直接通过电线、光纤 等介质进行传输。使用 NRZ 码传输, 接收端无需解码电路,可以简化接收端结构。

缺点:在高速传输时容易出现时钟漂移、码间串扰等问题,会 影响传输质量,使误码率增加。

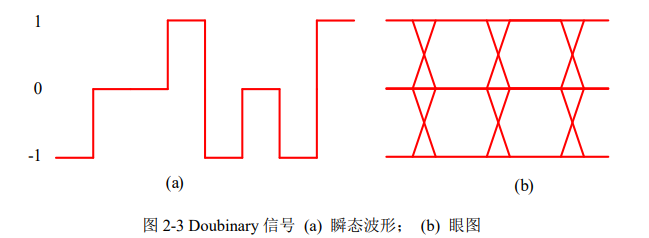

双二进制码

双二进制码(Doubinary, DB)是一种在数字通信系统中常用的调制方式之一,也 是一种三电平信号。它是将原始的二进制码信号进行叠加、滤波等处理后得到的信号, 可以用来提高光通信系统的传输性能和距离容限。双二进制码可以从非归零码中简单地转换得到。

在双二进制码中,相邻两个符号的波形幅度和极性相反,即正负相间。由于这种波形特性,双二进制码在传输过程中对色散和非线性失真的容限比常规的非归零码要高,能够更好地抵抗信道噪声和干扰,可以通过调制 3 个电平来 降低自身频谱,从而有效地减少信号的带宽,从而提高传输速率。然而,双二进制信号的差 分解码会引入码间干扰。在接收端,需要通过差分解码的方式将信号还原为原始的二进制信 号,以消除码间干扰。

3、四电平调制技术(PAM4)

超高速信号:现在采用PAM4调制的高速信号有:GDDR6X/GDDR7, PCIE6, IEEE802.3xx(高速以太网)50G及其以上的带宽等,可以看到以PAM4为代表的多电平调制可能在以后将是常态。

在800GE/400GE/200GE/50GE接口中的物理层采用50Gbps/lane的PAM4编码技术。 PAM4广泛应用于50G、单波100G、400G(非ZR)光模块等。

随着带宽需求的不断增加,我们需要想尽办法增加单位时间内传输的逻辑信息。

PAM4:是4-Level Pulse Amplitude Modulation,中文名叫做四电平脉冲幅度调制。是一种调制技术,采用4个不同的信号电平来进行信号传输。

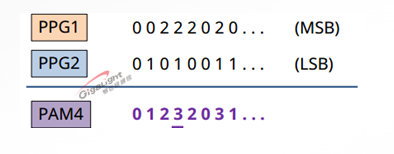

PAM4 调制方式采用一定的规则将二进制中的逻辑信号“0”和“1”转换为逻辑信号“0”,“1”,“2”和“3”,用四个不同的电平来进行信号传输。

PAM4 信号的每个符号周期包含了两个比特的逻辑信息,比如用逻辑信号“0”来代表逻辑信号“00”,“1”代表“01”,“2”代表“10”,“3”代表“11”。

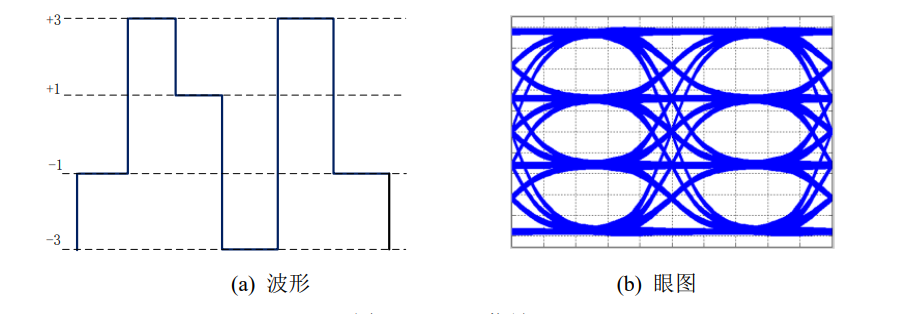

PAM4调制

这样一来,单个符号周期表示的逻辑信息,从NRZ的1bit,变成了2bit,翻了一倍。

NRZ VS PAM4 (右边是眼图)

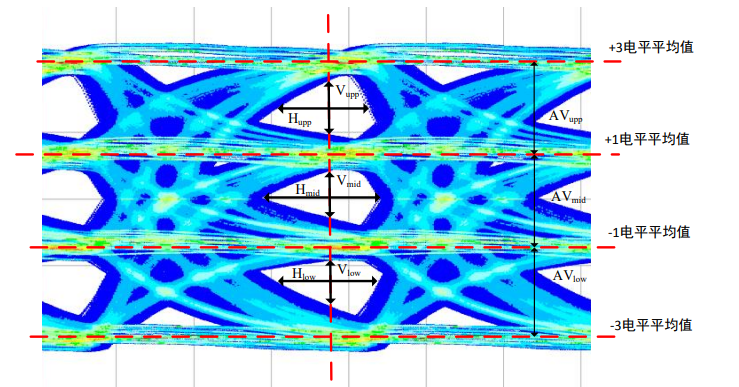

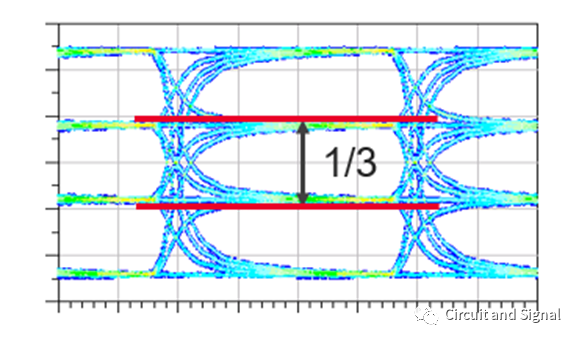

PAM4由于有4个电平,那我们可以对比NRZ猜想:PAM4的眼图应该有3个眼睛,确实是这样!PAM4信号的眼图如下图所示:

那么问题来了,这么好的技术,为啥之前不用?如果4电平能够翻一倍,为啥我们不搞个8电平、16电平、32电平?速度随便翻倍?

主要原因,实现PAM4,需要激光器能够做到对功率的精确控制。如果控制不好,就会造成很高的误码率,只能重新吹,影响信号传输效率。PAM4对噪声更加敏感。如果噪声太大,显然也会导致PAM4调制无法正常工作。

我们以单路25G波特率为例。所谓波特率(Baud Rate),就是一秒钟可以发送多少个完整脉冲。

例如25G EML芯片,约一秒钟发送25×109个脉冲(每秒250亿个泡泡)。采用NRZ的话,那就是速率(比特率,bit rate)是25Gbps。采用PAM4调制技术的话,翻个倍,变成50Gbps。所以,1个25G EML芯片采用PAM4调制之后,就可以做成了单通道50G的PAM4光模块。

现在很多大容量的光模块,都是这么double(翻倍)出来的。

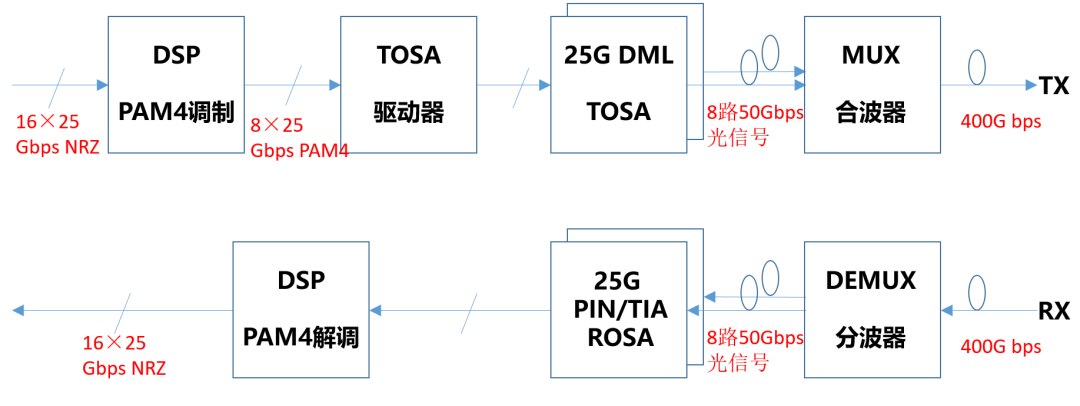

我们再举一个基于PAM4调制的400G DML光收发模块的例子。

发送单元信号时,16路25G NRZ电信号从电接口单元输入,经过DSP处理器对电信号进行预处理、PAM4调制后,输出8路25G PAM4的电信号,加载到驱动器芯片上,通过8路的激光器将高速电信号转换8路50Gbps的高速光信号,通过波分复用器合波后,合成1路400G的高速光信号输出。

接收单元信号时,将接收的1路400G的高速光信号通过光接口单元输入,经过解复用器转换成8路50Gbps的高速光信号,通过光接收机接收输入光信号,并将所接收的光信号转换成为电信号后,经过DSP处理芯片对电信号进行时钟恢复、放大、均衡、PAM4解调后,转换成16路25G NRZ的电信号。

PAM4的优缺点

那PAM4相对NRZ有什么优势,有什么缺点呢?我们先讲优势:

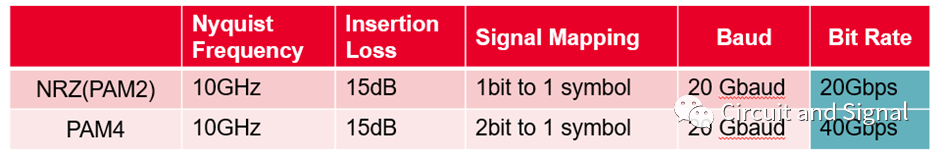

优点:传输效率高,带宽压缩。

由于PAM4一个电平(symbol)包含2bit的数据信息,在相同的内奎斯特频率开销下,PAM4可以传输的数据速率是NRZ的2倍,也就是说在提升数据速率的情况下带宽没有明显增加,如下表格所示;

缺点:信噪比低,对噪声的容忍度降低,此外TX/RX的设计难度增加,成本增加。

有4个电平将NRZ的一个眼图分成了3个,所以它对噪声更加敏感,更容易受到干扰。听起来PAM4的缺点多于优点,但是在信号速率不断飙升的情况下,这是迫不得已的一种方式。当然和其他方式相比,PAM4带来的收益可能远大于其他方案或者是它的缺点。

PAM4实现方法

由于 PAM4 信号具有 4 个电平,所以 PAM4 接收端电路比 NRZ 传输系统更复杂,对信噪比的要 求也更高。依据实现方法的不同,SerDes 系统接收机可分为基于 ADC/DSP 混合信号架构和传统的架构。

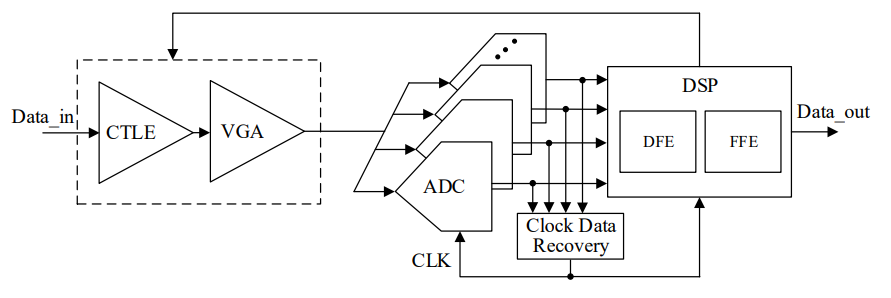

基于 ADC/DSP 的 PAM4 接收机架构

在 PAM4 信号下,一个 UI 有 4 个电平,接收机的模拟前端需要对 4 个电平进行区分和判决。而多比特的 ADC 能够将模拟信号量化为数字信号,可以很好地完成对接收信号的采样和判决作用,后续的信号还可以通过 DSP 技术实现数字域的均衡。

基于 ADC/DSP 混合信号架构 PAM4 接收端架构

进过信道衰减后的差分信号首先经过 CTLE 均衡,同时可变增益放大器(VGA)将信号调整到合 适的幅度,以便满足 ADC 的对输入信号的摆幅要求。ADC 采用时序交织方式设计,以便减小时序 压力,对于一个 56Gb/s PAM4 信号的接收端而言,可以采用 8 组时序交织的 SAR ADC,每组有 4 个 7bit 的 ADC,这样 ADC 的工作频率可以降至 875MHz。ADC 对信号进行采样并转化为数字信号, 进入数字域后,运用 DSP 设计数字 FFE 和 DFE 滤波器进一步均衡。CDR 从 ADC 输出的信号中恢 复出时钟信号,提供给 ADC 和 DSP 使用。同时,在 DSP 中还实现了自适应算法,输出反馈信号控 制 CTLE 和 VGA 的增益。

这种基于 ADC/DSP 架构的好处是结构灵活,具有强大的均衡能力,在超高速 SerDes 接收系统 中,DSP 通常可以实现十个抽头以上的 FFE 和一两个抽头的 DFE,利用先进工艺可以实现接收机 性能的提升;缺点是功耗大,结构复杂,需要设计高速高精度的 ADC。数字架构对 PAM4 信号的线 性度要求高,并且由于 ADC 存在量化误差,ADC 的好坏会直接影响接收机的性能。

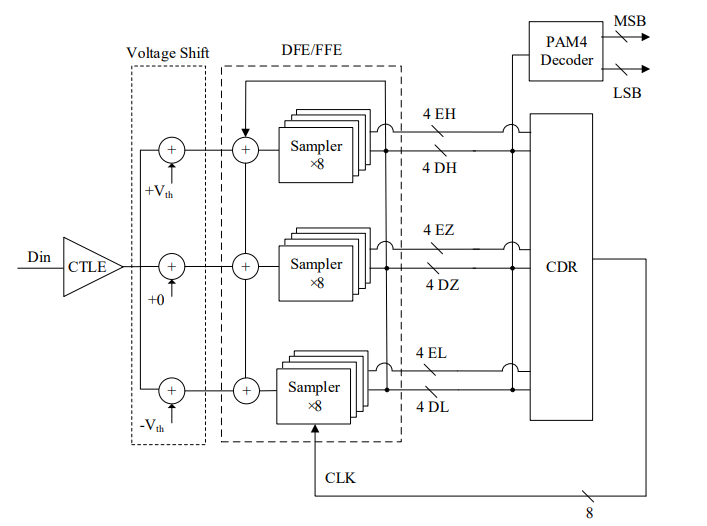

传统 PAM4 接收机架构(模拟Combine)

相比 NRZ 信号,传统架构的 PAM4 接收端需要增加多电平判决电路,同时 DFE 的实现采用 模拟方式。

传统架构 PAM4 接收端电路

传统架构 PAM4 接收端这是一个四分之一速率的接收机,经过信 道衰减的信号 Din 先经过 CTLE 进行均衡,电平移位模块(Voltage Shift)依据{+Vth,+0,-Vth}三个 参考电平将 PAM4 信号眼图上,中,下三个眼睛分别移动到零电平处。移位后的信号被分为并行的 三路,每一路都有一组包含 8 个采样器的采样单元,采样器组利用四分之一速率的八相时钟对信号 的中心和边沿进行判决采样,得到数据信息 DH,DZ,DL 和边沿信息 EH,EZ,EL。将三路数据信 息 DH,DZ,DL 反馈至采样器前,构成 DFE 反馈补偿和 FFE 补偿。同时 CDR 模块接收数据信号 (DH/DZ/DL)和边沿信号(EH/EZ/EL),输出准确的时钟信号以供采样器使用。

采用电平移位结构的传统接收端无需设计高性能的 ADC,也不需要利用 DSP 占用面积和消耗 功耗,具有经济,功耗低等优势。传统架构的接收机广泛应用于50Gb/s 以下的传输系统中,在满足数据速率的同时能够达到功耗和性能的平衡。

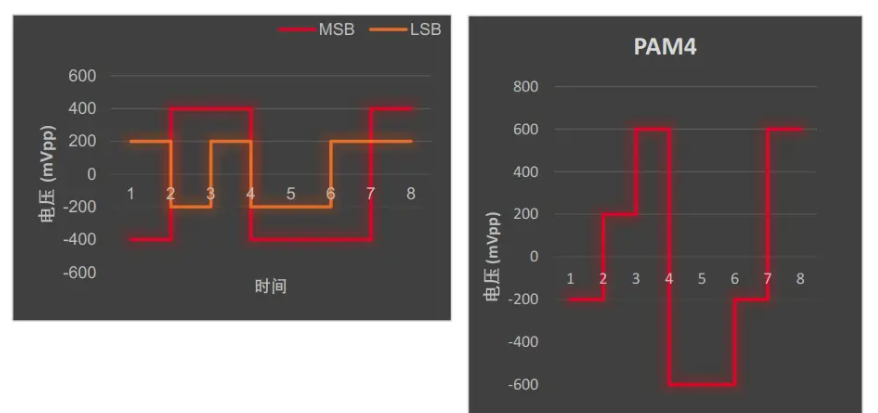

该架构通过两路NRZ信号进行相加操作,基于MSB+LSB Combiner来实现PAM4信号,有两路NRZ信号进行相加操作。

在图中,MSB和LSB NRZ码型使用不同的幅度表示:-400 mVpp至400 mVpp MSB和-200 mVpp至200mVpp LSB。

使用两个NRZ通道生成PAM4信号

CDR主要是用模拟电路的处理方式,对时钟做恢复,接收端先对传输过来的模拟信号进行时钟恢复,再转为数字信号。

那么,可否先转为数字信号,再恢复时钟呢?答案也是可以的。用到的处理电路,就是DSP。

DSP用于serdes,初衷并不是为了做时钟恢复,而是因为PAM4及以上的传输方式下,码元的处理较为复杂,需要由DSP完成。然后因为DSP有更好的数字处理能力,所以除了提供CDR能提供的时钟恢复功能之外,还可以进行色散补偿操作,去除噪声、非线性等干扰因素,对于整个电路的提升是优于CDR的。

DSP的短板在于,因为处理更复杂,所以功耗更高,成本也更高,而且DSP的延时也要长于CDR。

目前业内的主流观点认为,DSP更适合长距或中长距,CDR可能更适合短距或中短距。用于serdes的DSP主要是16nm及以下的方案,研发费用较高,需要有较大的出货量来平摊。产业界内,单通道最高数据率大于30 Gbit/s以上,通常考虑采用PAM4+DSP的方案,30 Gbit/s以下使用NRZ+CDR。已经有业内企业在研发新的CDR技术用于替代现有的DSP方案,用于PAM,最终实现低成本和更好的可操作性。

CDR的方案包括:基于数字PLL的CDR,基于相位插值的CDR,基于电荷泵和模拟滤波器的CDR等。其中后两者被更多认为属于模拟电路。而DSP被认为是完全数字电路。

关于CDR、DSP在serdes领域的应用,以及与NRZ、PAM的搭配关系,与国外相比目前国内的相关研究还不够深入,国内能够获取的资料也还较少。

50G PAM4简介如下:

7004

7004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?