一:I 2C 物理层

它的物理层有如下特点:

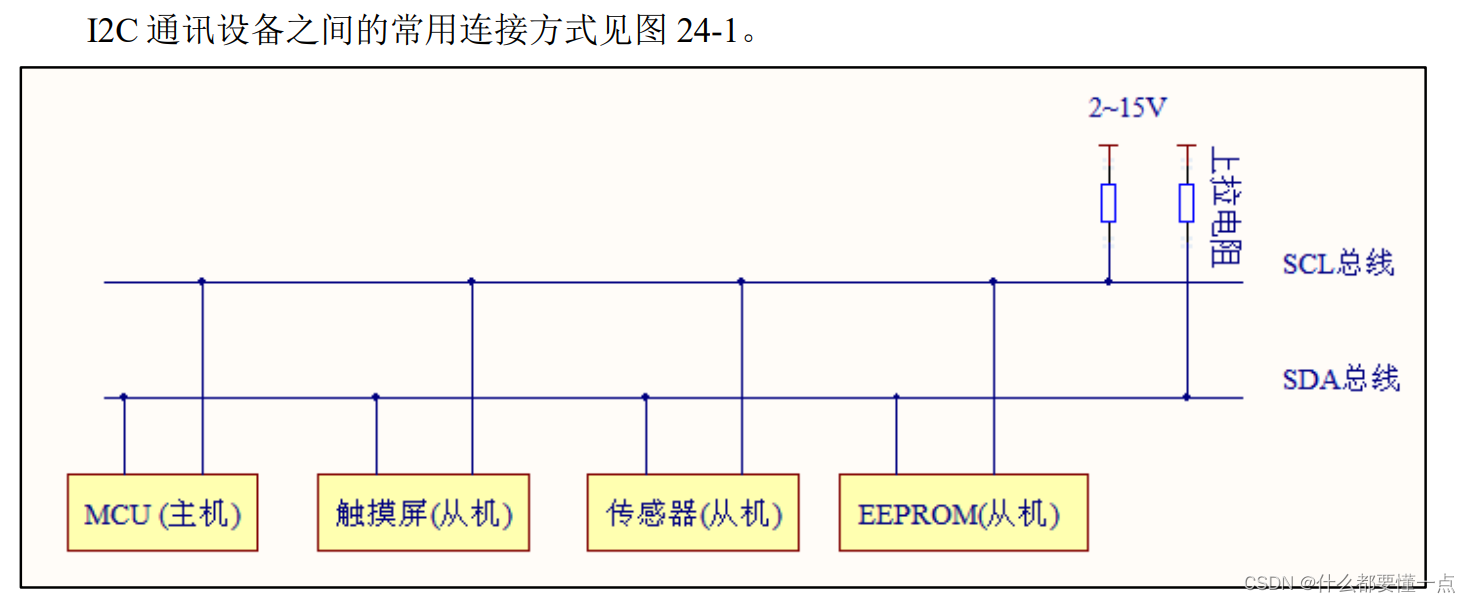

(1) 它是一个支持设备的总线。“总线”指多个设备共用的信号线。在一个 I2C 通讯总线 中,可连接多个 I2C 通讯设备,支持多个通讯主机及多个通讯从机。

(2) 一个 I2C 总线只使用两条总线线路,一条双向串行数据线(SDA) ,一条串行时钟线 (SCL)。数据线即用来表示数据,时钟线用于数据收发同步。 零死角玩转 STM32F103—指南者 第 216 页 共 824

(3) 每个连接到总线的设备都有一个独立的地址,主机可以利用这个地址进行不同设备之 间的访问。

(4) 总线通过上拉电阻接到电源。当 I2C 设备空闲时,会输出高阻态,而当所有设备都空 闲,都输出高阻态时,由上拉电阻把总线拉成高电平。

(5) 多个主机同时使用总线时,为了防止数据冲突,会利用仲裁方式决定由哪个设备占用 总线。 (6) 具有三种传输模式:标准模式传输速率为 100kbit/s ,快速模式为 400kbit/s ,高速模式 下可达 3.4Mbit/s,但目前大多 I 2C 设备尚不支持高速模式。

(7) 连接到相同总线的 IC 数量受到总线的最大电容 400pF 限制 。

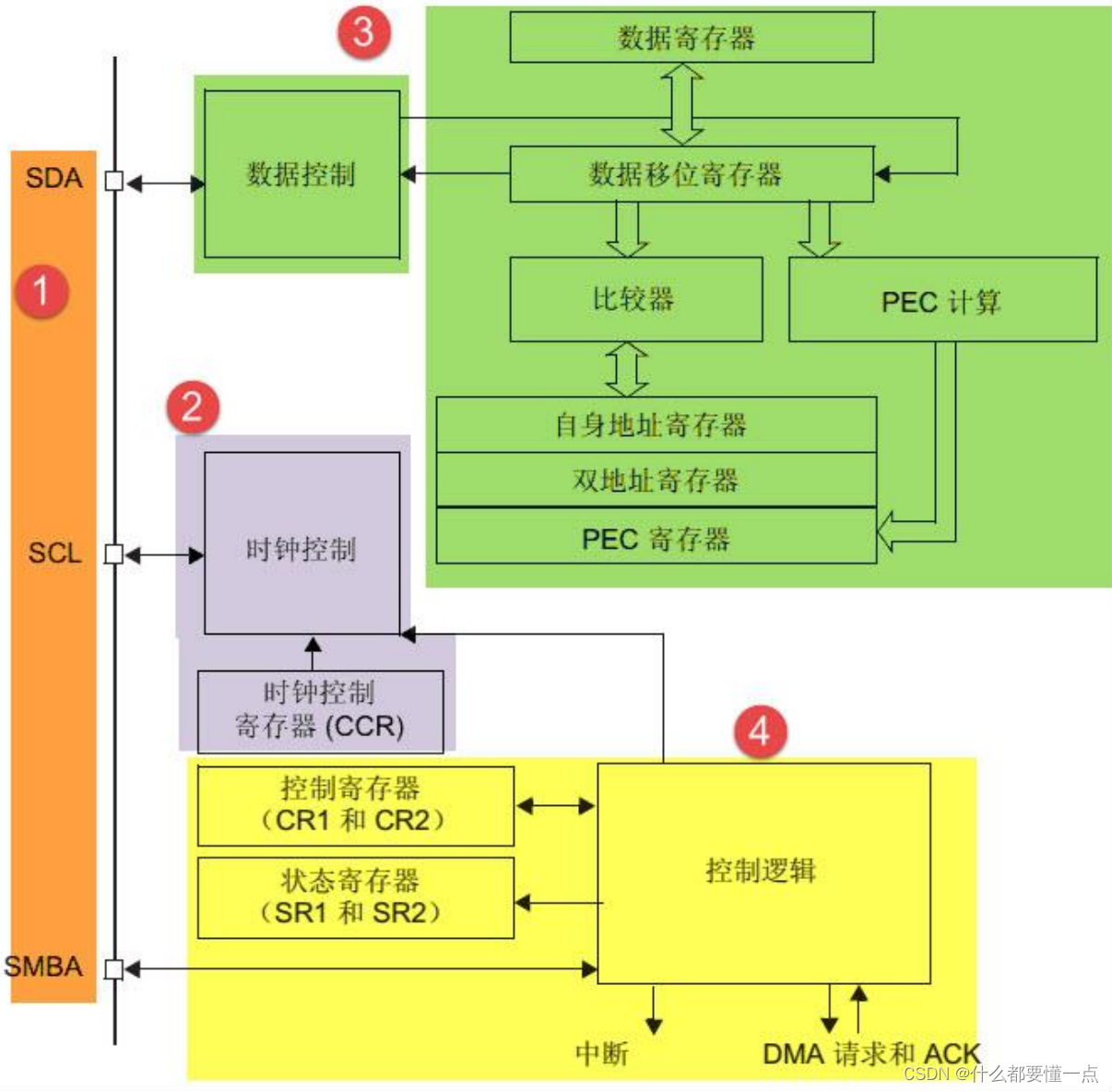

I 2C 架构剖析(按序号解析)

1. 通讯引脚(橘黄色部分)

I 2C 的所有硬件架构都是根据图中左侧 SCL 线和 SDA 线展开的(其中的 SMBA 线用于 SMBUS 的警告信号,I2C 通讯没有使用)。STM32 芯片有多个 I2C 外设,它们的 I2C 通讯 信号引出到不同的 GPIO 引脚上,使用时必须配置到这些指定的引脚

2. 时钟控制逻辑

SCL 线的时钟信号,由 I 2C 接口根据时钟控制寄存器(CCR)控制,控制的参数主要为时 钟频率。配置 I2C 的 CCR 寄存器可修改通讯速率相关的参数:

可选择 I2C 通讯的“标准/快速”模式,这两个模式分别 I2C 对应 100/400Kbit/s 的 通讯速率。

在快速模式下可选择 SCL 时钟的占空比,可选 Tlow/Thigh=2 或 Tlow/Thigh=16/9 模式,我们知道 I2C 协议在 SCL 高电平时对 SDA 信号采样,SCL 低电平时 SDA 准备下一个数据,修改 SCL 的高低电平比会影响数据采样,但其实这两个模式的 比例差别并不大,若不是要求非常严格,这里随便选就可以了。

CCR 寄存器中还有一个 12 位的配置因子 CCR,它与 I2C 外设的输入时钟源共同 作用,产生 SCL 时钟,STM32 的 I2C 外设都挂载在 APB1 总线上,使用 APB1 的 时钟源 PCLK1,SCL 信号线的输出时钟公式如下:

标准模式: Thigh=CCR*TPCKL1 Tlow = CCR*TPCLK1

快速模式中 Tlow/Thigh=2 时: Thigh = CCR*TPCKL1 Tlow = 2*CCR*TPCKL1

快速模式中 Tlow/Thigh=16/9 时: Thigh = 9*CCR*TPCKL1 Tlow = 16*CCR*TPCKL1 例如,我们的 PCLK1=36MHz,想要配置 400Kbit/s 的速率,计算方式如下: PCLK 时钟周期: TPCLK1 = 1/36000000 目标 SCL 时钟周期: TSCL = 1/400000 SCL 时钟周期内的高电平时间: THIGH = TSCL/3 SCL 时钟周期内的低电平时间: TLOW = 2*TSCL/3

计算 CCR 的值: CCR = THIGH/TPCLK1 = 30 计算结果得出 CCR 为 30,向该寄存器位写入此值则可以控制 IIC 的通讯速率为 400KHz,其实即使配置出来的 SCL 时钟不完全等于标准的 400KHz,IIC 通讯的正确性也 不会受到影响,因为所有数据通讯都是由 SCL 协调的,只要它的时钟频率不远高于标准即 可。

3. 数据控制逻辑

I2C 的 SDA 信号主要连接到数据移位寄存器上,数据移位寄存器的数据来源及目标是 数据寄存器(DR)、地址寄存器(OAR)、PEC 寄存器以及 SDA 数据线。当向外发送数据的时 候,数据移位寄存器以“数据寄存器”为数据源,把数据一位一位地通过 SDA 信号线发送 出去;当从外部接收数据的时候,数据移位寄存器把 SDA 信号线采样到的数据一位一位地 存储到“数据寄存器”中。若使能了数据校验,接收到的数据会经过 PCE 计算器运算,运 算结果存储在“PEC 寄存器”中。当 STM32 的 I2C 工作在从机模式的时候,接收到设备地 址信号时,数据移位寄存器会把接收到的地址与 STM32 的自身的“I2C 地址寄存器”的值 零死角玩转 STM32F103—指南者 第 223 页 共 824 作比较,以便响应主机的寻址。STM32 的自身 I2C 地址可通过修改“自身地址寄存器”修 改,支持同时使用两个 I2C 设备地址,两个地址分别存储在 OAR1 和 OAR2 中。

4. 整体控制逻辑

整体控制逻辑负责协调整个 I2C 外设,控制逻辑的工作模式根据我们配置的“控制寄 存器(CR1/CR2)”的参数而改变。在外设工作时,控制逻辑会根据外设的工作状态修改 “状态寄存器(SR1 和 SR2)”,我们只要读取这些寄存器相关的寄存器位,就可以了解 I2C 的工作状态。除此之外,控制逻辑还根据要求,负责控制产生 I2C 中断信号、DMA 请求及 各种 I2C 的通讯信号(起始、停止、响应信号等)。

321

321

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?