数字电路静态时序分析基础

建立静态时序分析的环境

- 目的:建立静态时序分析的约束 (.sdc)

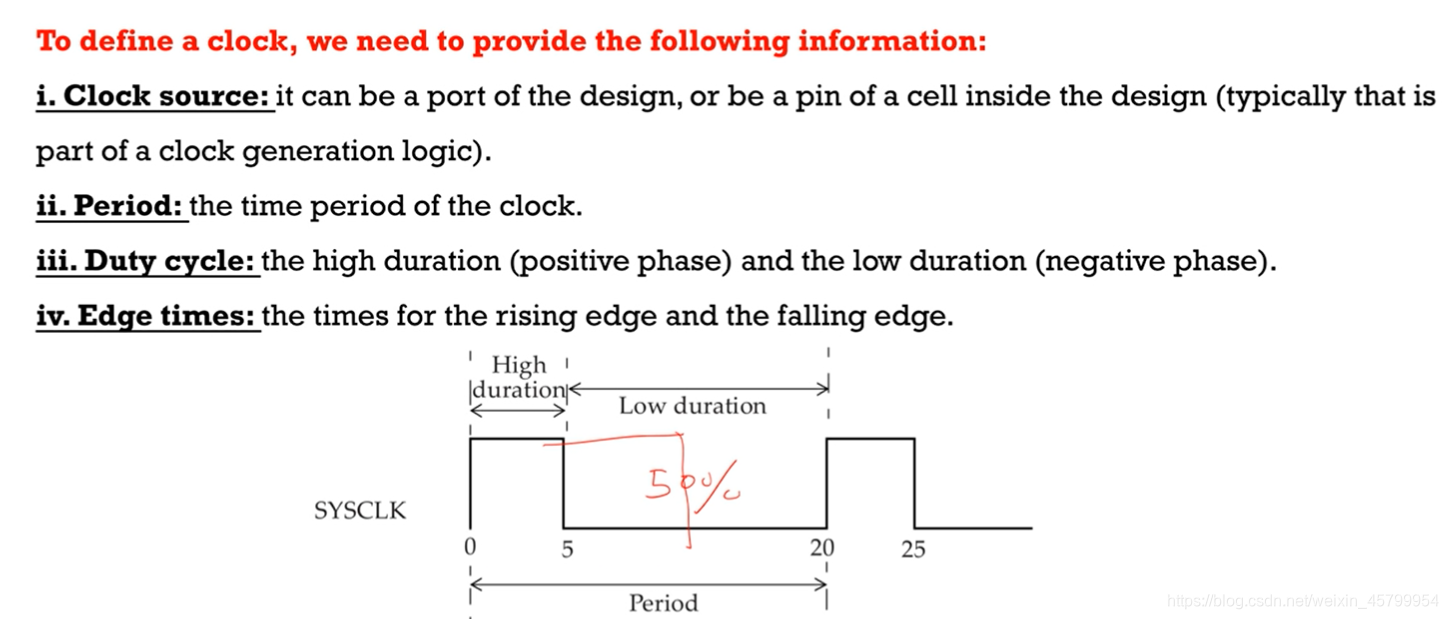

1. 时钟约束

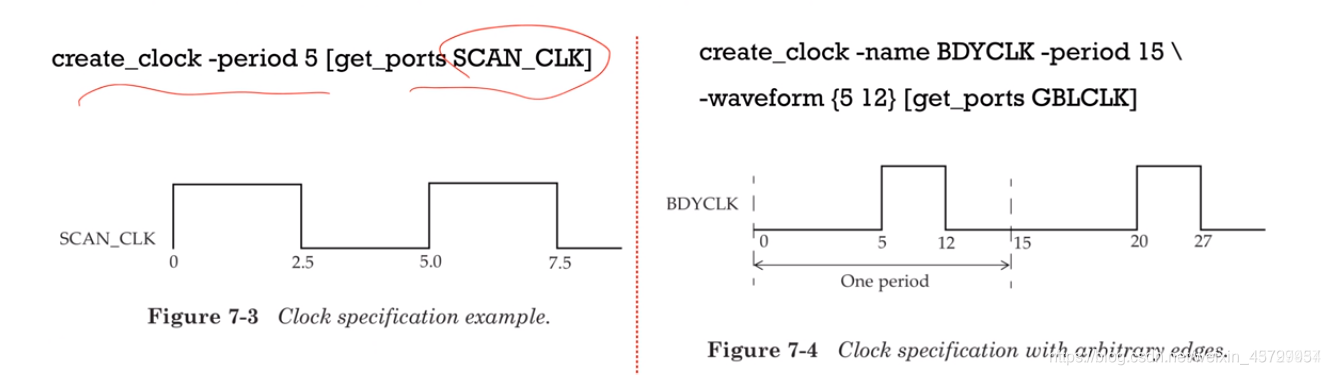

1.1 建立时钟 creat_clock

- clock source 时钟的源点

- period 时钟的周期

- Duty cycle 占空比

- Edge times 边缘翻转的时间

creat_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

creat_clock -period 5 [get_ports CLK]

creat_clock -name BDYCLK -period 15 -wave {5 12} [get_ports GBLCLK]

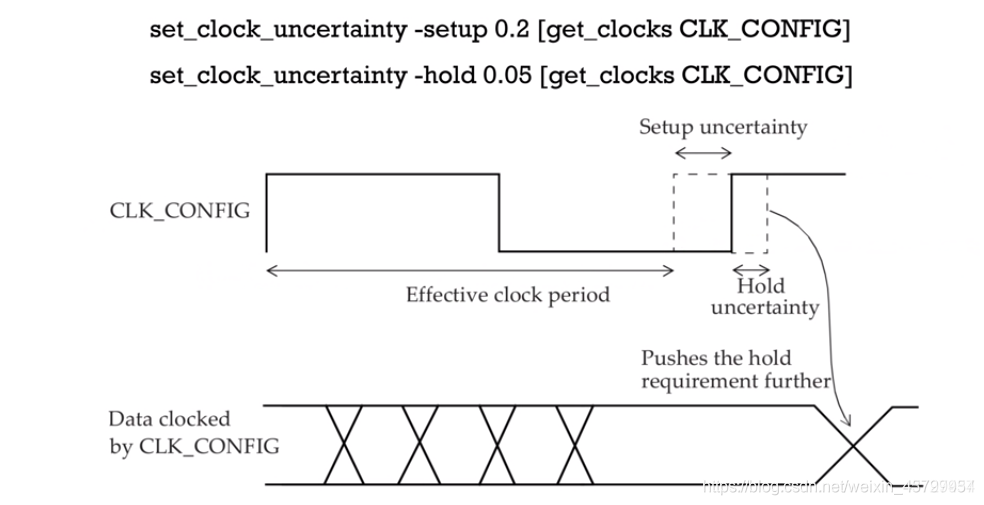

1.2 时钟不确定性 set_clock_uncertainty

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG ]

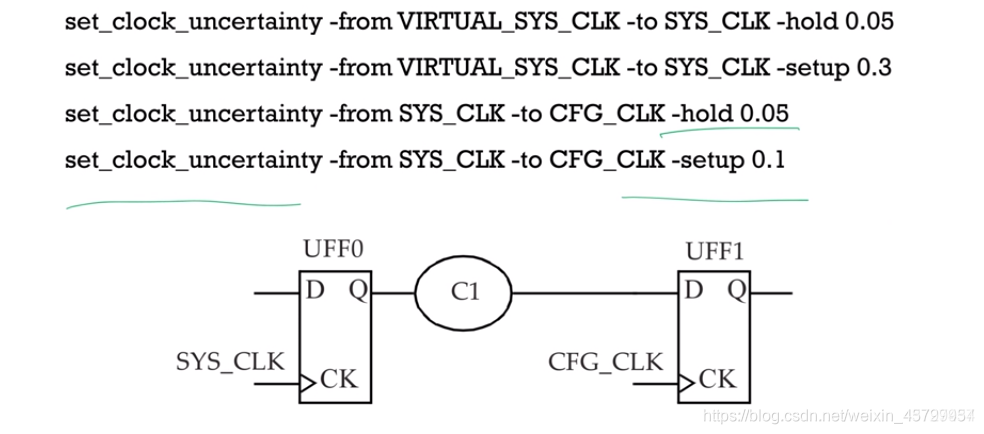

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

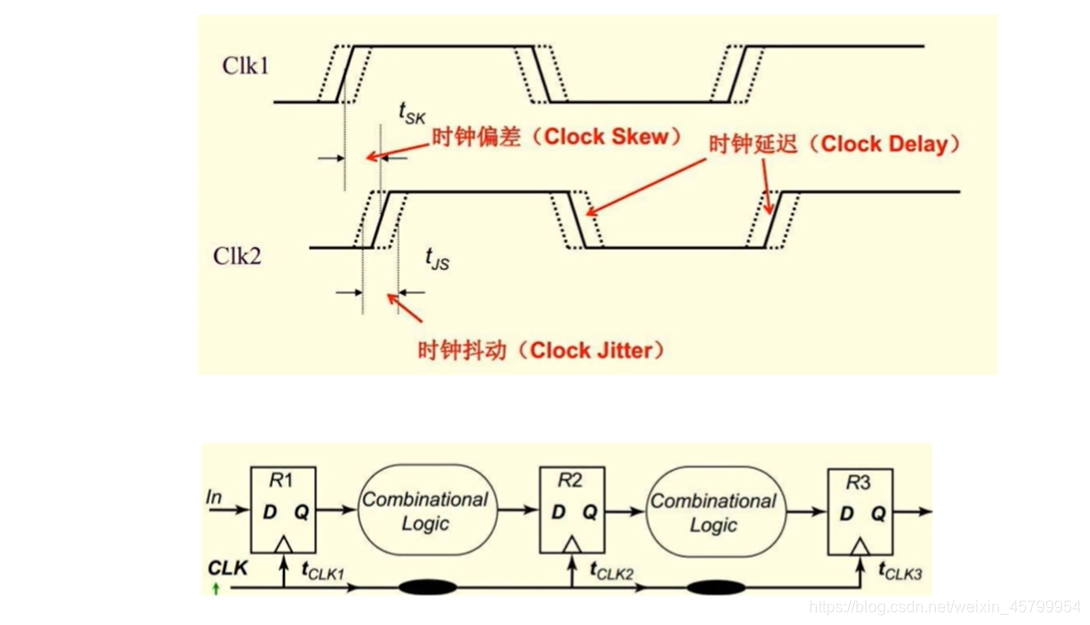

set_clock_uncertainty 来源

- clock skew时钟偏差

- clock delay时钟延迟

- clock jitter 时钟抖动

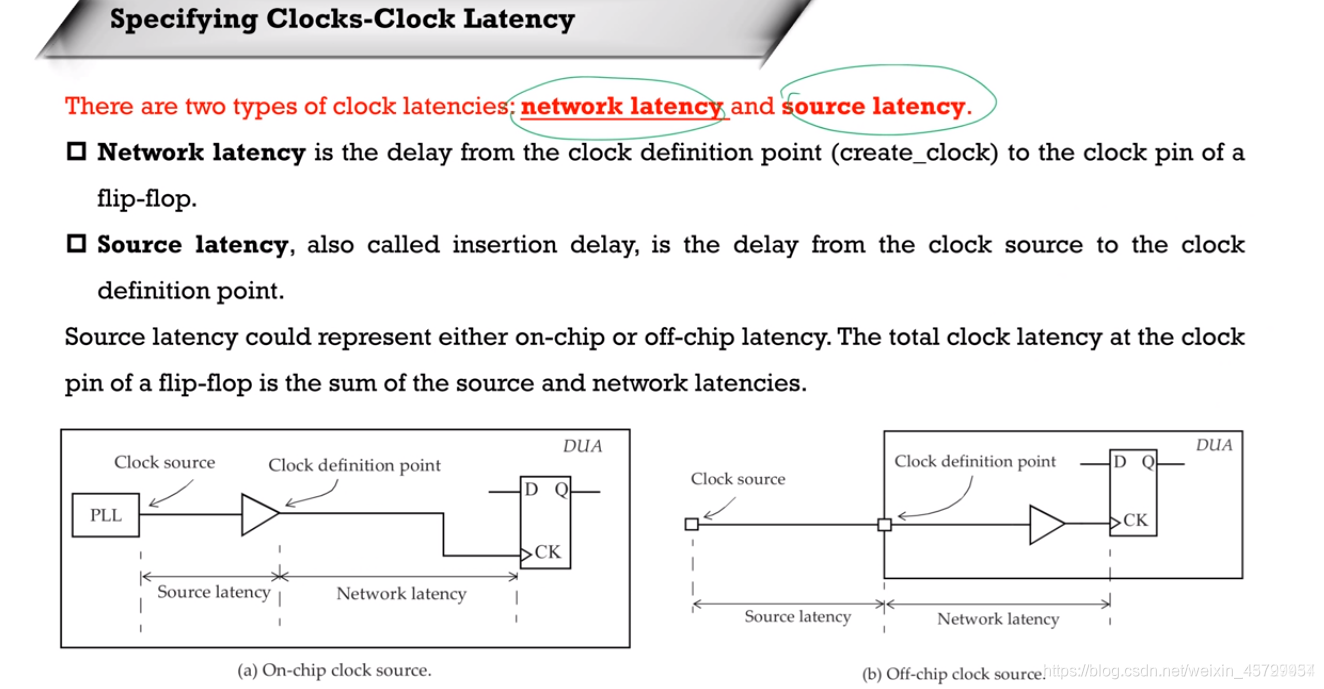

1.3 时钟延迟 set_clock_latency

两部分组成

- source latency: PPL-> 定义的时钟点

- network latency : 定义的时钟点->触发器

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

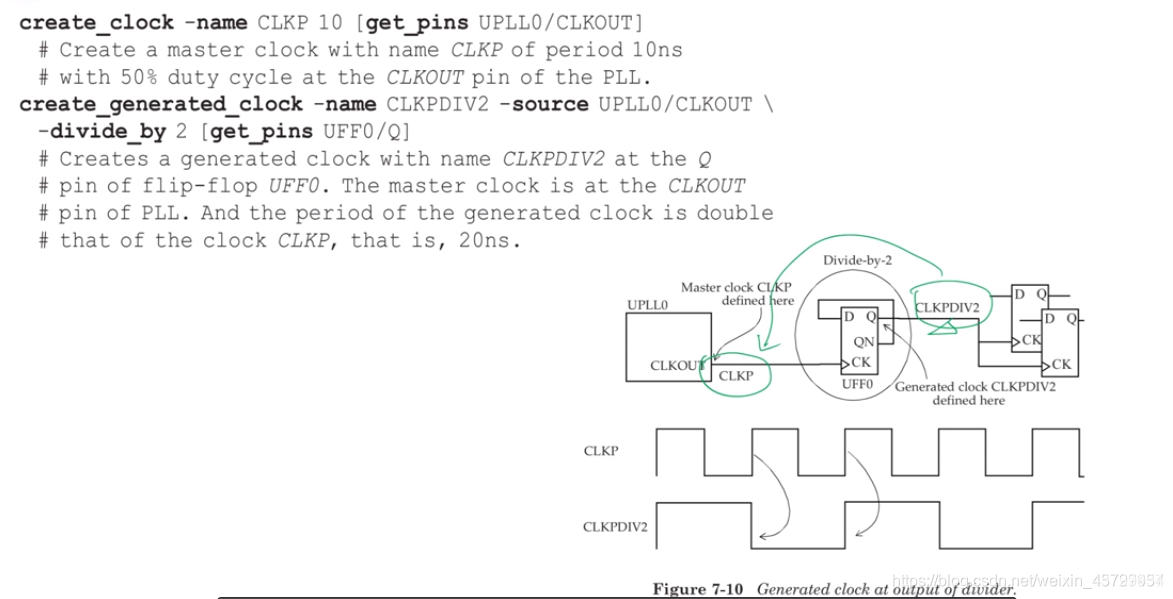

1.4 生成时钟 creat_generate_clcok

- 二分频时钟:由主时钟生成二分频的时钟,需要保持继承性

creat_clock -name CLKP 10 [get_pins UPLL0/CLKOUT] //master clock

creat_generate_clcok -name CLKPDIV2 -source UPLL0/CLKOUT -divied_by 2 [get_pins UFF0/Q] //generated clock

2. 外部约束

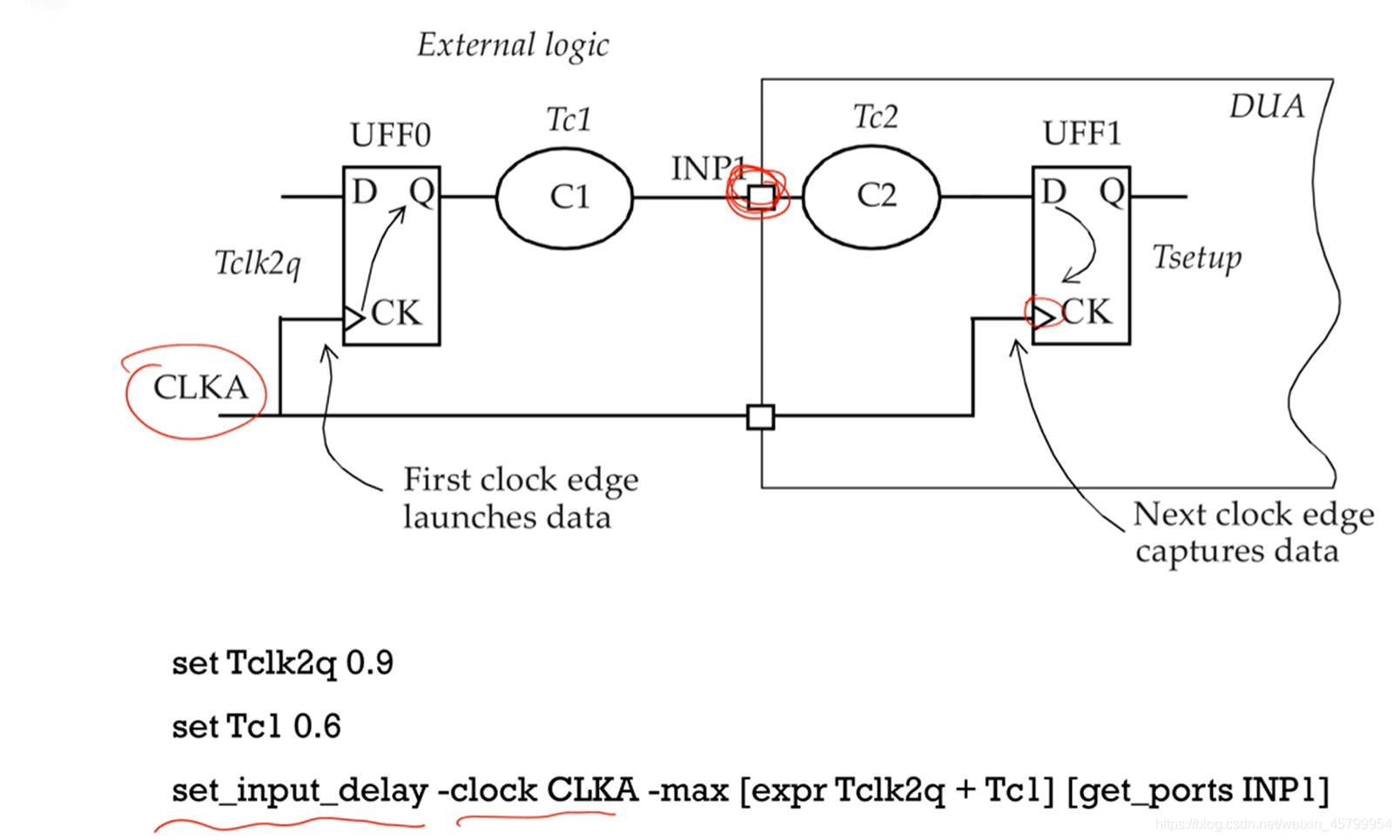

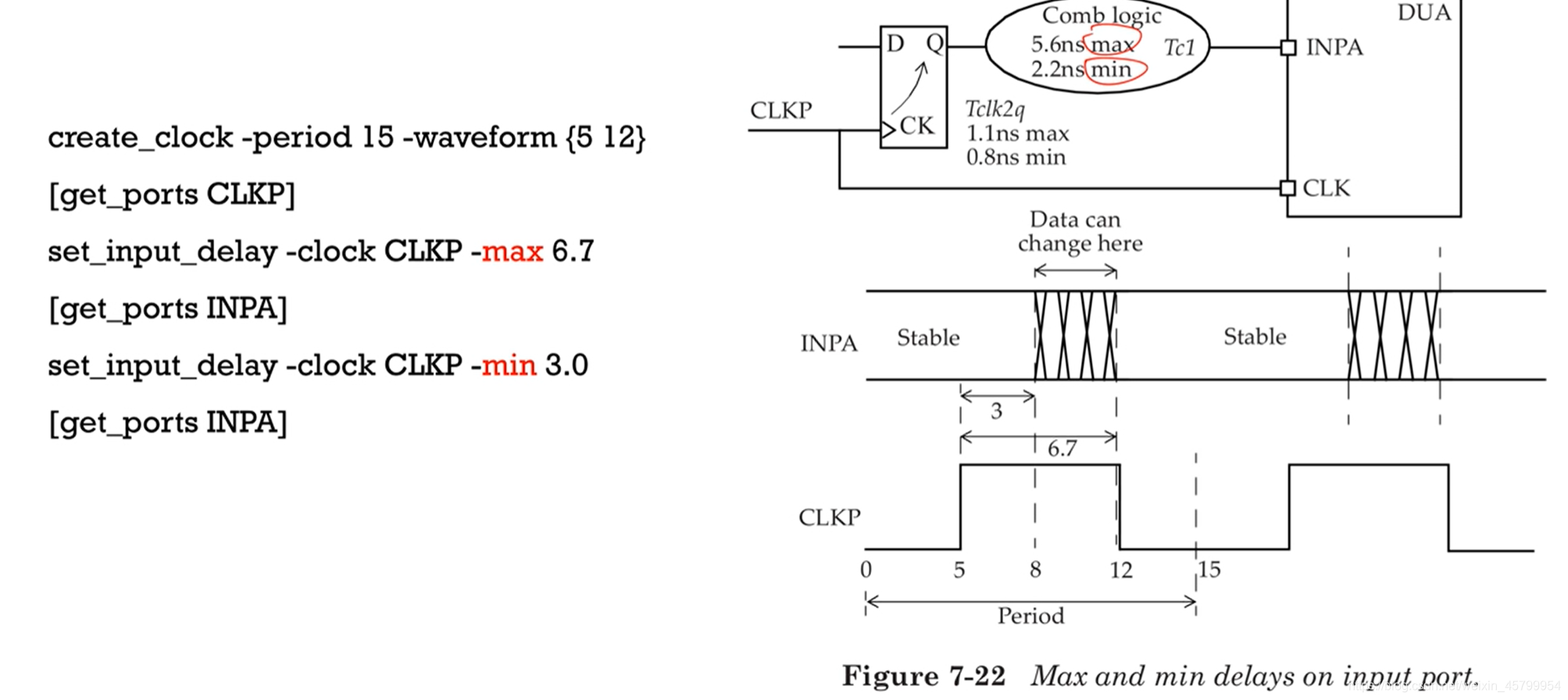

2.1 输入延时 set_input_delay

set Tclk2q 0.9

set Tcl 0.6

set_input_delay -clock CLKA -max [expr Tclk2q + Tcl] [get_ports INP1]

- 设置最大最小,分别针对建立时间和保持时间

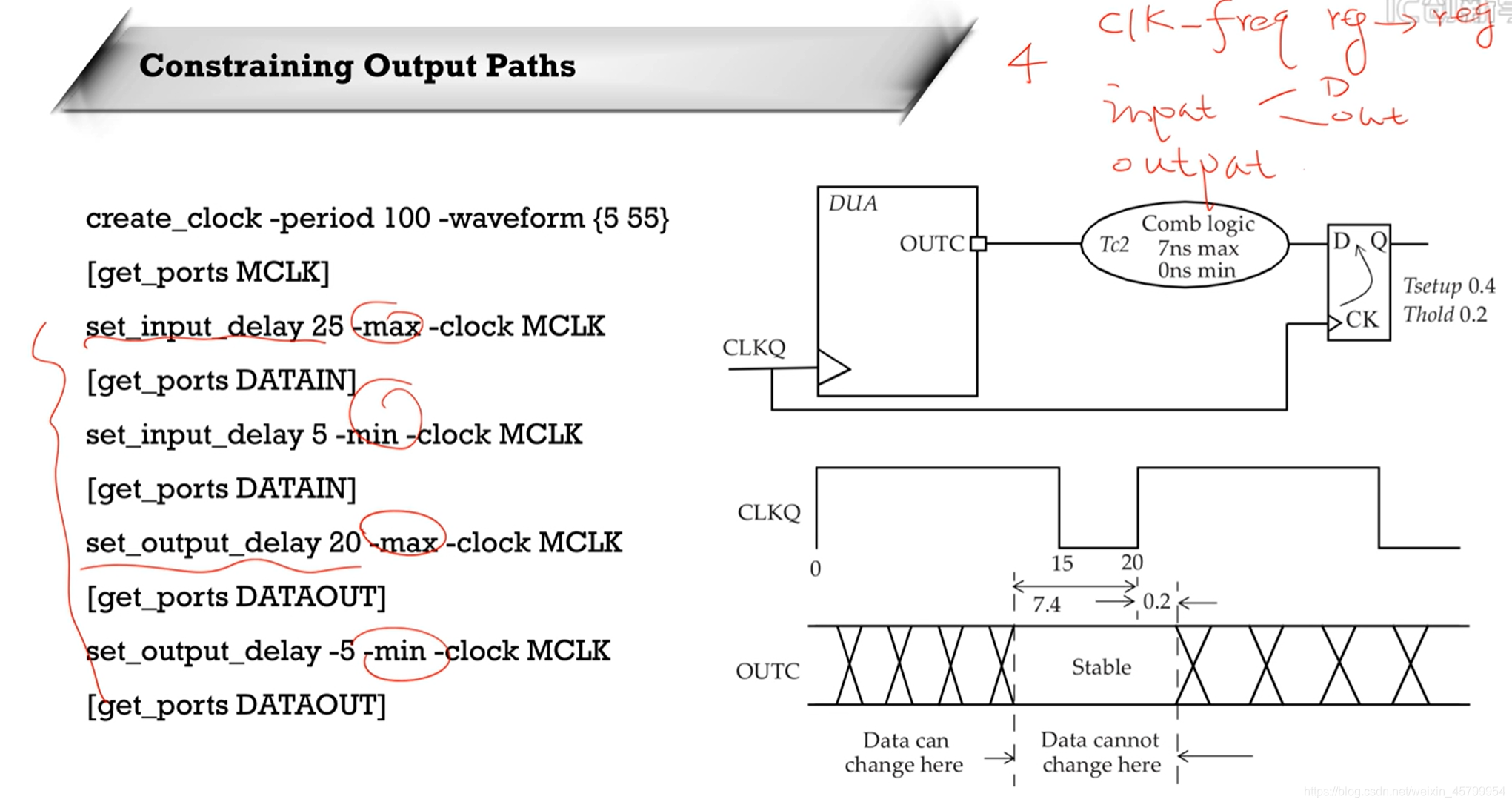

2.2 输出延时 set_output_delay

out到输出的时间

set Tc2 0.9

set Tsetup 1.1

set_output_delay -clock CLKQ -max [expr Tsetup + Tc] [get_ports OUTB]

-

最大延迟7.4 = Tsetup + Tc2

-

最小延迟 6.8 = Tc2 - Thold

-

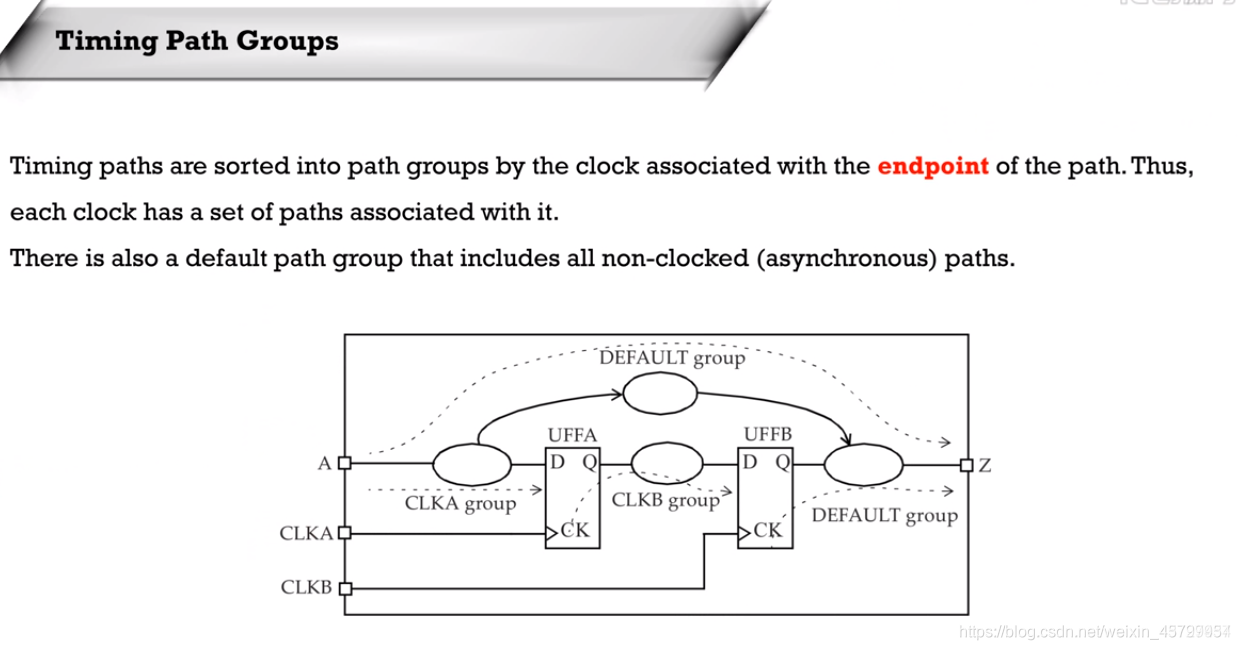

时序路径分组

-

终点属于哪个时钟就输入哪个时钟的path

-

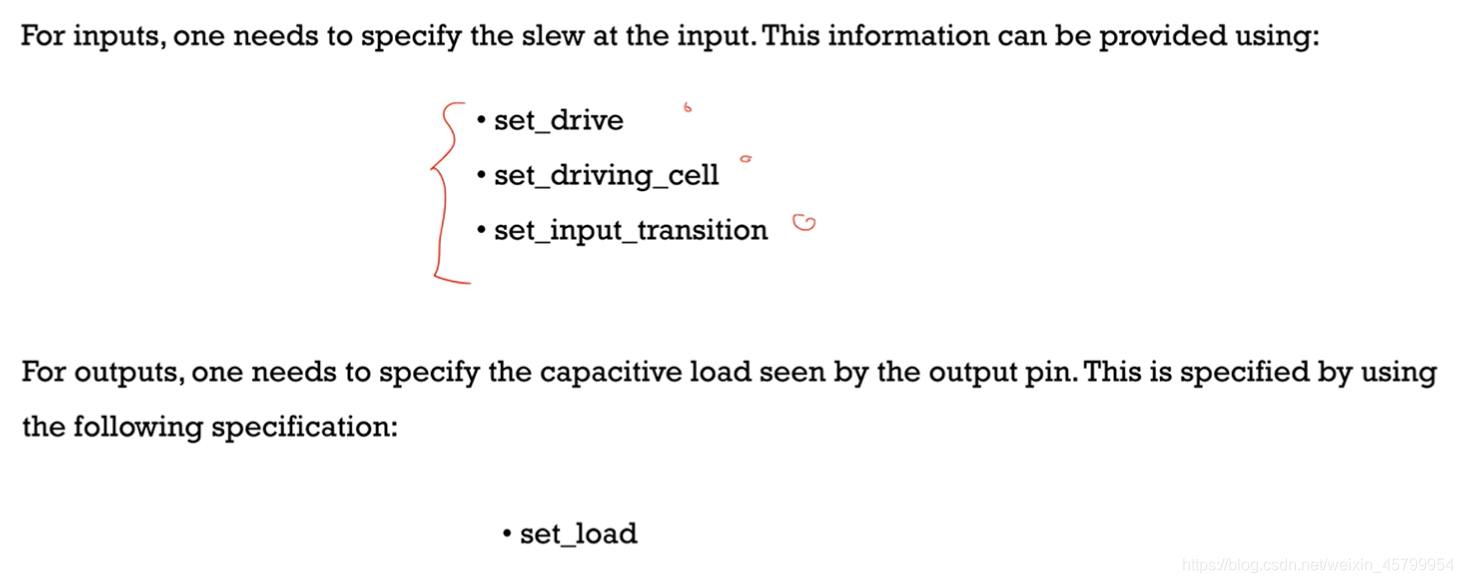

属性设置

-

指定端口的时候还会有一些额外属性。

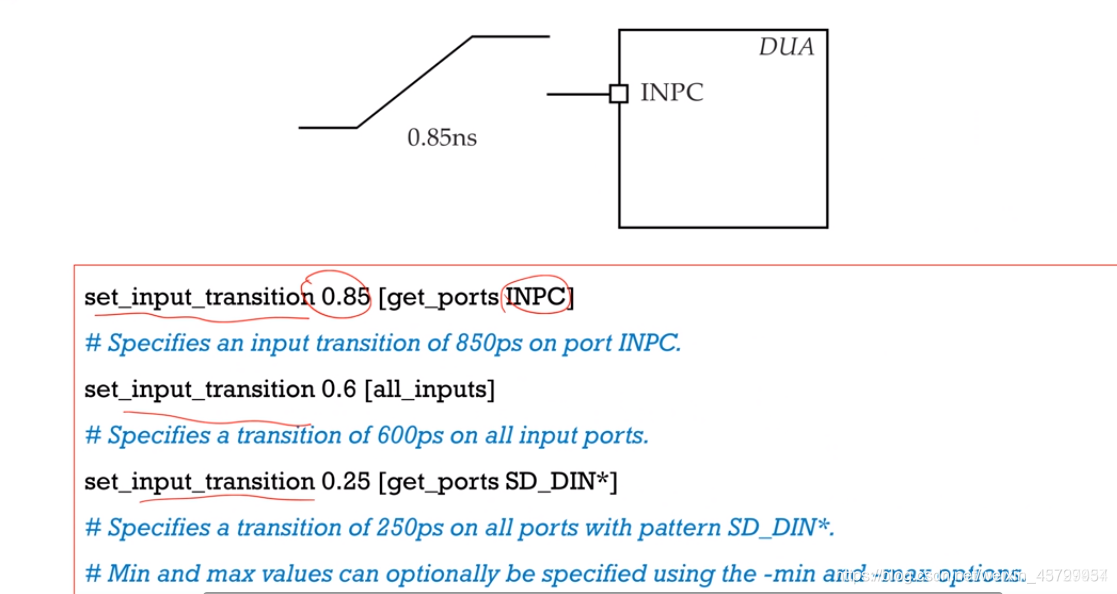

对于input这些属性主要包括:

set_drive

set_driving_cell

set_input_transition -

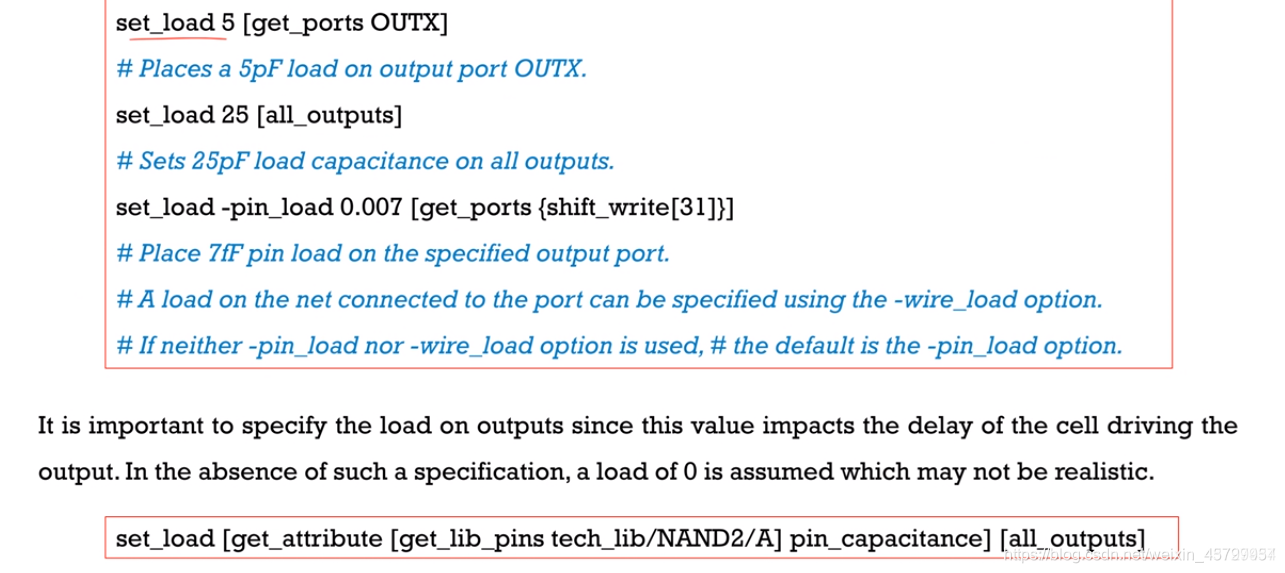

对于output要指定以下属性:

set_load

- 通过库参数设置

- output 的负载默认是0(理想)

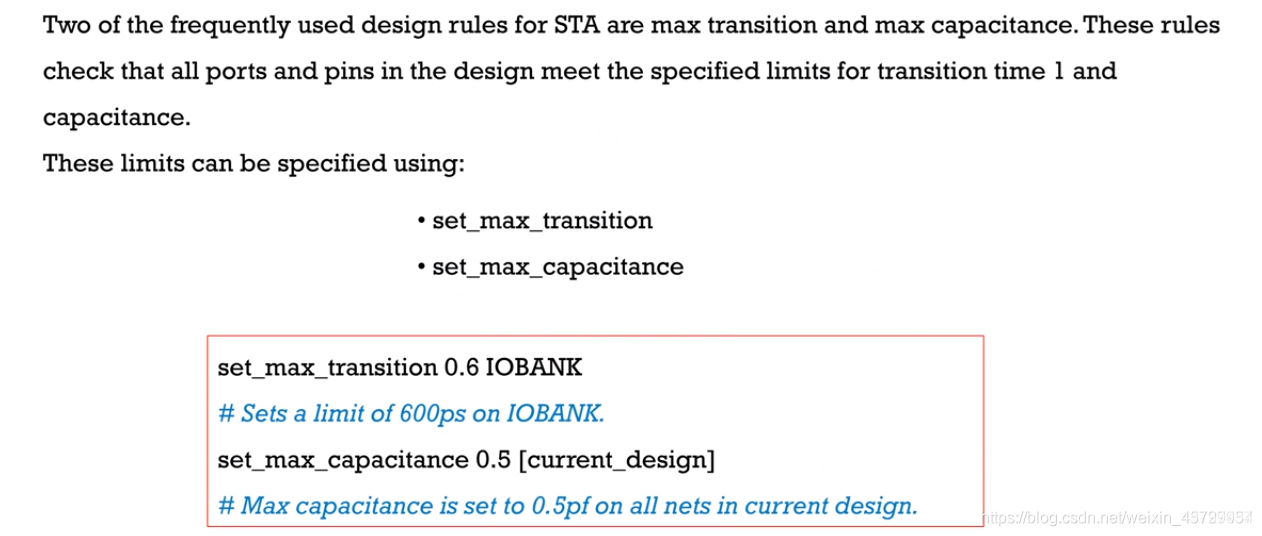

3. DRC

- set_max_transition

- -set_max_capacitance

- set_max_fanout

- set_max_area

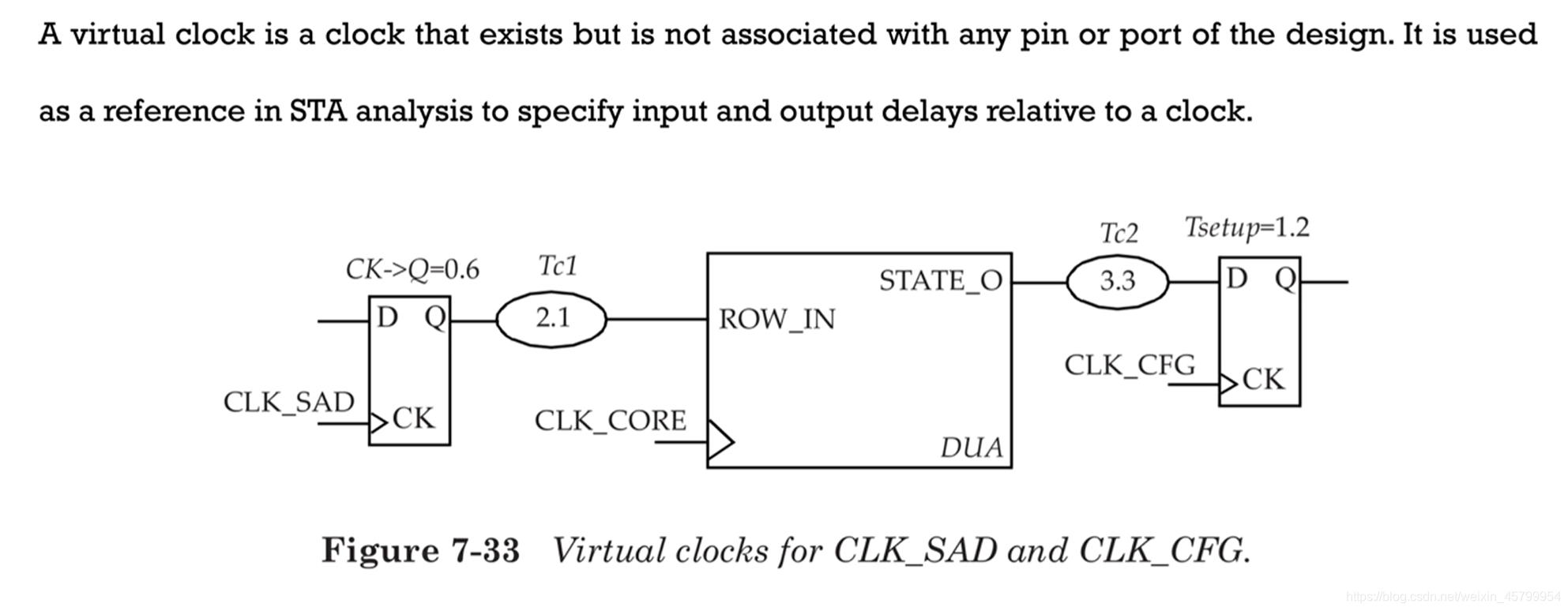

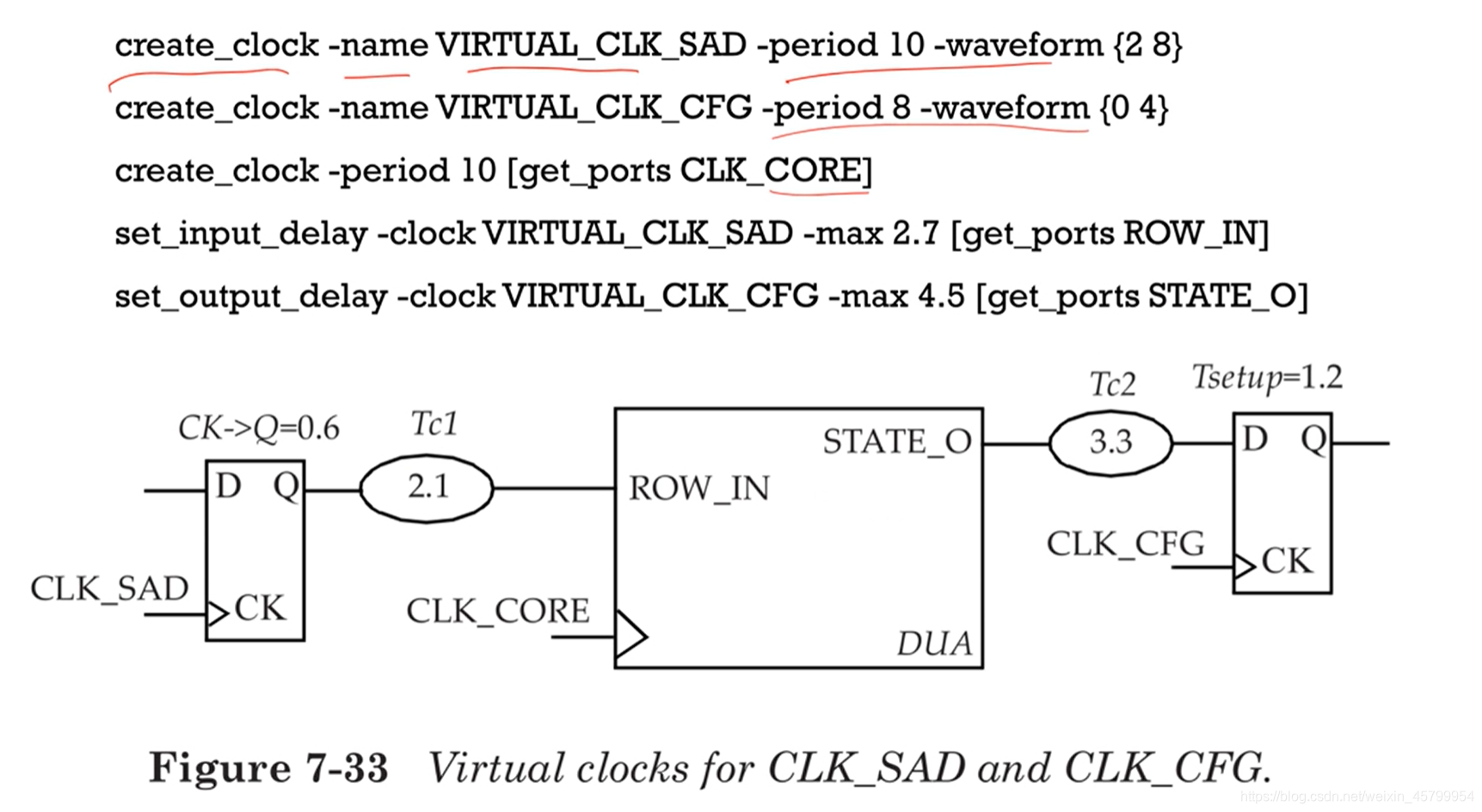

4. Virtual clock

- 指定input或output相关的一个时钟

- 定义 :不需要指定管脚

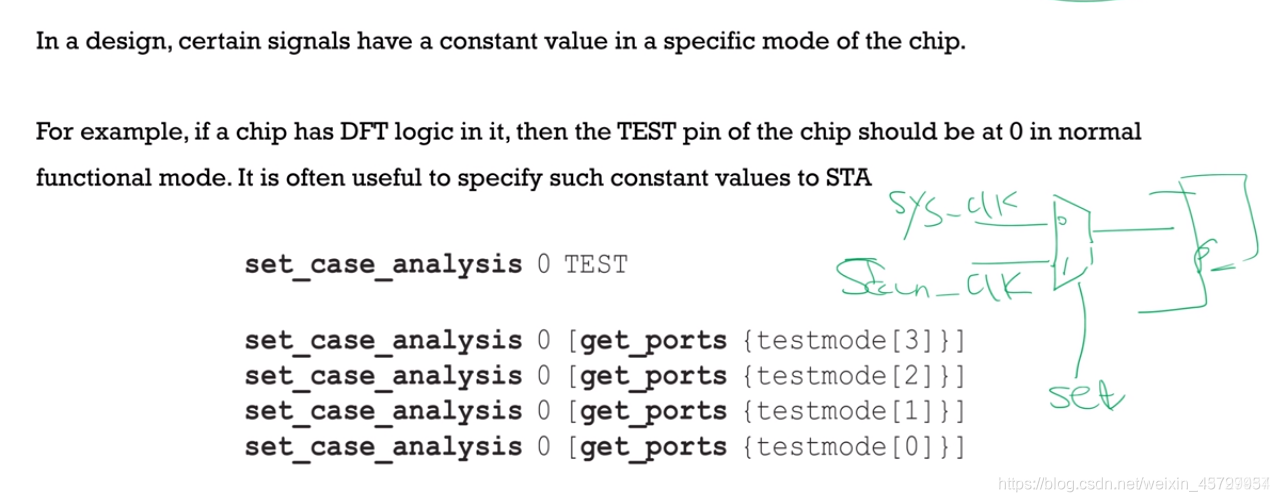

5. Refining the Timing Analysis

让静态时序变得更精细化

-

set_case_analysis

在静态时序分析过程不分析DFT的TEST时钟相关

-

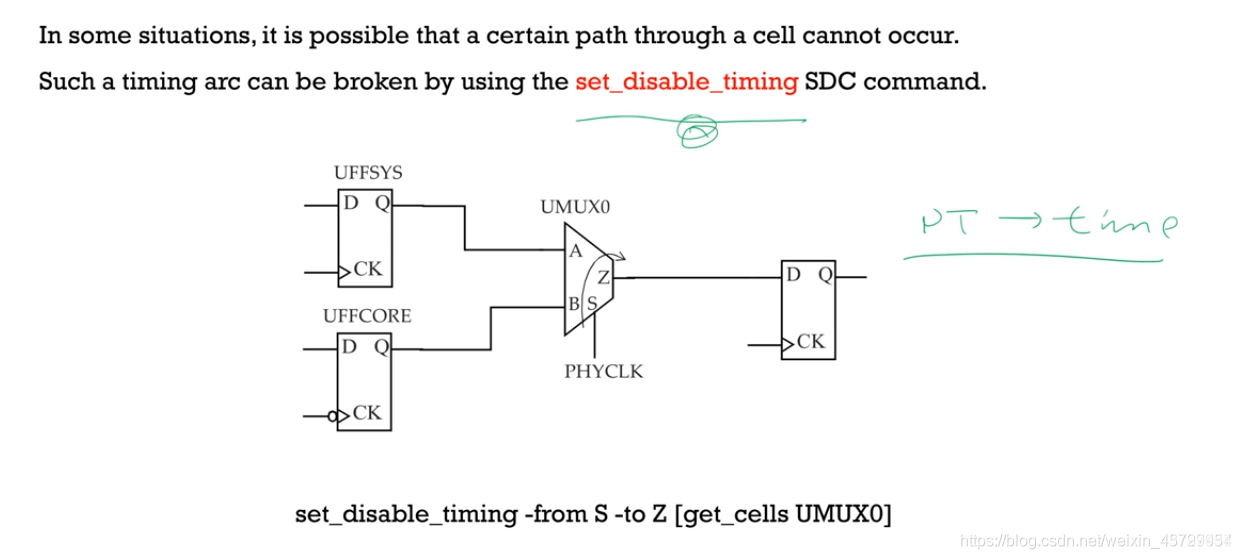

set_disable_timing

设置不分析非时序路径

-

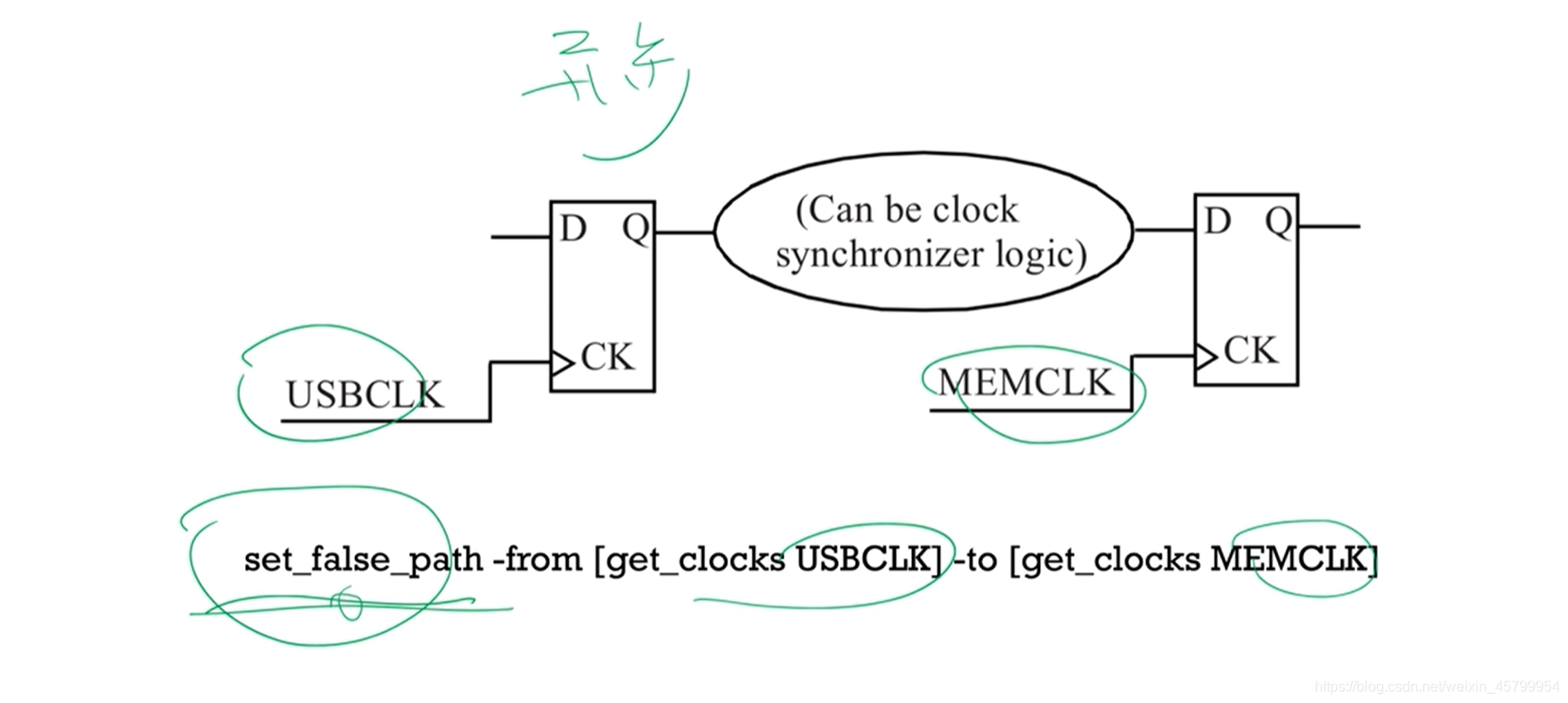

set_false_path

伪时序路径:如跨时钟域

-

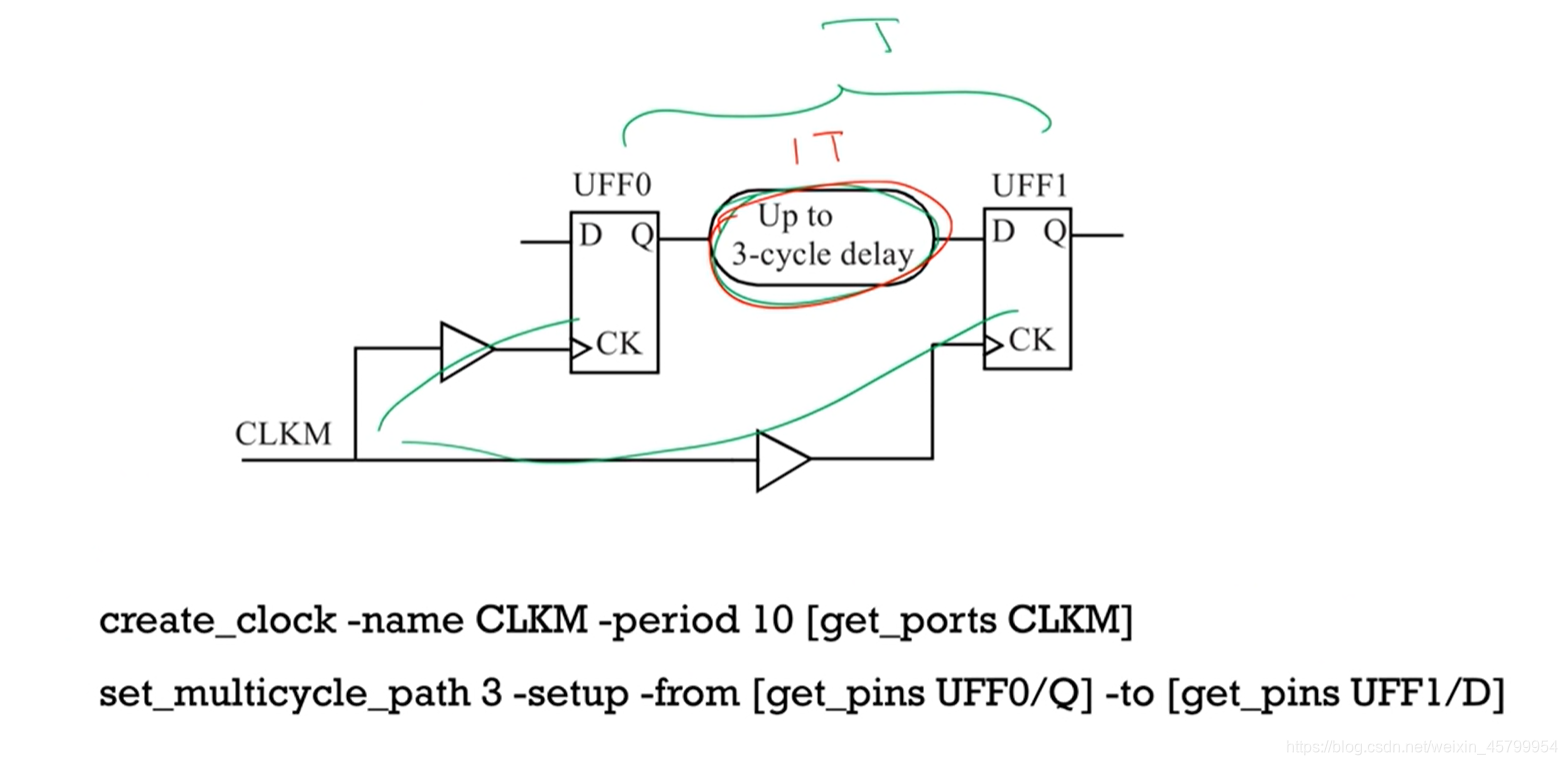

set_multicycle_path

设置多周期约束,前端人员指定

1120

1120

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?