System Verilog语法基础要点

文章目录

一、Wire, reg, logic, int, parameter, localparam

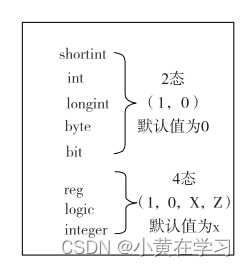

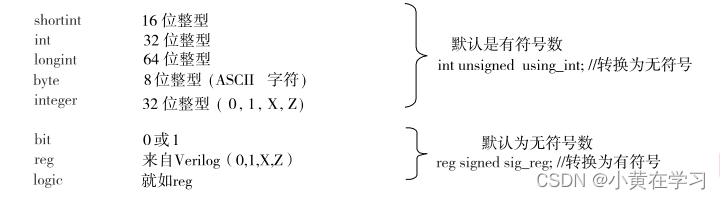

1. Wire, reg, logic

- logic是sv对reg类型的改进,其不仅作为一个变量起作用(reg),还可以被连续赋值、门和module驱动(wire),这使得sv不需要再对reg和wire进行区分。

- 但logic不能被多个信号驱动,例如inout类型的信号,则需要定义成wire。

- logic是四态数据类型。

2. int

3. parameter, localparam

- localparam 与 parameter 相同,只是它们不能通过defparam语句或例化直接修改。

- localparam 可以用 parameter 来表示,从而达到用defparam或者例化修改parameter的值进而修改 localparam 的目的。

二、 Struct, packed struct, array, packed array

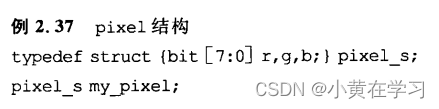

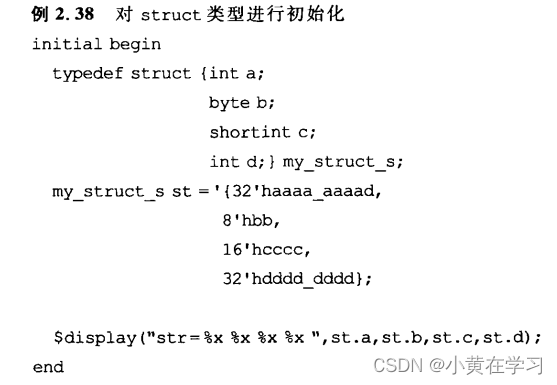

1. Struct, packed struct

- verilog中并没有struct的说法,但struct的功能较少:class可以同时包含数据和代码,而struct本身只是数据的集合(是可综合的)。

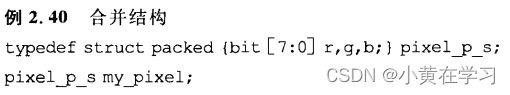

- sv提供了packed struct合并结构体,允许struct可以连续地在存储器内存放。

应用场景 :1.减少储存器使用量 2.存储器的部分bit代表了某些特殊含义(比如处理器的inst opcode)

- 如果经常要对整个struct进行操作, 使用packed struct的效率会更高;如果操作经常针对struct内的成员,那么应该使用unpacked的struct。

对于packed struct内尺寸不规则成员读写的代价颇高

2. array, packed array

- sv引入了一种新的定宽数组声明方式,可以在变量名之后给出其维度来创建新array。

下面两种声明方式是一样的int array1[8][4];

int array2 [0:7][0:3]; - 如果array地址读取越界,那么读出来的结果会是该信号类型的缺省值。对于四状态数组,读出来是X;对于双状态数组,读出来的结果是0。

- 数组的初始化:单引号加大括号

int array1 [4]='{0,1,2,3};

- 批量初始化

array2='{4{8}};

array3='{9,8,default:1}; - 在sv中,允许数组下标和位下标混用

array[0][2:1]

- packed array允许一个数组有时候被看成一个整体,有时候可以被看成是多个单独数据的组合。其存放时是连续的bit集合。(packed和unpacked array可以混用)

packed声明就是多维尺寸放在变量前面写

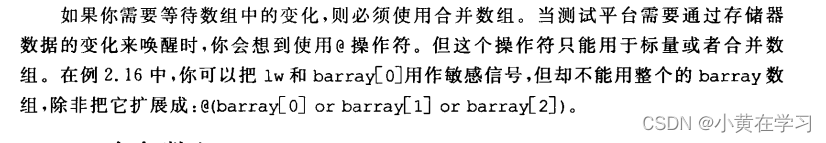

- packed array适合经常对数组中某部分进行操作的情景。此外,如果要把数组作为@中的敏感信号,那么就需要用packed array。

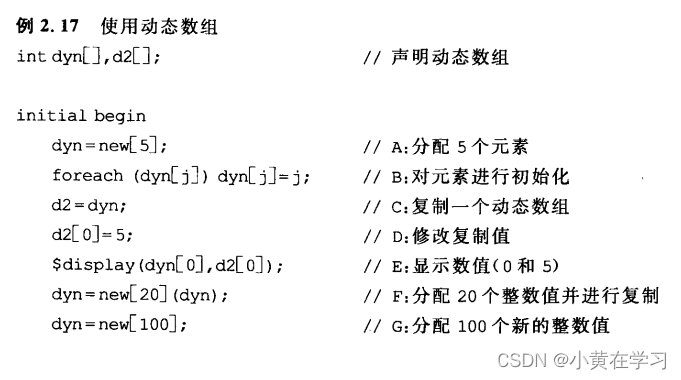

- 对于某些刚开始不知道其大小的数组,我们可以先不声明其尺寸,用空下标定义,后面再利用new[]数组指定。

三、Always, always_comb, always_ff

1. Always

- sv保留了always语句,并且在循环中增加了 continue 和 break 的语法

- 可以省略使用begin…end块了,还可以用:之后的增加变量名给begin…end块命名

2. always_comb, always_ff

- sv中对always关键词进行细化了,always_comb专门用于组合逻辑,综合工具会判断always_comb块内是否是组合逻辑,以防不小心生成latch。在使用时需要注意always_comb内只能使用阻塞赋值=。

- 针对要使用latch的情况,sv提供了关键词always_latch,在使用时不需要敏感信号列表。

- 对于要使用ff的情况, 可以使用关键词always_ff。使用时需要敏感型号列表,信号前需要注意备注是否是正/负边沿触发。在使用时需要注意always_ff内只能使用非阻塞赋值<=。

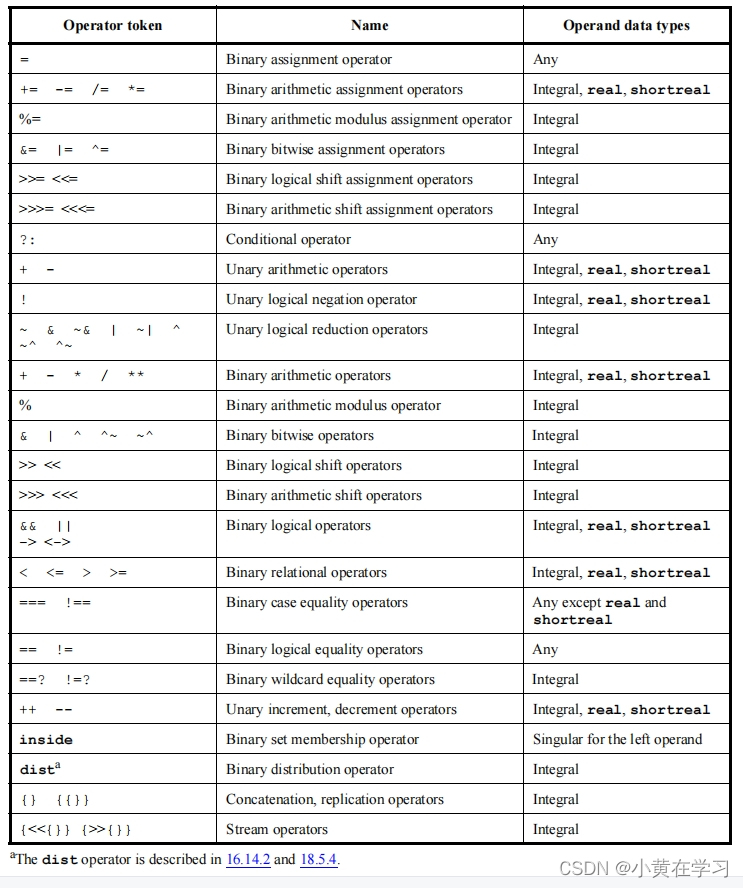

四、运算符

五、If else, case, for

1. If else

- 在always块里面使用

if() … else …

允许嵌套,嵌套用的也是 if() … else …

允许没有else的情况出现,如果这样,那么被赋值的信号就会保持原值,相当于产生了一个latch

2.case

- https://blog.csdn.net/jk_101/article/details/127682098

3. for, foreach

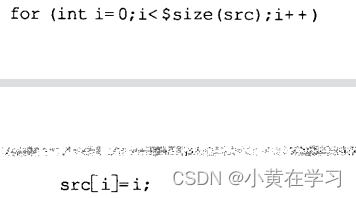

- for的用法

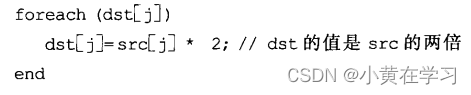

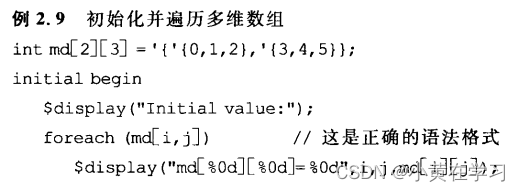

- foreach的用法

如果是多维数组,其索引变量用逗号隔开。如果要进行嵌套的foreach,在第二次遍历时,括号内变量要写成[,j]

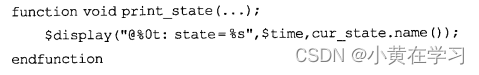

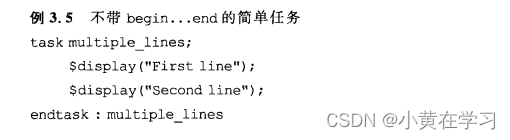

六、Task, function

- task可以消耗时间,但是func不行:func不可以带有#延时或者阻塞语句,func若要调用task需要在fork join_none语句中

系统自带函数

- $bits 占据的bit位数

- $clog2 求底数为2的log值,可用于求地址

- $error 输出自定义的错误信息,暂停仿真

- $warning 输出自定义的错误信息,不暂停仿真

- $info 输出自定义的错误信息,不暂停仿真

- $display https://zhuanlan.zhihu.com/p/72085819

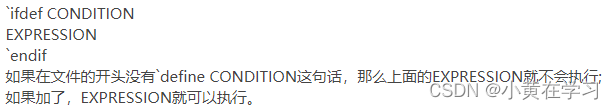

七、宏的使用

-

`define

-

`ifdef

可以跟宏 elsif 一起用

-

`ifndef

跟 ifdef差不多,就是if not的意思 -

`else

跟ifdef一起用的,如果没有定义宏,那么就执行else内的 -

`endif

-

`include

插入一个.v的文件进来

八、Package,Generate

1. package

https://blog.csdn.net/Hision_fpgaer/article/details/50909653

2. generate

https://zhuanlan.zhihu.com/p/107047600

本文详细介绍了SystemVerilog的基础语法要点,包括Wire、reg、logic等数据类型的差异与应用,struct和packedstruct的使用场景,always_comb和always_ff的时序逻辑控制,以及运算符、条件语句、循环语句的使用。此外,还提到了task和function的异同,宏定义的使用,以及package和generate的概念。

本文详细介绍了SystemVerilog的基础语法要点,包括Wire、reg、logic等数据类型的差异与应用,struct和packedstruct的使用场景,always_comb和always_ff的时序逻辑控制,以及运算符、条件语句、循环语句的使用。此外,还提到了task和function的异同,宏定义的使用,以及package和generate的概念。

1333

1333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?