文章目录

1. 计算机系统

-

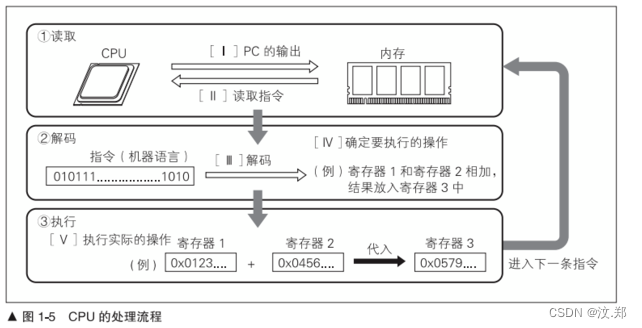

CPU(Central Processing Unit):计算机中进行各种运算和数据处理的装置;根据指令进行各种处理的电子电路;主要进行的是指令读取-指令解码-指令执行;

-

指令集根据特征可分为RISC(Reduced Instruction Set Computer,精简指令集)指令和CISC(Complex Instruction Set Computer ,复杂指令集);RISC指令比较简单,种类少。CISC指令复杂,种类多;要进行同一操作的话,用RISC需要更多的指令,但单个指令会更快;用CISC需要较少指令,单指令需要更多的时间;

-

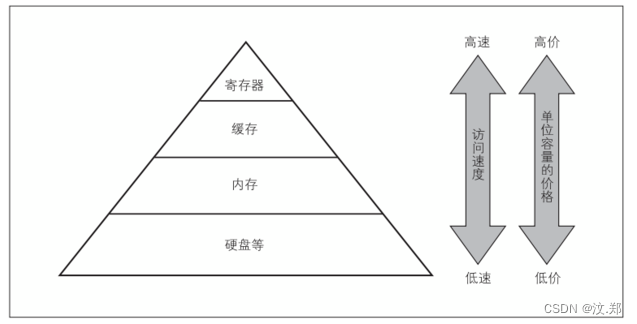

内存是用来存放运行时指令和数据的存储器;越接近CPU的内存进行的访问速度越快,代价越大;

-

总线是CPU、内存和I/O之间进行数据交换的通道;发起操作的一方称master,被操作的一方为slave;

-

多个master的总线时,master需要进行总线使用时步骤为:

- 申请使用总线;

- 仲裁器许可使用总线;

- 发送请求;

- 请求应答;

- 释放总线控制权;

-

总线的优点为只要遵循总线协议,任何设备都可以简单的进行连接,并且使用共享通道,降低硬件设计成本;但相应的问题是由于总线共享,导致了数据传输较慢,需要进行仲裁等操作,总线的数据吞吐量较低;

2.数字电路基础

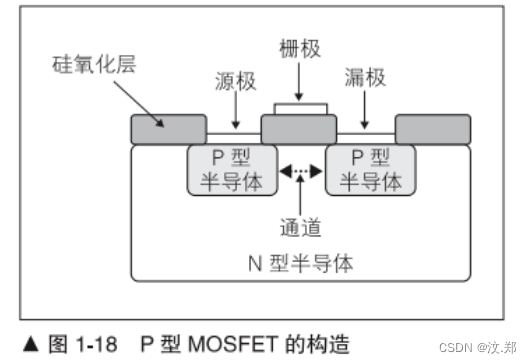

- MOSFET结构;

-

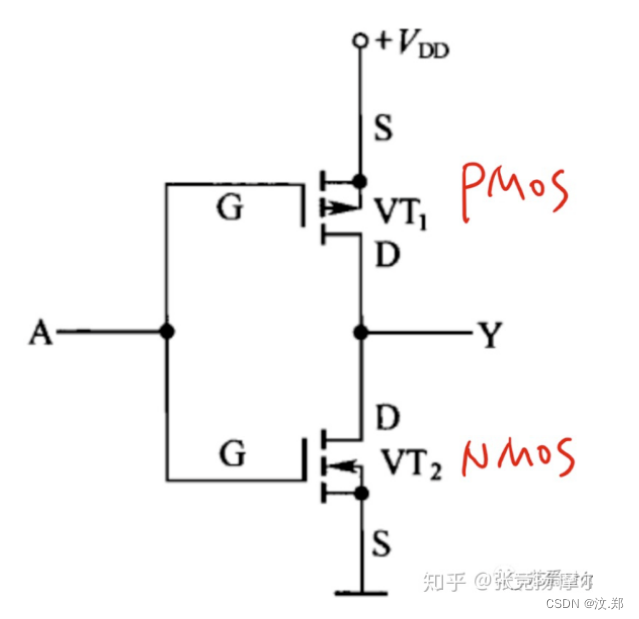

PMOS:该MOS管图如下,工作模式参考NMOS,但需要注意此时栅极需要用做负极;

-

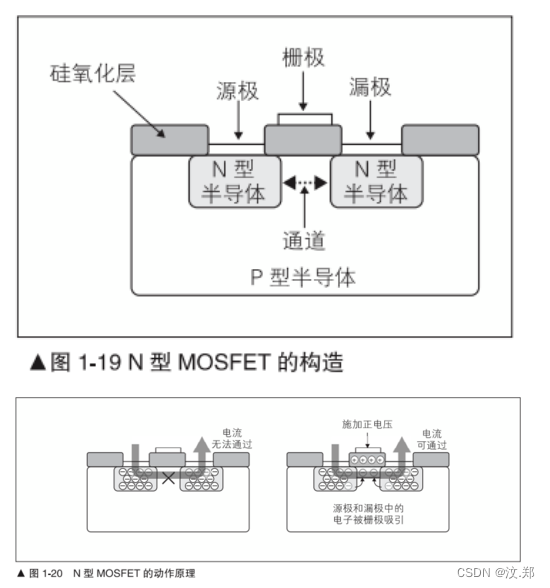

NMOS:

在不给栅极施加电压时,源极和漏极之间充满了异种半导体,因此电流无法流过。当给栅极施加正电压后,栅极处堆积大量电子,使得源极和漏极之间的电子连通,此时电子就可以通过源极流向漏极,产生电流;

-

CMOS:CMOS由PMOS和NMOSZ组合而得,如下;

-

3.Verilog HDL语言

-

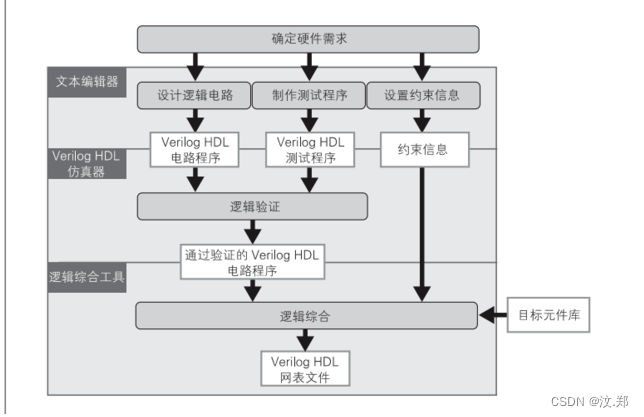

设计流程:确定硬件需求→编写verilog代码、设定面积,时钟周期约束等→功能验证等→逻辑综合、生成网表

-

数据类型有寄存器类型(reg)和线网类型(wire);reg型变量会保存上次写入的数据;wire类型变量用以连接各模块,其实也就是将reg连接起来;在不声明时默认为wire类型;

-

阻塞赋值、非阻塞赋值;

-

注意将组合逻辑中的if条件、case情况写完整,避免生成不必要的锁存器;

-

timescale 用来设定仿真执行的单位时间和时间精度;例:timescale 1ns/1ps 时间单位1ns,时间精度1ps;仿真时时间精度没必要设置太小,可以减少仿真时间;

4.系统蓝图

-

避免使用魔术数字(Magic number,嵌入代码中的常数),而使用更多的宏,可增加代码的可移植;

-

驼峰拼写法(UpperCamelCase),多个单词组合,每个单词首字母大写;软件使用该法,硬件一般使用加“_”隔开;

-

多个master以及多个slave总线中,对slave的选择信号一般都是根据master送出的地址信号进行判断;也就是说每个slave是有自己的地址空间,每个slave之间的地址空间相互独立,不重叠;

-

流水线的冒险,资源冒险。数据冒险。控制冒险。

-

CPU模式;

- 内核模式(管理者模式):全部指令可以无限制的执行;

- 用户模式:指令执行受到限制;

-

中断和异常;

- 中断是指让CPU暂停正在执行的操作,执行处理该中断;中断完成处理后返回中断处继续执行;

- 异常是指CPU的执行产生了预期之外的结果(如指令无法解码、运算结果溢出、操作违反权限等);

异常和中断的区别是:中断是有CPU外部引起不是CPU内部的问题。是由外部来通知CPU需要停止手头上的事执行相关的处理,处理完后回到中断处继续执行,是一种正常的流程;而异常则是一种不符合预期的情况,异常处理完成后可能会回到异常处继续执行,也有可能直接强制中止,这是一种不正常的操作;

- 中断的产生有mask、en、force_int、int_raw_rpt、int_rpt;

5.I/O的设计与实现

-

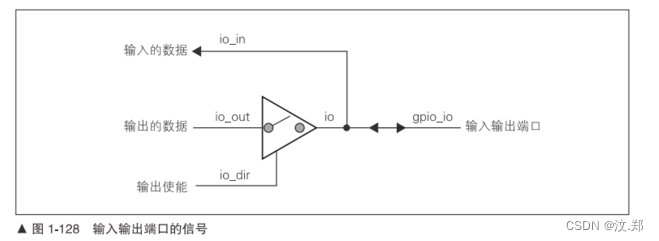

gpio_io类型的示意图;

-

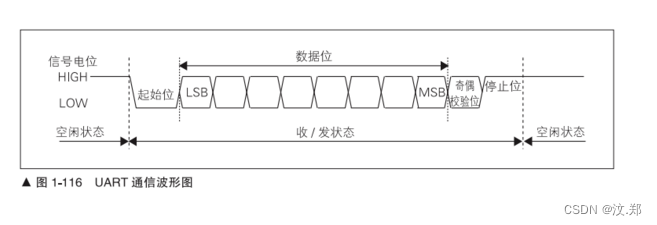

UART的基本协议;是起止式同步接收,发送串口通信装置;协议具体内容需要专门找时间看下;

6. SPI、I2C、UART、CAN总线简介

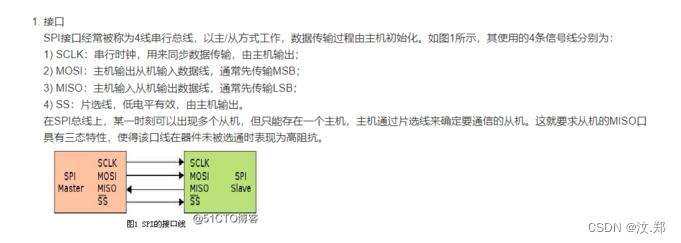

1.SPI总线

SPI总线由4个接口组成;

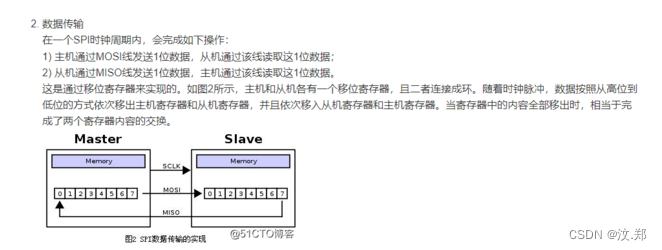

2. 数据传输是将master与slave之间的寄存器通过移位方式进行传输;

- 优缺点

- 优点;

- 支持全双工操作;

- 操作简单;

- 数据传输效率高;

- 缺点;

- 需要占用主机较多的口线(每个从机都需要一根片选线);

- 只支持单个主机;

2. I2C

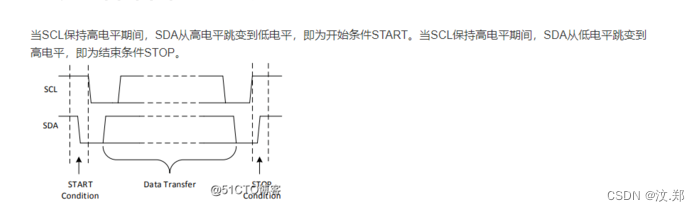

I2C接口由时钟线(SCL)和数据线(SDA)组成;

-

主机给从机发数据

- 发送开始条件,和从机地址;

- 发送数据

- 发送结束条件;

-

主机从从机读取数据;

- 发送开始条件,和从机地址;

- 发送要读取的地址;

- 读取数据;

- 发送停止条件;

-

开始结束条件如下:

-

优缺点:

-

优点;

- 只使用两条信号线;

- 支持多主机多从机;

-

缺点;

- 速率较慢;

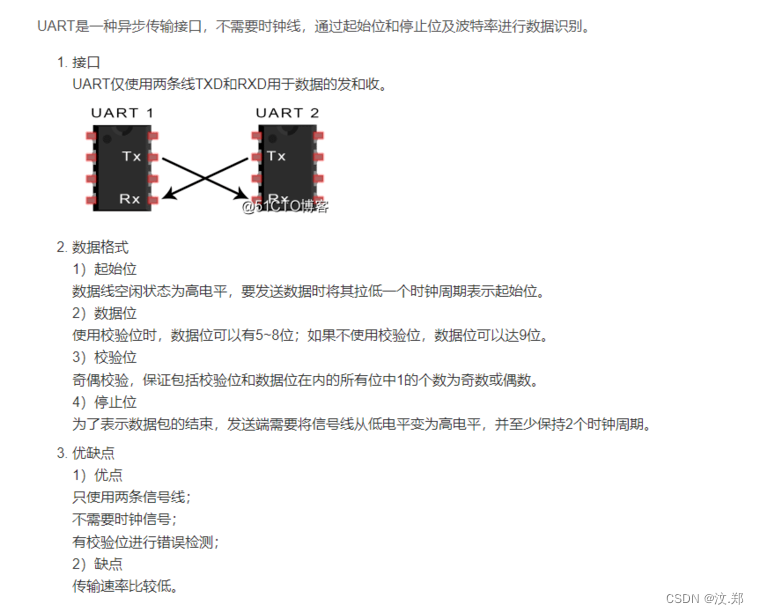

3.UART

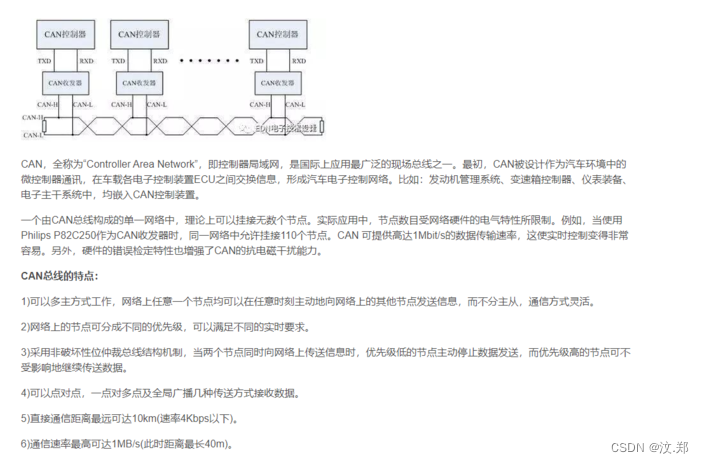

4.CAN

5. 对比

2786

2786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?